电平专题

外部中断的边缘触发和电平触发

MCS-51单片机中的边缘触发是指当输入引脚电平由高到低发生跳变时,才引起中断。而电平触发是指只要外部引脚为低电平就引起中断。 在电平触发方式下,当外部引脚的低电平在中断服务返回前没有被拉高时(即撤除中断请求状态),会引起反复的不需要的中断,造成程序执行的错误。这类中断方式下,需要在中断服务程序中设置指令,清除外部中断的低电平状态,使之变为高电平。

开漏输出和推挽输出区别TTL电平和CMOS电平的区别

目录 开漏输出和推挽输出区别 参考附件: 正文: TTL电平和CMOS电平的区别 参考附件: 1.TTL电平: 2.CMOS电平: 3.电平转换电路: 开漏输出和推挽输出区别 参考附件: 开漏输出、推挽输出的区别_开漏输出和推挽输出区别-CSDN博客 正文: 推挽输出和开漏输出的主要区别体现在电路结构、工作原理以及应用场景上。 推挽输出由两个晶体管构成,一个N

逻辑器件输出高阻态时,输出端口的电平是什么状态呢?

高阻态是逻辑器件输出端口的一种状态,当端口处于高阻态时,输入端口的电平变化不会引起输出端口变化,不会对与之相连的后级输入端口或总线产生影响,对于总线架构的电路极为重要。 输出端口处于高阻态时,输出端口处于一种随机状态,电平可能处于任意位置,此时有微弱的输入或输出电流,通常为几个微安左右。重点是高阻态时,对后级连接的负载无驱动能力,而与电平状态无关。

STM32通过ADM3222完成UART转232通信电平转换

1、简介 单片机默认串口输出电平是UART信号,但是在实际项目中经常需要将其转换成232电平,此时就需要ADM3222芯片来完成电平的转换,下面对使用过程进行总结。 2、硬件电路 从上图中可以看到芯片需要对1、18进行配置才能进行工作,通过查阅手册可知,1引脚需要配置低电平,18引脚需要配置成高电平,芯片才能工作。 通过该芯片支持两路信号转换,本次通过串口1进行测试,单片机的串口1接

双通道SP3232芯片实现由TTL电平转RS232电平

首先,单片机的串口必须经过电平转换才可以和标准RS-232通信,这个转换芯片5V的一般是MAX232或SP232,3.3V的一般是MAX3232或SP3232。 严格说,SP有3232和SP232两种,前者宽电,后者只支持5V。 SP3232是一款RS-232接口收发器芯片,其主要功能是串行转并行和并行转串行数据的转换。SP3232的引脚如下: 插一段,SP3232和SP3222的区别: 在

TTL电平和CMOS电平的区别

区别具体如下: (一)TTL高电平3.6~5V,低电平0V~2.4V。 CMOS电平Vcc可达到12V。 CMOS电路输出高电平约为0.9Vcc,而输出低电平约为0.1Vcc。 CMOS电路不使用的输入端不能悬空,会造成逻辑混乱。 TTL电路不使用的输入端悬空为高电平。 另外,CMOS集成电路电源电压可以在较大范围内变化,因而

epoll下电平触发LT和边沿触发ET的区别

LT 电平触发 高电平触发 EPOLLIN 事件 数据可读 内核中的socket接收缓冲区 为空 低电平 不会触发 内核中的socket接收缓冲区 不为空 高电平 会触发 EPOLLOUT事件 数据可写 内核中的socket发送缓冲区不满 高电平 内核中的socket发送缓冲区 满 低电平 ET 边沿触发 转换的时候触发

AiP74LVC1T45GB236.TR SOT23-6缓冲器/驱动器双电源接口电平转换

AIP74LVC1T45GB236.TR 是一款电平转换芯片,它的应用领域非常广泛,主要包括: 1. 嵌入式系统:在嵌入式系统中,由于不同的外设可能工作在不同的电源电压下,该电平转换器可用于确保微控制器和其他逻辑电路之间的信号传输正确无误。 2. 汽车电子:汽车电子系统经常需要处理来自不同电源域的信号,AIP74LVC1T45GB236.TR 可用于汽车电子设备中以保证稳定的数据通信。

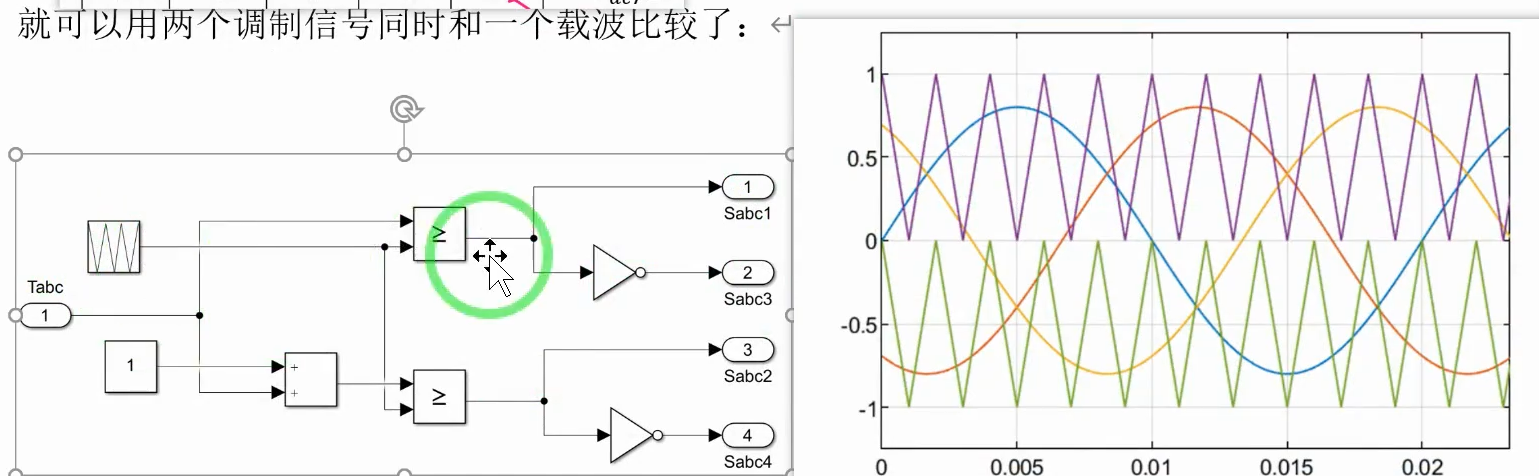

SPWM载波调制方式-三电平杂记1

方法一: P=2 O=1 N=0 方法二:双载波直接发波 方法三:负轴载波和调制波往上抬升1,得到使用同一个载波 在正半周在P和O切换,在下半轴式O和N切换

Xilinx FPGA 管脚的默认电平配置方法 XDC约束

目录 未使用的引脚,XDC约束其他已使用的引脚,XDC约束 未使用的引脚,XDC约束 set_property BITSTREAM.CONFIG.UNUSEDPIN PULLDOWN [current_design]set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]set_property BITST

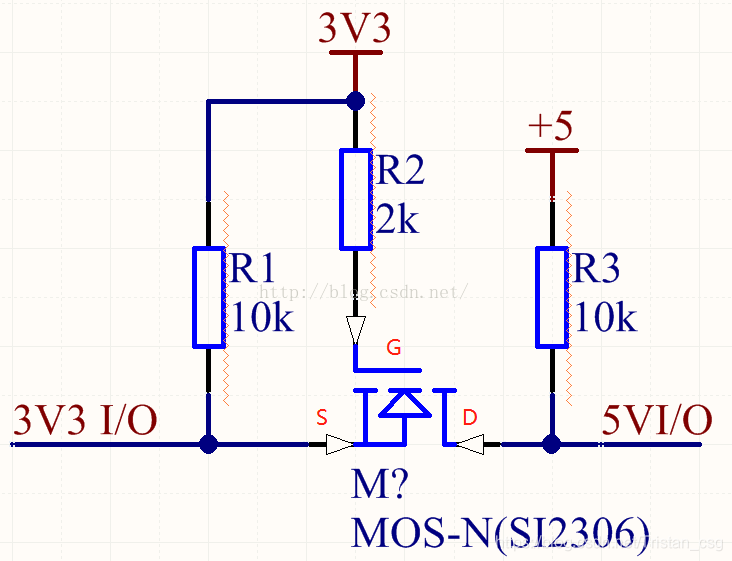

3.3与5V 电平转换

1.简介 现在大多数的MCU基本都是3.3V供电,而外围器件依旧存在一些5V供电的,两者之间的通信不可避免的需要电平之间的转换。 2.电路设计 这里介绍一个可以实现两个电平的相互转换的电路,网上相关的介绍也很多,近期的一个项目设计刚好用的,特此记录一下。 TR1、TR2为分立的 NMOS 三极管,S为源极,D为漏极,G为栅极。Rp为上拉电阻,一个连接在S与VDD1之间;另一个连接D与V

一种解决按键开关电平毛刺问题的算法

一种解决按键开关电平毛刺问题的算法 /* * 通过检测按键开关的相应管脚电平状态来判断按键是否按下, * 按键未按下时,对应管脚电平的为高,按下之后对应管脚电平变为低电平, * 松开之后,回复高电平,通过电平变化的上升延来判断按键被按下 * 具体算法:主循环每轮进行一次电平采样,每次采样值保存在1Byte的最低位bit中 * (0:低电平,1:高电平),保存之前左移一位,确保保存

在BootLoader中使用gpio--获取gpio的高低电平,以及设置相应的管脚的电平高低

以下以rv1108平台为例: 在项目中,需要实现一个功能,在Linux kernel加载前BootLoader判断一个引脚电平的高低状态,从而决定加载不同的kernel,以及相应的文件系统,以实现双系统的功能。 //判断按键的电平高点状态:#if 1//set gpio3_a4's direction intputu32Reg = read_XDATA32(0x10330000 + 0x00

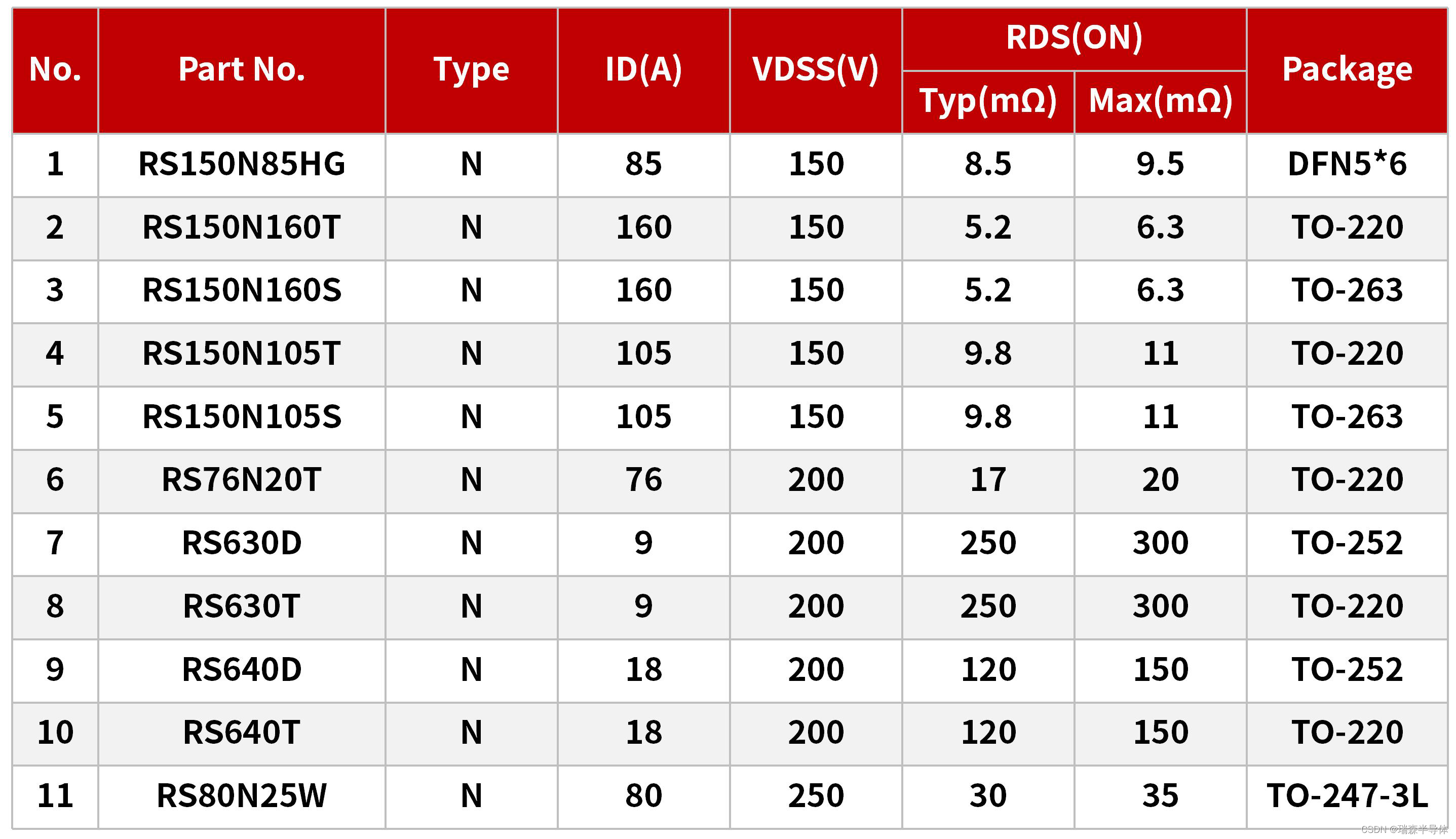

低压MOS在多电平逆变器上的应用-REASUNOS瑞森半导体

一、前言 多电平逆变器,是一种新型逆变器。常规逆变器,在单桥臂上采用单个开关器件。多电平逆变器在单桥臂上包含多个串联开关器件,能够精细地控制输出电压。将逆变输出的正弦波进行微分,微分数量越多,越接近正弦波。常见的多电平逆变器有三、五、七电平等。其功率开关元件工作在较低的频率上,使功率元件的开关损耗减小,产生的电磁干扰较小,逆变器效率更高。缺点是需要用到更多数量的功率开关元件,对驱动调制以及测试验

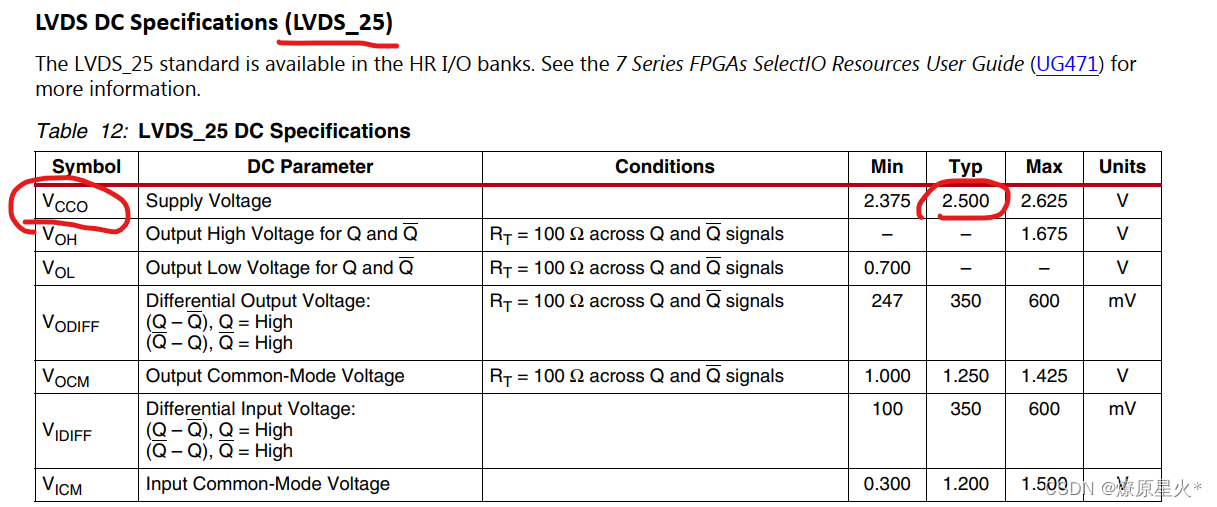

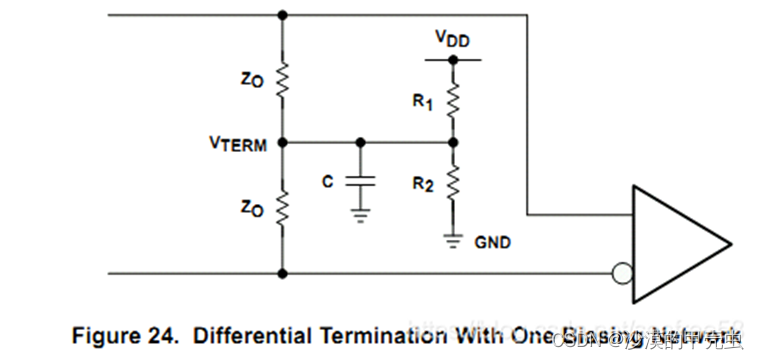

ECL、LVDS和CML电平

芯片间互连通常有三种接口:PECL(Positive Emitter-Coupled Logic)、LVDS(Low-Voltage Differential Signals)、CML(Current Mode Logic)。 各接口电平规范 ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。以上三种均为射随输出结构,必须有电阻

DDR3的DQS_p/n信号电平摆幅变化不一致现象

环境: zynq7100, MT41J64M16 现象: (1) 处理器读DDR3的操作,DQS_p/n信号与DQn信号一道,由DDR3发出,处理器接收。 测量发现,DQS信号电平摆幅低低高高的现象,摆幅高时能达到正常摆幅要求,低时只是正常摆幅的一半左右。 (2) 处理器写DDR3的操作,DQS_p/n与DQn一道,由处理器发出,DDR3接收。 测量信号正常,DQS信号差分摆幅一

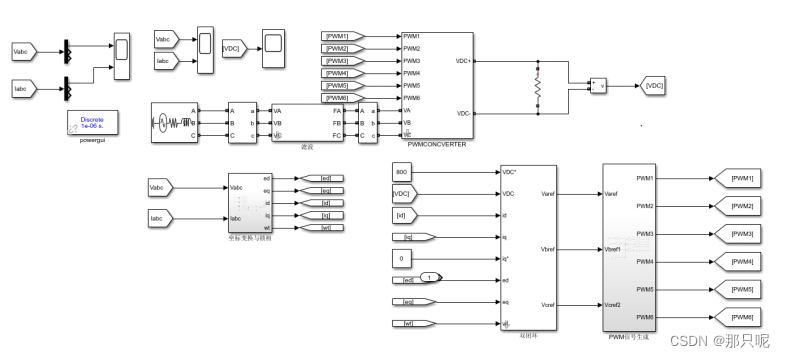

一份报告实现两电平逆变、三电平逆变、三相整流、光伏并网simulink仿真

一份报告实现两电平逆变、三电平逆变、三相整流、光伏并网simulink仿真。逆变、整流与光伏的全家桶系列,适合小白使用。 模型获取链接:一份报告实现两电平逆变、三电平逆变、三相整流、光伏并网simulink仿真

硬件知识:N-MOS管 双向电平转换电路

如上图所示,是 MOS-N 场效应管 双向电平转换电路。 双向传输原理: 为了方便讲述,定义 3.3V 为 A 端,5.0V 为 B 端。 A端输出低电平时(0V) ,MOS管导通,B端输出是低电平(0V) A端输出高电平时(3.3V),MOS管截至,B端输出是高电平(5V) A端输出高阻时(OC) ,MOS管截至,B端输出是高电平(5V) B端输出低电平时(0V

嵌入式单片机 TTL电平、232电平、485电平的区别和联系

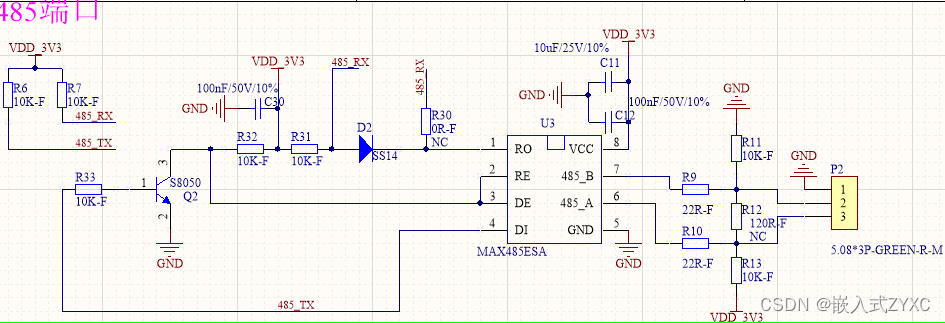

一、简介 TTL、232和485是常见的串口通信标准,它们在电平和通信方式上有所不同, ①一般情况下TTL电平应用于单片机外设,属于MCU/CPU等片外外设; ②232/485电平应用于产品整体对外的接口,一般是片外TTL串口转232/485,232/485进行数据通信传输; 二、案例 1、TTL电平 (1)TTL(Transistor-Transistor Logic)电平是一种低电

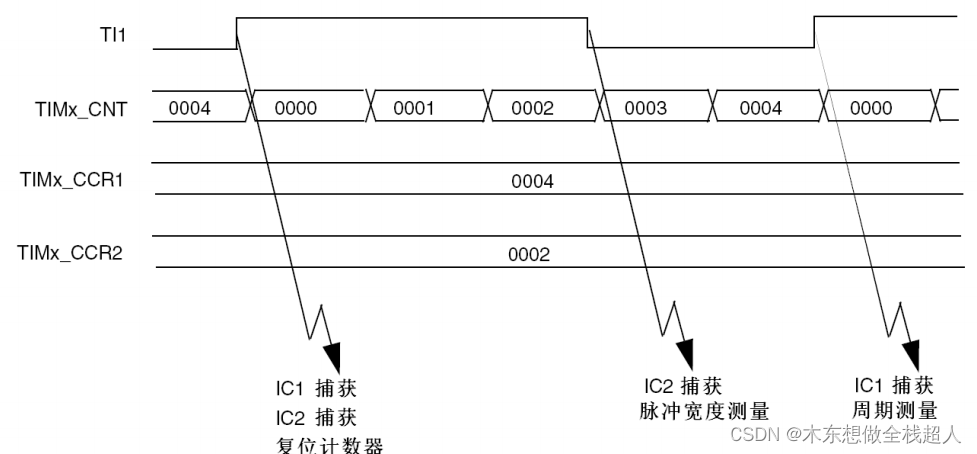

电平输入检测-定时器输入捕获

目录 一,引入 二,具体结构 三,实现步骤 四,PWM输入模式 一,引入 上篇博客,我们对于定时器的计数核心——时基单元作了细致的了解。这篇博文,我们来介绍定时器的四大功能模块之一——输入捕获模块。 输入捕获模块,顾名思义,当外界有电平输入MCU时,定时器的输入捕获模块能够捕获到电平,进而通过时基单元(计数器),记录捕获的电平的时间、占空比等数

多路NPN信号转TTL电平/PNP/TTL电平转0-24V电平

特点: ● 8路NPN信号转PNP信号高速转换 ● 8路0-5V电平转0-24V电平 ● 8路TTL电平转0-24V电平 ● 8路NPN信号转TTL电平 ● 8路0-24V电平转0-5V电平 ● 支持输入信号和输出信号电平翻转。 ● 电平转换速度可达1MHz ● 信号输入 / 输出之间隔离耐压3000VDC ● 宽电源供电范围:8 ~ 32VDC ● 标准DIN35导轨安装,方便集中布线 典型应

NTB0101GS1Z 电压电平 移位器 产品概述 特性

NTB0101是一个1位双电源转换收发器,具有自动方向传感功能,可实现双向电压电平转换。它具有两个1位输入输出端口(A和B),一个输出使能输入(OE)和两个供应引脚(VCC(A)和VCC(B))。VCC(A)可以在1.2 V到3.6 V之间的任何电压下供电,VCC(B)可以在1.65 V到5.5 V之间的任何电压下供电,使该设备适合在任何低压节点(1.2 V, 1.5 V, 1.8 V, 2.5

差分逻辑电平 — LVDS、CML、LVPECL、HCSL互连

前言 首先了解差分逻辑电平、单端逻辑电平的基础知识 地址:常见的逻辑电平_常用的逻辑电平-CSDN博客 注: ECL >> PECL >> LVPECL演变; ECL速度快,驱动能力强,噪声小,但是功耗大,使用中需要负电源。为了简化电源,出现了PECL和LVPECL的输出模式。PECL电路速度快,驱动能力小,噪声小,高频。高功耗是PECL输出的主要缺点,且不同电平不能驱动

基于rk3568解决gpio阶梯波形(适用于i2c、uart、电平转换)

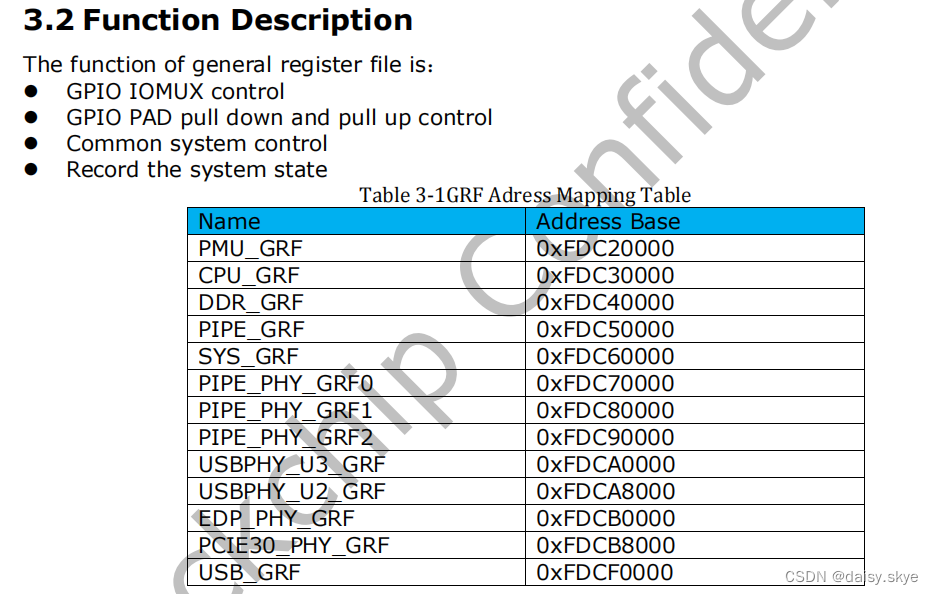

目录 1、理解GPIO的开漏(OD)和开集(OC) 2、查询io寄存器地址及定义 3、配置可调寄存器接口dev/mem author daisy.skye的博客_CSDN博客-嵌入式,Qt,Linux领域博主 daisy.skye_嵌入式,Linux,Qt-CSDN博客daisy.skye擅长嵌入式,Linux,Qt,等方面的知识https://blog.csdn.net/qq_4071526