卷积码专题

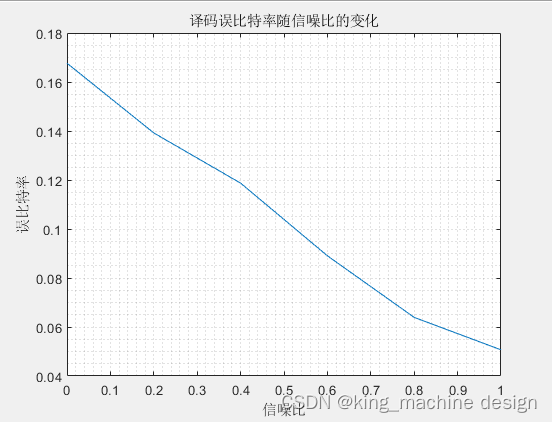

基于MATLAB仿真的BCC卷积码维特比译码算法

🧑🏻个人简介:具有3年工作经验,擅长通信算法的MATLAB仿真和FPGA实现。代码事宜,私信博主,程序定制、设计指导。 🚀基于MATLAB仿真的BCC卷积码维特比译码算法 目录 🚀1.BCC卷积码概述 🚀2.维特比译码算法 🚀2.1概述 🚀2.2算法核心思想 🚀2.3算法优缺点 🚀2.4应用实例 🚀2.5部分源代码和仿真截图 🚀1.BCC卷积

【5G NR】【一文读懂系列】移动通讯中使用的信道编解码技术-卷积码原理

目录 一、引言 二、卷积编码的发展历史 2.1 卷积码的起源 2.2 主要发展阶段 2.3 重要里程碑 三、卷积编码的基本概念 3.1 基本定义 3.2 编码器框图 3.3 编码多项式 3.4 网格图(Trellis)描述 四、MATLAB示例 一、引言 卷积编码,作为数字通信领域中的一项关键技术,自其诞生以来便受到广泛关注。卷积编码是一种纠错编码方法,它通过

Verilog | 卷积码实现

一、卷积码(convolution code) 卷积码是一种差错控制编码,由P.Elias于1955年发明。因为数据与二进制多项式滑动相关故称卷积码。卷积码在通信系统中应用广泛,如IS-95,TD-SCDMA,WCDMA,IEEE 802.11及卫星等系统中均使用了卷积码。以(n,k,m)或者(n,k,L)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n为每个k元组码字对应的卷积码输出n

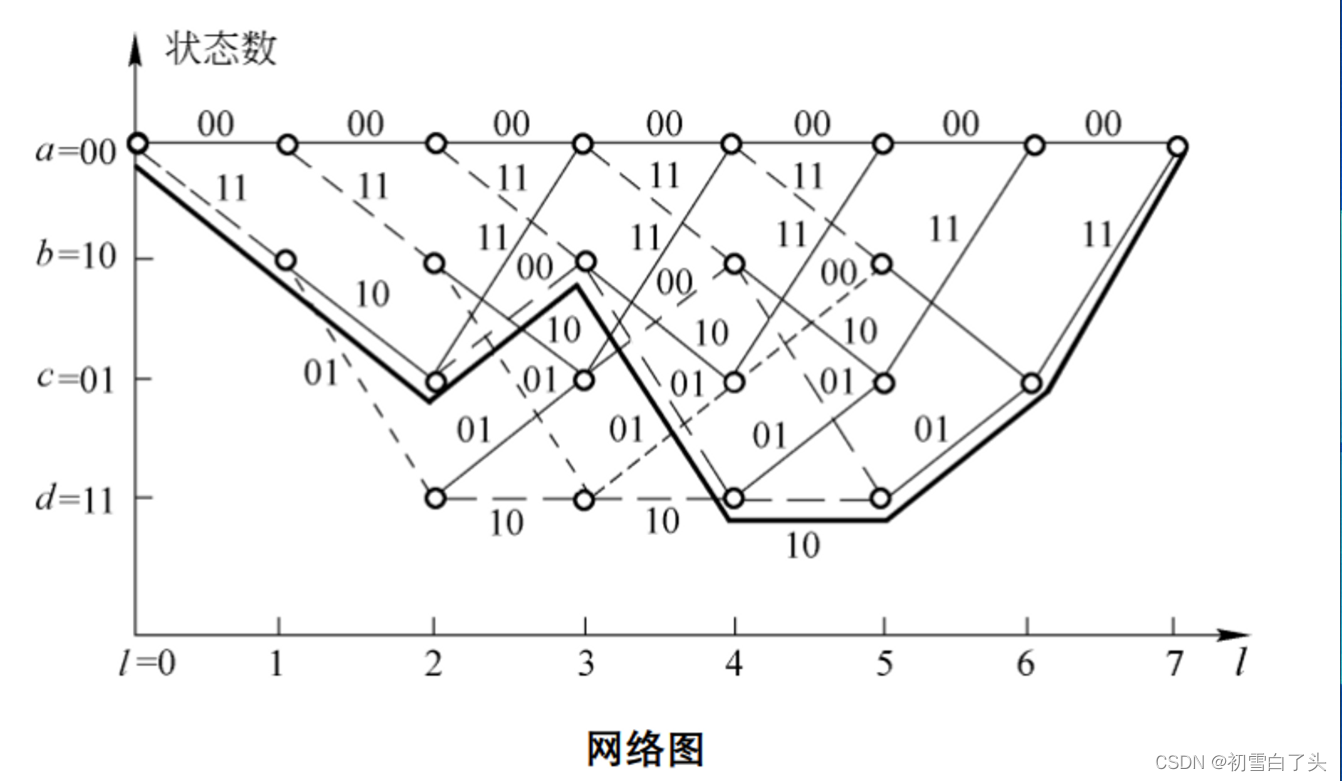

维特比译码器(Viterbi Decoder)硬件架构(一)--卷积码及编解码算法介绍

1. 卷积码(convolution code) 卷积码在无线通信里用的非常广泛,通常卷积码编码器开始工作前都要进行初始化,按编码器的初始状态不同可以分为两类: 1.1 末尾补零卷积码(Tail-bits): 通常卷积码编码器开始工作时都要进行初始化,编码开始前将编码器的所有寄存器单元都进行清零处理。而在编码结束时,需要添加0到码流末尾(Tailed Termination),使编码器状态归

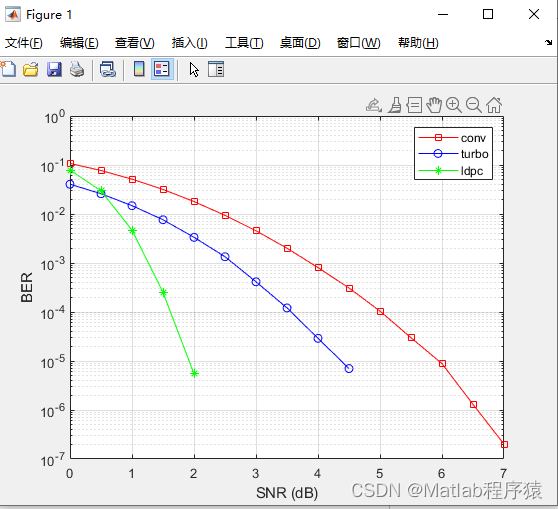

【MATLAB源码-第69期】基于matlab的LDPC码,turbo码,卷积码误码率对比,码率均为1/3,BPSK调制。

操作环境: MATLAB 2022a 1、算法描述 本文章介绍了卷积码、Turbo码和LDPC码。以相同的码率仿真这三种编码,并对比其误码率性能 信源输出的数据符号(二进制)是相互独立和等概率的; 信道是加性白高斯噪声信道(AWGN);采用BPSK调制,忽略载波;(3,1,2)卷积码:移位寄存器个数为2,码率为1/3,生成多项式g=[5,7,7];卷积码译码采用Viterbi最大似然译码

【MATLAB源码-第69期】基于matlab的LDPC码,turbo码,卷积码误码率对比,码率均为1/3,BPSK调制。

操作环境: MATLAB 2022a 1、算法描述 本文章介绍了卷积码、Turbo码和LDPC码。以相同的码率仿真这三种编码,并对比其误码率性能 信源输出的数据符号(二进制)是相互独立和等概率的; 信道是加性白高斯噪声信道(AWGN);采用BPSK调制,忽略载波;(3,1,2)卷积码:移位寄存器个数为2,码率为1/3,生成多项式g=[5,7,7];卷积码译码采用Viterbi最大似然译码

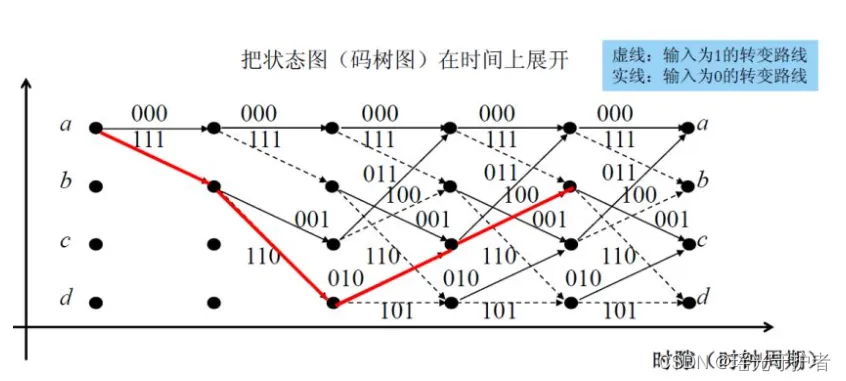

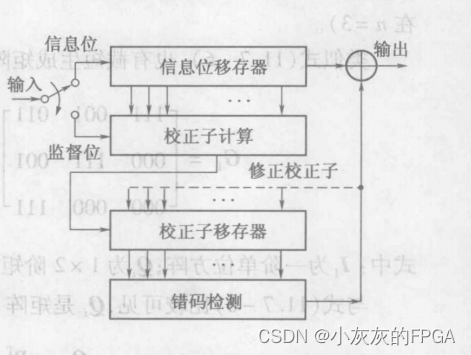

通信原理板块——卷积码(原理、代数和几何表示、编码和解码)

微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等 1、卷积码定义 卷积码(convolutional code)是一种线性非分组码,适用于前向纠错。 卷积码在编码是,把k比特的信息段变成n个比特的码组,但是监督码元不仅仅和当前的k比特信息段有