例化专题

DSP48E1 (primitive)原语例化实例2

DSP48E1 (primitive)原语例化实例2 再补充两个比较常用的用法。 1 o <= in1*in2-c OPMODE=7'b0110101 ALUMODE=0001 CARRYIN=1 ALUMODE = 0001 可以实现- Z + (X + Y) - 1 = not (Z) + X + Y。 OPMODE[6:4]=011, Z选择C

DSP48E1 (primitive)原语例化实例

DSP48E1 (primitive)原语例化实例 之前倒腾dsp48e1的时候发现网上虽然有一些文章,但是大部分都是无用的文章, 正如某位同仁说的,高手都忙于泡妞,哪有精力来写文章, 把之前倒腾的代码贴出来供大家参考。 先把OPMODE和ALUMODE贴上,来自网上的文章 OPMODE用来决定下面这个图X,Y,Z这些mux的选择,一时半会看不懂,稍微花点时间是可以看懂的

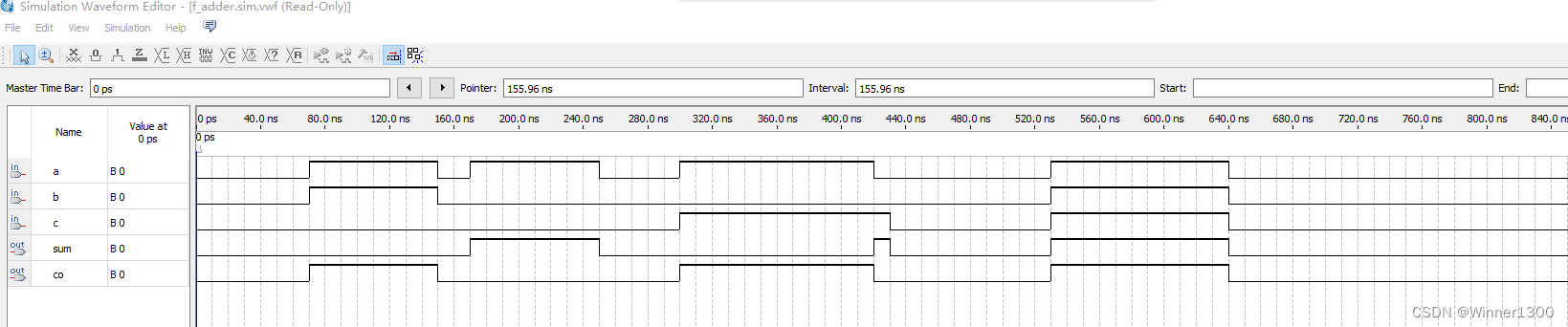

EDA 全加器设计及例化语句应用

文章目录 前言一、全加器是什么?二、使用步骤1.半加器2.全加器1.新建一个全加器工程2.添加半加器的.v文件到全加器工程中3.新建全加器.v文件,写程序,调用半加器.v文件 完成例化 三、仿真效果总结 前言 提示:这里可以添加本文要记录的大概内容: 项目需要: 提示:以下是本篇文章正文内容,下面案例可供参考 一、全加器是什么? 示例: 二、使用步骤 1.半

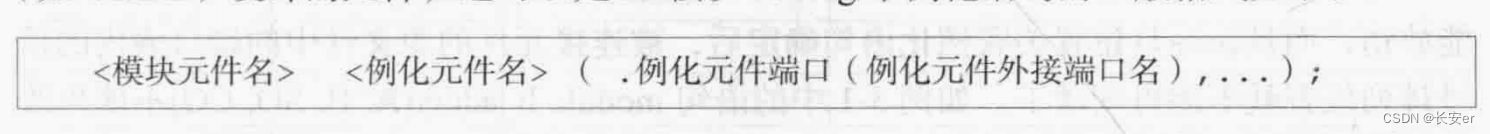

FPGA中的模块调用与例化

目录 一、模块调用与实例化 1.1 模块调用 1.2 模块实例化 1.3 Verilog例化语句及其用法 1.3.1 例化语句的基本格式 1.3.2 实例化三种不同的连接方法 二、模块调用实例-全加器与半加器 2.1 半加器模块 2.2 全加器模块 三、参数定义关键词与整数型寄存器 3.1 参数定义关键词 parameter 3.2 局部参数定义关键词 localpar

vivado:调试工具原理及实现学习总结(调用IP核,生成IP,例化,调试)

内容:调用vivado提供的IP核,生成用户定制的IP,并通过HDL语言进行例化。然后通过提供的调试功能对设计进行调试,分析调试结果。 环境:VIVADO 2018.2 语言:Verilog HDL 参考书目:Xilinx FPGA权威设计指南 -Vivado 2014集成开发环境 创建新的fifo调试工程 创建工程,project name:fifo_verilog,芯片参考选择xc7a10