本文主要是介绍FPGA中的模块调用与例化,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一、模块调用与实例化

1.1 模块调用

1.2 模块实例化

1.3 Verilog例化语句及其用法

1.3.1 例化语句的基本格式

1.3.2 实例化三种不同的连接方法

二、模块调用实例-全加器与半加器

2.1 半加器模块

2.2 全加器模块

三、参数定义关键词与整数型寄存器

3.1 参数定义关键词 parameter

3.2 局部参数定义关键词 localparam

3.3 整数型寄存器 integer

四、总结

一、模块调用与实例化

在 FPGA 中,模块调用和实例化是一种常见的组织和复用硬件设计的方式,首先是模块调用

1.1 模块调用

·模块:在 FPGA 设计中,模块是指一个独立的硬件功能单元,通常由一段 Verilog 或 VHDL 代码描述。模块可以实现各种功能,例如时钟分频器、计数器、状态机等。

·调用:在设计中需要使用某个模块时,可以通过模块调用来引入该模块。这样可以在当前模块内使用该模块的功能。

模块调用的语法如下所示(以 Verilog 为例):

module TopModule;// 模块调用ModuleName instance_name (port_list);// ...

endmodule

其中,ModuleName 是被调用的模块的名称,instance_name 是实例化该模块的实例名,port_list 是模块的输入输出端口连接。1.2 模块实例化

·实例化:模块实例化是指创建并使用模块的一个具体实例,将模块的功能引入到设计中。实例化过程会为模块创建一个独立的实例,并通过连接输入输出端口与其他模块进行通信。

·参数化实例化:在实例化时,可以通过参数化的方式为模块传递参数来配置其功能。这样可以根据需要创建多个具有不同配置的模块实例。

模块实例化的语法如下所示(以 Verilog 为例):

module TopModule;// 模块实例化ModuleName #(.parameter_name(parameter_value)) instance_name (port_list);// ...

endmodule

其中,ModuleName 是要实例化的模块的名称,parameter_name 是模块定义中的参数名,parameter_value 是要传递给参数的值,instance_name 是实例化该模块的实例名,port_list 是模块的输入输出端口连接。

通过模块调用和实例化,可以将设计分成多个模块,每个模块负责一个特定的功能,并通过连接和调用的方式组合起来实现复杂的系统功能。这种模块化的设计方式有助于提高代码的可读性、可维护性和重用性。

1.3 Verilog例化语句及其用法

例化的对象叫做实例或实体,即元件。元件例化即是引入一种连接关系,将设计好的模块定义为一个元件,然后利用特定语句将此元件与当前的设计实体的指定端口相连接。

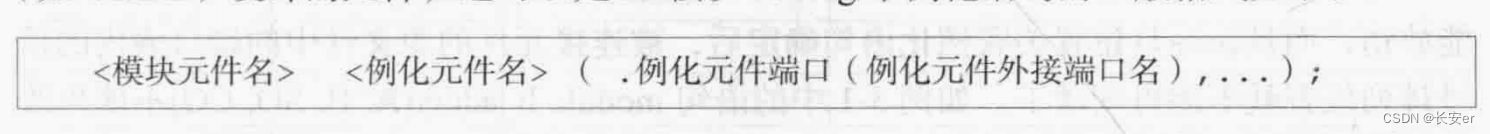

1.3.1 例化语句的基本格式

1.3.2 实例化三种不同的连接方法

在 Verilog 中,模块实例化时可以使用三种不同的连接方式,即位置关联法、名称关联法和混合关联法。

(1)位置关联法(Positional Association):

位置关联法是最基本的连接方式,通过按照模块定义中端口的顺序来连接输入输出端口。

例如,在实例化模块时,按照模块定义中端口的顺序依次连接对应的信号。这种方式要求信号的顺序与模块定义中端口的顺序完全一致。

module my_module(input a, input b, output c);// 模块内部逻辑

endmodule// 使用位置关联法实例化 my_module

my_module inst1( input_signal_a, input_signal_b, output_signal_c );

(2)名称关联法(Named Association):

名称关联法是通过指定端口名来连接输入输出端口,这种方式下顺序可以任意排列。

在实例化模块时,为每个端口明确指定连接的信号,不必按照模块定义中端口的顺序进行连接。

module my_module(input a, input b, output c);// 模块内部逻辑

endmodule// 使用名称关联法实例化 my_module

my_module inst1( .a(input_signal_a), .b(input_signal_b), .c(output_signal_c) );

(3)混合关联法(Mixed Association):

混合关联法允许使用位置和名称两种关联方式的组合。一部分端口使用位置关联,另一部分端口使用名称关联。

module my_module(input a, input b, output c);// 模块内部逻辑

endmodule// 使用混合关联法实例化 my_module

my_module inst1( .a(input_signal_a), input_signal_b, .c(output_signal_c) );

这三种关联法灵活地满足了不同的连接需求,可以根据具体情况选择合适的方式来实例化模块,并连接输入输出端口。

二、模块调用实例-全加器与半加器

当在 FPGA 设计中需要实现全加器功能时,通常可以利用半加器模块来实现。下面我将以全加器调用半加器为例,详细分析模块调用与实例化的过程:

2.1 半加器模块

首先,我们需要定义半加器的模块。半加器是一个简单的加法器,用于对两个输入进行相加并输出结果和进位。以下是一个 Verilog 实现的半加器模块的示例代码:

module half_adder(input a, input b, output sum, output carry);assign sum = a ^ b;assign carry = a & b;

endmodule

在上面的代码中,half_adder 模块接受两个输入 a 和 b,并输出 sum(和)和 carry(进位)。

2.2 全加器模块

接下来,我们需要定义全加器模块,并在其中调用半加器模块。全加器通过组合多个半加器来实现更高位的加法运算。以下是一个 Verilog 实现的全加器模块的示例代码:

module top_module(input a, input b, input cin, output sum, output cout);wire s1, c1, c2;// 实例化第一个半加器模块half_adder ha1 (.a(a),.b(b),.sum(s1),.carry(c1));// 实例化第二个半加器模块half_adder ha2 (.a(s1),.b(cin),.sum(sum),.carry(c2));// 计算总的进位assign cout = c1 | c2;

endmodule

上述使用的是名称关联法,若使用位置关联法则是

在上面的代码中,full_adder 模块使用了两个半加器模块 half_adder 来实现全加器的功能。首先,通过调用 half_adder 模块两次,分别实现两个半加器的功能。然后,根据半加器的输出和输入进位 cin 计算最终的和 sum 和进位 cout。

通过以上示例,我们展示了如何在 FPGA 设计中实现全加器模块调用半加器模块的过程。模块化设计的方式有助于提高代码的可读性和可维护性,同时也方便了对功能模块的复用和扩展。

用名称关联法

三、参数定义关键词与整数型寄存器

当在 Verilog 中进行硬件描述语言的设计时,参数定义关键词 parameter 和 localparam 以及整数型寄存器 integer 都扮演着重要的角色。它们分别用于定义参数、局部参数和整数型寄存器。以下是它们的详细介绍:

3.1 参数定义关键词 parameter

1.参数使用关键词 parameter 进行定义,允许在模块内外赋值并且在编译时生效。参数可以在模块实例化时被改变,但在编译时保持不变。

2.参数定义的格式和语法如下:

parameter parameter_name = value;

其中,parameter_name 是参数的名称,value 是参数的值。参数的值可以是常数、表达式或其他参数,但不能包含任何输入或输出端口。参数可以被用于指定模块的大小、延迟等属性,也可以用于配置模块的功能。

3.注意点:

参数一旦在编译时确定,就不能再修改。

参数可以用于指定模块的大小、延迟等属性,也可以用于配置模块的功能。

参数可以在模块实例化时被改变,但在编译时保持不变。

4.parameter的参数传递功能

在 Verilog 中,parameter 用于定义模块的参数,它具有参数传递的功能,可以在模块实例化时传递参数值。这样可以使得同一个模块在不同的实例中使用不同的参数值,从而实现模块的灵活复用和定制化。

当定义一个模块时,可以将参数定义为 parameter,并在模块实例化时为这些参数赋值。这样做的好处是,可以通过改变参数值来改变模块的行为或特性,而无需修改模块的定义。

示例1:演示如何在 Verilog 模块中使用 parameter 来进行参数传递:

module MyModule #(parameter WIDTH = 8)

( input [WIDTH-1:0] data, output reg [WIDTH-1:0] result ); // 使用 parameter 定义的宽度来进行操作

always @(*) begin result = data + WIDTH; // 使用 parameter 定义的宽度进行计算

end endmodule

在上面的示例中,MyModule 模块使用了一个名为 WIDTH 的 parameter,并将其用作数据宽度。在模块实例化时,可以为 WIDTH 参数赋予不同的值,以定制模块的行为。

示例2:模块实例化,展示了如何传递参数值:

module Testbench; // 实例化 MyModule 模块并传递参数值

MyModule #(4) dut1 (input_data, output_result1);

MyModule #(8) dut2 (input_data, output_result2);

// ... endmodule

在这个示例中,实例化了两个 MyModule 模块,分别为它们传递了不同的 WIDTH 参数值。这样,dut1 和 dut2 所代表的两个模块将使用不同的参数值进行实例化,从而实现了参数传递的功能。

通过 parameter 参数传递功能,可以实现对模块的定制化配置,提高了模块的灵活性和重用性。

3.2 局部参数定义关键词 localparam

局部参数使用关键词 localparam 进行定义,类似于 parameter,但它们只能在当前模块中使用。

局部参数定义的格式和语法如下:

localparam parameter_name = value;

其中,parameter_name 是局部参数的名称,value 是局部参数的值。局部参数的定义和使用方式与参数类似,不同之处在于 localparam 只能在当前模块中使用。

注意点:

局部参数只能在当前模块中使用。

局部参数一旦在编译时确定,就不能再修改。

3.3 整数型寄存器 integer

在 Verilog 中,整数型寄存器 integer 用于声明整数类型的变量,可以用于存储整数值。整数型寄存器通常用于逻辑运算、计数器等场景。

整数型寄存器的定义格式和语法如下:

integer variable_name;

其中,variable_name 是整数型寄存器的名称。整数型寄存器可以用于存储整数值,并且可以进行逻辑运算和算术运算。

注意点:

整数型寄存器可以用于存储整数值,并且可以进行逻辑运算和算术运算。

整数型寄存器可以在 always 块、initial 块和 task/function 中使用。

四、总结

在 FPGA 设计中,模块调用和实例化是一种常见的组织和复用硬件设计的方式。模块调用是指引入一个模块以在当前设计中使用其功能,而模块实例化则是创建并使用模块的具体实例,将其功能引入到设计中并通过连接输入输出端口与其他模块进行通信。

在 Verilog 中,模块实例化可以通过位置关联法、名称关联法和混合关联法来实现端口连接。位置关联法按照模块定义中端口的顺序连接输入输出端口,名称关联法通过指定端口名连接输入输出端口,而混合关联法允许两种关联方式的组合,以满足不同的连接需求。

举例来说,当需要在 FPGA 设计中实现全加器功能时,可以调用半加器模块来实现。通过在全加器模块中实例化多个半加器模块并按照需要连接其输入输出端口,可以实现更高位的加法运算。这种模块化的设计方式有助于提高代码的可读性、可维护性和重用性,同时也方便对功能模块的扩展和调用。

参数定义关键词 parameter 用于定义可在模块内外赋值并且在编译时生效的参数。

局部参数定义关键词 localparam 类似于 parameter,但它们只能在当前模块中使用。

整数型寄存器 integer 用于声明整数类型的变量,可以用于存储整数值,并且可以进行逻辑运算和算术运算。

天天开心!学习进步!

这篇关于FPGA中的模块调用与例化的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!