vcs专题

解决IDEA菜单栏找不到VCS的问题,且使用IDEA推送新项目到托管仓库

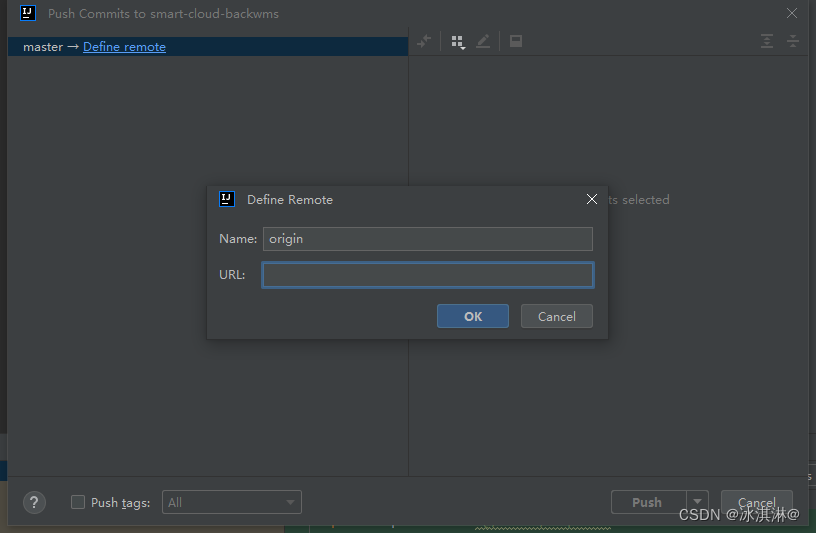

问题描述: 在idea软件中使用git推送项目,idea页面顶部菜单栏无VCS 解决方案: 一:File->Settings->Version Control-> 点击+ ->选择项目->VCS:->点击ok: 二:托管平台创建一个Git仓库来保存idea要推送的项目(此处使用的是github): 三:idea中将项目推送到Git仓库中: 3.1:点击

IC开发——VCS基本用法

1. 简介 VCS是编译型verilog仿真器,处理verilog的源码过程如下: VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。 VCS使用步骤,先编译verilog源码,再运行可执行文件: 编译命令的格式:vcs sourcefile [compile_ti

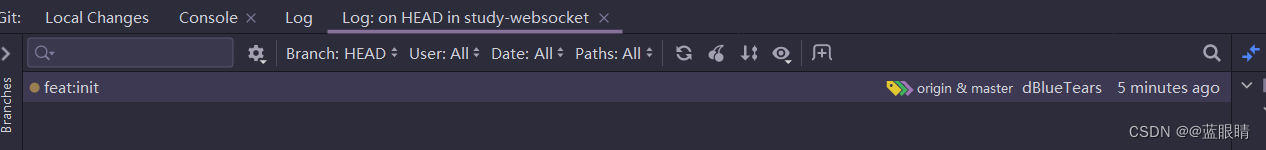

2023idea没有VCS首次提交代码到Git

1、setting 2、vcs------>create git repository 3、右键项目----->Git------>add 4、右键项目------>git------>commit Directory 之后就会显示这个页面(下面写你提交的信息,就是你修改了什么) 点击commit,提交 5、Git--------->push 6、选

ubuntu 20.04 安装 VCS + Verdi

Ubuntu16.04安装VCS和Verdi Ubuntu 16.04 VCS+Verdi安装总结 - 灰信网(软件开发博客聚合)

Co-Simulation of C with Verilog in VCS

Co-Simulation of C with Verilog in VCS Introduction Verilog PLI(编程语言接口)是一种从Verilog代码调用C或C ++函数的机制。   在Verilog代码中调用的函数称为系统调用。 内置系统调用的示例是$ display,$ stop,$ random。PLI允许用户创建自定义系统调用,Verilog语法不允许我们

开发常用VCS(版本控制系统)

引言:也是受到Idea的启发,现将自己近些年来使用过或待尝试的版本控制系统进行归纳,总结。 几个名词及概念: VCS:版本控制系统(Version Control System / Revision Control System,或者叫做源码控制系统Source Control System,简称VCS),是软件开发人员最常用的工具之一。DVCS:分布式版本控制系统(Distributed V

UVM基础知识1:在vcs中,sv通过DPI调用C函数实例(连接简单的C子程序)

来源:systemverilog验证 测试平台编写指南(书籍) 1 新建counter7.c文件 vi counter7.c #include<svdpi.h>void counter7(svBitVecVal * o,const svBitVecVal * i,const svBit reset,const svBit load){s

UVM基础知识0:在vcs中,sv通过DPI调用C函数实例

来源:systemverilog验证 测试平台编写指南(书籍) 1 新建factorial.c文件 vi factorial.c int factorial (int i) {if (i <= 1) return i;else return i*factorial(i-1);} 2 新建test.sv文件 vi test.sv import "DPI-C" funct

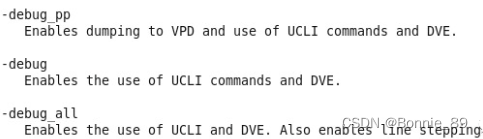

【VCS】VCS 常用参数总结

-debug选项,为了导出VPD通常选择-debug_pp; 2. 常用编译选项 No.命令描述1 +define+= 命令行进行宏定义,在代码中使用了`ifdef 编译指令2 +mindelays器件延时使用sdf 文件中的最小值(sdf 文件中的时序(min:typ:max))3 +maxdelays 器件延时使用sdf 文件中的最大值4 –v导入库文件的ve

利用cvs2svn和svn-importer 将vcs项目转成svn

公司将svn架设起来了.现在需要将所有的代码,文档统一通过svn管理起来.(公司的项目比较多.有的项目组是单独.所以使用版本管理的工具很多.有的用cvs,svn,vss等等.但是主要的是cvs和svn).通过投票表决.决定统一使用svn. 作为技术组.要提供技术支持,遇到的问题是各个项目组将原来使用cvs的项目转成svn.当然最主要的是要保存以前的版本. 任务下达后.google后

vcs generate coverage report

1,GUI界面 dve -cov ./coverage.vdb 2,cml生成文本文件格式 urg -dir coverage.vdb 参考: http://www.testbench.in/CO_04_COVER_POINTS.html

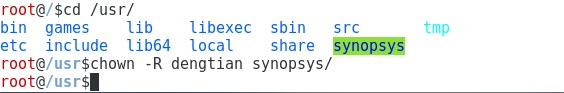

3、ubuntu14.04/16.04 安装VCS

首先下载其安装包:链接:https://pan.baidu.com/s/1iokjsBTa0YYIhG9rlJEreg 提取码:1ayj 然后通过wincap 拖到linux(ubuntu14.04 或者ubuntu 16.04) 第一步:在/home/ubuntu/目录下建立主文件夹 mkdir synopsyscd synopsysmkdir synopsysmkdir vcs_20

4、linux环境下,使用VCS进行Verilog和C语言联编译

`timescale 1ns / 1nsmodule test;initialbegin$hello;// #10 $stop;#10 $finish;endendmodule/**********************************************************************/ 文件名为hello_test.v #include

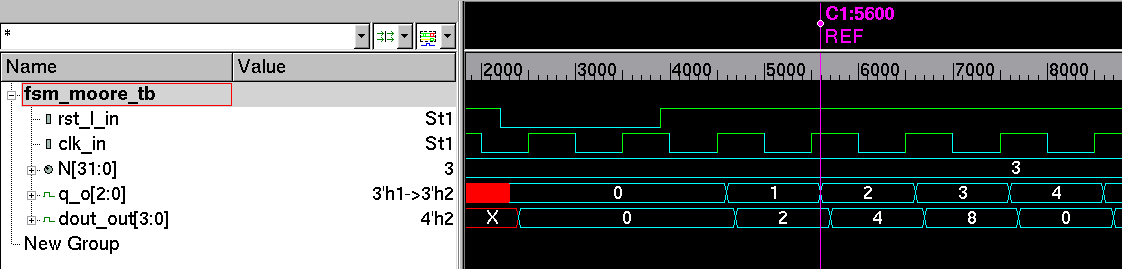

vcs编译systemverilog并且用verdi查看波形

转载自:http://blog.chinaaet.com/weiqi7777/p/5100017757 对于编写的systemverilog代码,在linux下,可以使用vcs编译,但是编译的时候,要注意,要加入几个选项。 整个过程,linux使用的是64位的redhat,vcs使用的是vcs2015,verdi使用的是verdi2015。如以下的systemverilog代码。

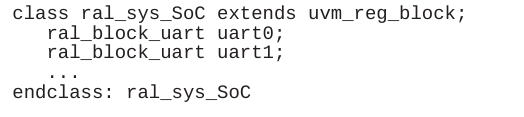

VCS的ralgen命令产生UVM寄存器模型

文章目录 前言一、寄存器描述表格二、生成 .ralf 寄存器文件2.1 field2.2 register2.3 register block2.4 system 三、产生UVM寄存器模型 前言 在验证时,寄存器模型是必不可少的一个环境,且在项目中可能面临着需要不断更新迭代的需求。那么如何快速建立 UVM寄存器模型 呢?采用VCS ralgen脚本的主要步骤如下: 中心

Makefile脚本启动VCS+Verdi

文章目录 一、快速入门二、Makefile的语法1.语法格式2.命令执行3.变量 三、VCS仿真1.VCS常用命令2.Makefile实现自动化仿真 四、VCS+Verdi的使用1.编译2.仿真3.Verdi 查看fsdb文件的命令4.Makefile启动VCS+Verdi的实例 注:主要侧重于Makefile调用VCS和Verdi联合仿真。 一、快速入门 Mak

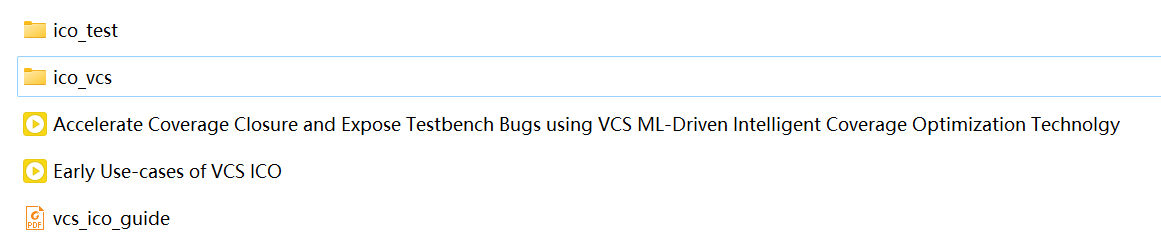

VCS ICO - Intelligent Coverage Optimization

ico是vcs提供的用于优化覆盖率的feature;一般用户通过dist solver bofore等约束了变量的随机概率,而ico会在用户约束的基础上,做一些自动“修正”,以此来优化随机激励,提高随机多样性,加速覆盖率收敛,缩短 turn-around time TAT。 主要功能包含如下几部分: Prognosis: 用于查看当前平台是否适用ico,对于都是直接用例测试,没有随机策略的平台,

Makefile与VCS/Questasim联合运用实例

文章目录 一、Questasim的Makefile编写1.1.Makefile编写实例1.2.辅助方法1.2.1.-help命令查询1.2.2.手册查询 二、VCS的Makefile编写2.1.Makefile编写实例一 ——插入随机种子seed2.2.Makefile编写实例二 ——灵活指定编译文件2.3.Makefile编写实例三 ——DVE软件查看波形和覆盖率2.4.Makefile

记一次idea问题—performing vcs refresh...

01、前言 本人出现该场景是,我把本地SVN A项目删了,而A项目与B项目同在一个SVN目录下,当我修改B项目且提交代码时,出现了该问题。 idea不是很懂操作,就搜索了一下得出了三种答案,但只有其一帮助了我。 02、方法一 选择 File --> Invalidate Caches / Restart -->Invalidate and Restart,idea重启之后就好了 网上

vcs makefile

主要参考: VCS使用Makefile教程_vcs makefile-CSDN博客https://blog.csdn.net/weixin_45243340/article/details/129255218?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522170524049516800227431373%2522%252C%252

关于CentOS7安装VCS等EDA仿真软件过程中遇到的问题

自述(前面废话可以忽略,直接进入正题) 本文原创,转载请注明出处! 第一次写文章,依照“国际惯例”,总归是要说些废话,即所谓的写在前面: 碍于目前普通院校本科教育课程体系的限制,几乎都只是停留在通识教育阶段,除非你有心并且某位老师愿意带你,才有机会在本科阶段进入实验室,接触真正的项目。工科所需要的工程能力要求是很高的,本科教育阶段的实践太少,即便有也只是流于形式,所谓实验课很多都是依葫芦画瓢,大

android studio svn提交时performing vcs refresh时间很长

解决方案: 测试有效 https://blog.csdn.net/zeal9s/article/details/88615092

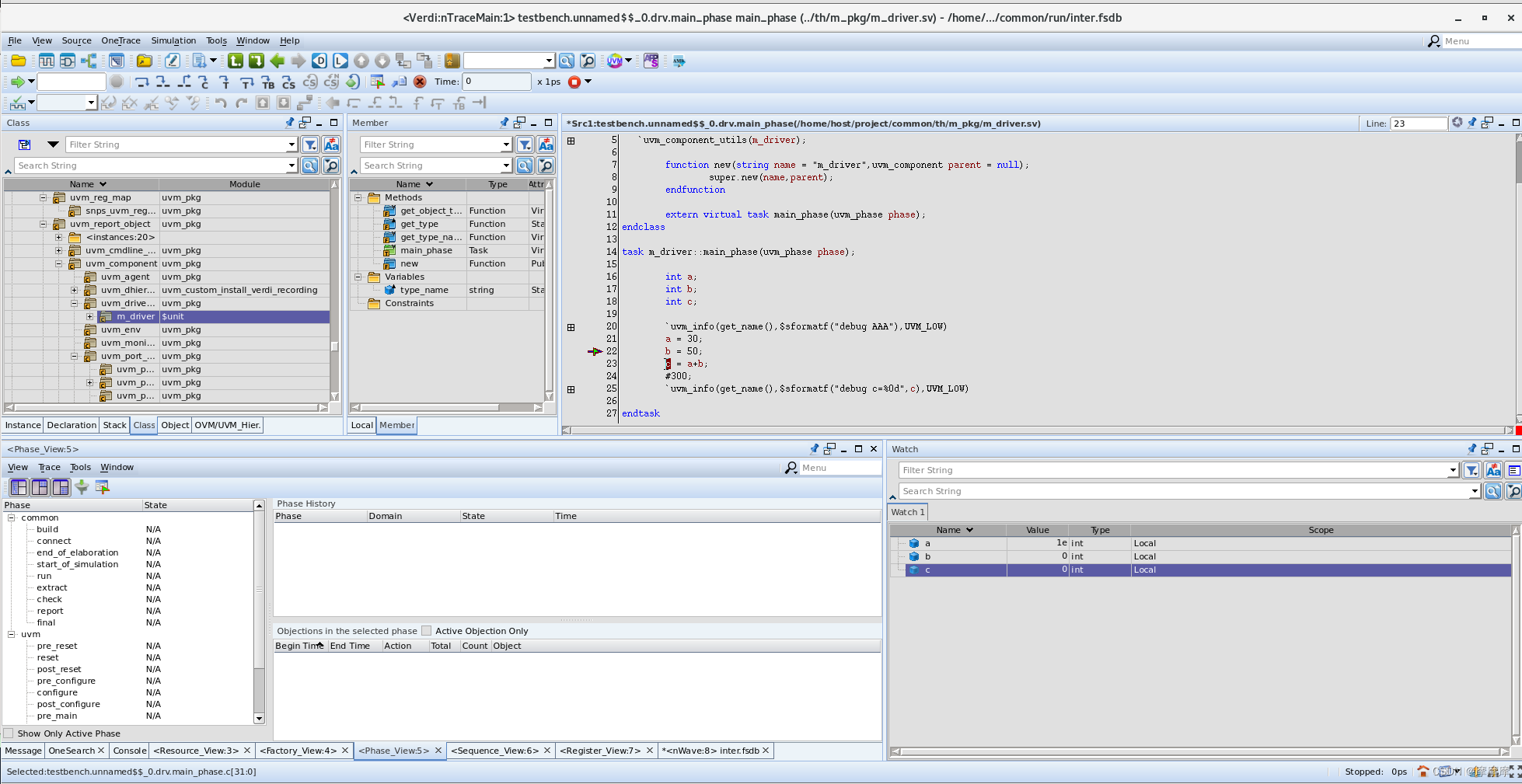

vcs+verdi+uvm单步调试及问题记录

编译 编译选项如下: vcs -ntb_opts uvm -sverilog -f $PROJ_ROOT/tb/option.f -debug_access+all -kdb -lca -full64 -fsdb_old -timescale=1ns/10ps 其中最重要的是要加上这四项 -debug_access+all -kdb -lca -full64 option.f里面的内容如