serdes专题

LVDS与SerDes到底是什么关系?

随着智能座舱和智能驾驶功能的应用,汽车中的摄像头和液晶屏越来越多,多种图像显示和多屏互动也成为增强汽车智能化和用户体验的重点内容。 这些图像显示功能需要在不同的控制器之间或者控制器与远端的液晶屏或摄像头之间进行数据传输。 比如中控与仪表之间,座舱域控制器与各个显示屏之间,摄像头与控制器之间等等。 而远程的数据传输就需要串行通信。汽车中最常用的串行通信协议是CAN总线,各个控制器之间的数据

慷智serdes调试记录(AIM951-958)

项目使用的是AIM951~958 951和958测试图谱输出 下面是两种1920*1080不同屏幕timing的951图谱输出(一般我们提供屏幕timing,然后找慷智FAE要下寄存器配置,他有一个xcel文档,可以自己设置屏幕timing然后得到寄存器设置值,表见另外的附件) -------------951 pattern output-----------i2cset -fy 8 0

Serdes系统中的CTLE技术

典型的SerDes系统包含输入数据、串行器、发射机(TX)、信道、接收机(RX)、解串器和输出数据。串行数据比特流被输入到发送器。发射机由均衡器(EQ)和包括封装效果的线性模拟后端组成。传输后端和接收器前端之间的通道由传输线(TL)组成,传输线可以包括布线和印刷电路板走线。 Serdes高速信号完整性问题 典型的SerDes系统信道是包含发射信号的高频衰减的线性系统。下图显示了与具有100

SerDes系列之CTLE均衡技术

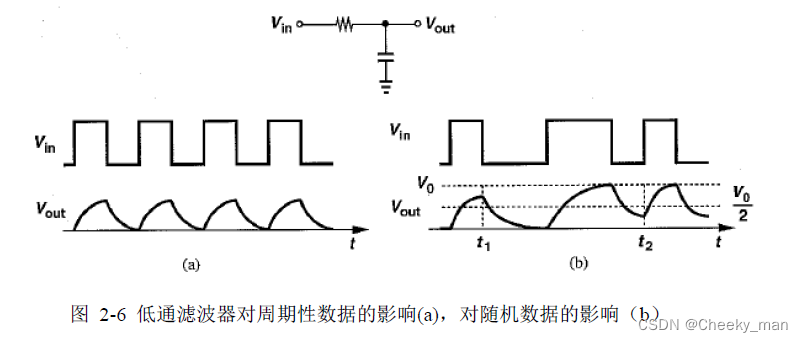

CTLE(连续时间线性均衡)是一种施加在接收器上的线性模拟高通滤波器,通过衰减低频信号分量,以补偿奈奎斯特频率附近的衰减比例,从而实现信道补偿。当低频信号分量向下衰减并推入底噪范围时,CTLE就会失去调节动力,与Tx FFE 一样,CTLE 仅解决通道的总的低通滤波效应,使用上可以考虑避免重复。 CTLE 支持交流增益和EQ设置,交流增益中均衡器对低频频谱施加

SerDes系列之电路技术概述

现在的高速电路设计中,SerDes的应用几乎无处不在,如下图所示的一款SoC,其外设接口除了少量普通的IO,几乎都是SerDes专用接口,因此,电路设计中对于SerDes接口电路的熟知程度,几乎就决定了设计的成败。 本文以概述的形式,陈述了SerDes电路设计中的关键技术元素,让读者了解这些基本概念的同时,也为后续的系列文章进行铺垫。 S

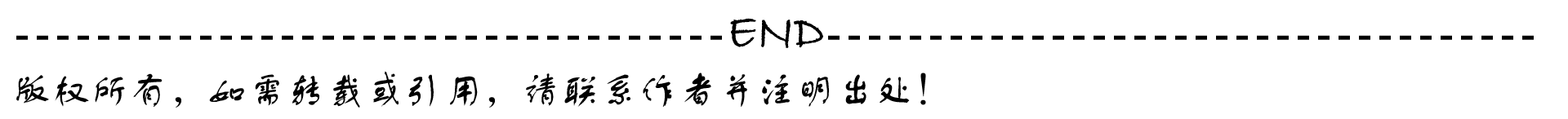

serdes 同轴电缆和双绞线接法

1、同轴电缆 Coaxial Cable 2、双绞线STP(Shielded Twisted Pair) 比如我们用的车载camera一般就只需要接一路即可,RIN+接camera, RIN-通过电容接地。

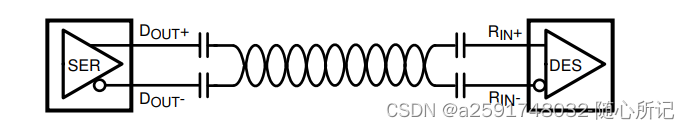

【相机方案】智能驾驶的域控采用的“串行器和解串器”方案的总结(持续更新),SerDes,GMSL

SerDes是Serializer/Deserializer的缩写,即串行器和解串器。由于同轴线的传输延迟几乎可以忽略不计(ns级别),相当于将原来只能短距离传输的高速并行信号(MIPI/I2C/CLK等)的传输距离延长,真正做到高带宽、低延迟、长距离的数据传输。 SerDes的串行-解串可以通过数模电路或者FPGA来实现。在商用领域,出于性价比的考量,往往会使用独立IC芯片来实现这个功能,GM

Intel FPGA IP之LVDS SerDes IP学习

FPGA 视频数据输入输出直通工程: 屏:13.2吋8bit色深,屏幕分辨率为1440*1920@60,具有两个Port,每个Port有4个差分数据对与1个差分时钟对,差分对均支持LVDS协议芯片:Cyclone V系列FPGA目的:通过FPGA的LVDS SerDes RX接口输入8bit 色深RGB图像数据,然后再通过LVDS SerDes TX接口输出8bit 色深RGB图像数据,是个直通

【学习笔记】Serdes中的高速接口设计

参考文献: 一、绪论 1.1 背景 “串行替代并行”: 串行传输使用差分信号传输以传输更长距离; 并行传输因串扰无法长距离传输;并行线路对信号偏斜量的要求,限制了最大的传输速率。 SerDes=Serializer + Deserializer Serializer:用于Tx端,译为串行器,将并行数据转化为串行数据(并转串)。 PLL:时钟源,以低速参考时钟作为输入,

手撕书系列 之 《High Speed Serdes Devices and Applications》 (一)

目录 第一章 Serdes Concepts 1.1 并行数据总线 1.2 源同步接口 1.2.1 减小I/O pin 的数量 1.2.2 Clock Forwarding(时钟传播) 1.2.3 Higher Speed Source Synchronous Interfaces 前序: 工作方向需要学习 SerDes 相关内容,找来行业圣经先啃一啃, 由于个

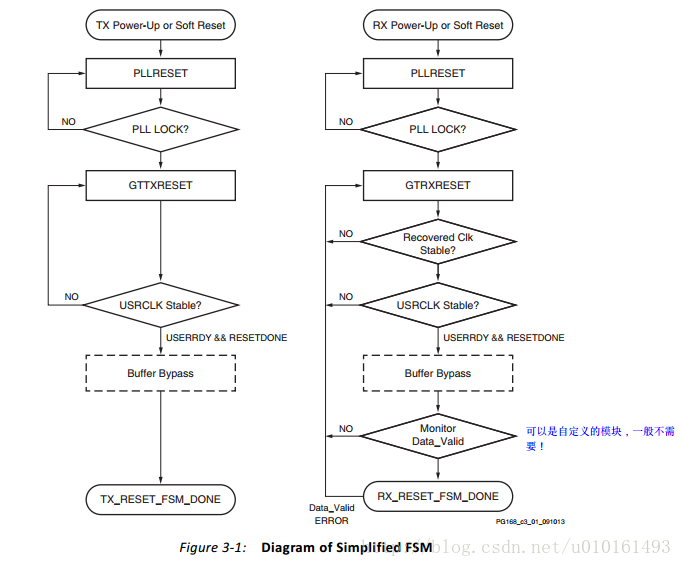

Serdes系列总结——Xilinx serdes IP使用(三)——12G serdes

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 Serdes系列总结——Xilinx serdes IP使用(三)——12G serdes IP核的详细设置IPexample的使用附件 器件:Xilinx zynq zu6cg 版本:vivado2019.2 实现:12.16512G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对se

LATTCE ECP3 FPGA serdes调试出错,数据乱码怎么解决?

完整版请点击https://hifpga.com/问题/36956 向博主本人提问FPGA相关问题 大家好。我们在跑两片 FPGA 之间使用Serdes通信的时候,发现 RX 出现错误。TX 端发送的数据是从0一直累加1,但是接收端RX收到的数据是杂乱无章,没有规律的,同时有一堆的 Error 状态出现。 硬件同事测量眼图说信号质量是符合要求的(见下图)。 我这个工程很简单,就是将I

Lattice ecp5 SerDes接收异常怎么解决?

完整版请点击https://hifpga.com/问题/36654 向博主本人提问FPGA相关问题 目前有个项目需要Lattice ecp5 (型号:LFE5UM-25-6MG285C)与 Xilinx k7之间通过两路SerDes进行通信,从ecp5发送到k7端是两路1.485G的SerDes信号,从k7端发送至ecp5端是一路SerDes信号(速率为0.7425G和1.485G都

xilinx A7 (artix 7)serdes GTP 生成的example例程注释解析

本文首发于hifpga.com XILINX的 serdes GT IP真的是够复杂的,生成的例子也是复杂,而且为了适配各种情况,代码里很多冗余的东西,发送部分比较简单 ,接收部分有点繁琐,我做了点注释,这里的只做的GTP的,GTX的自己看吧。 ///// ____ ____ // / /\/ / // /___/ \ / Vendor: Xilinx //

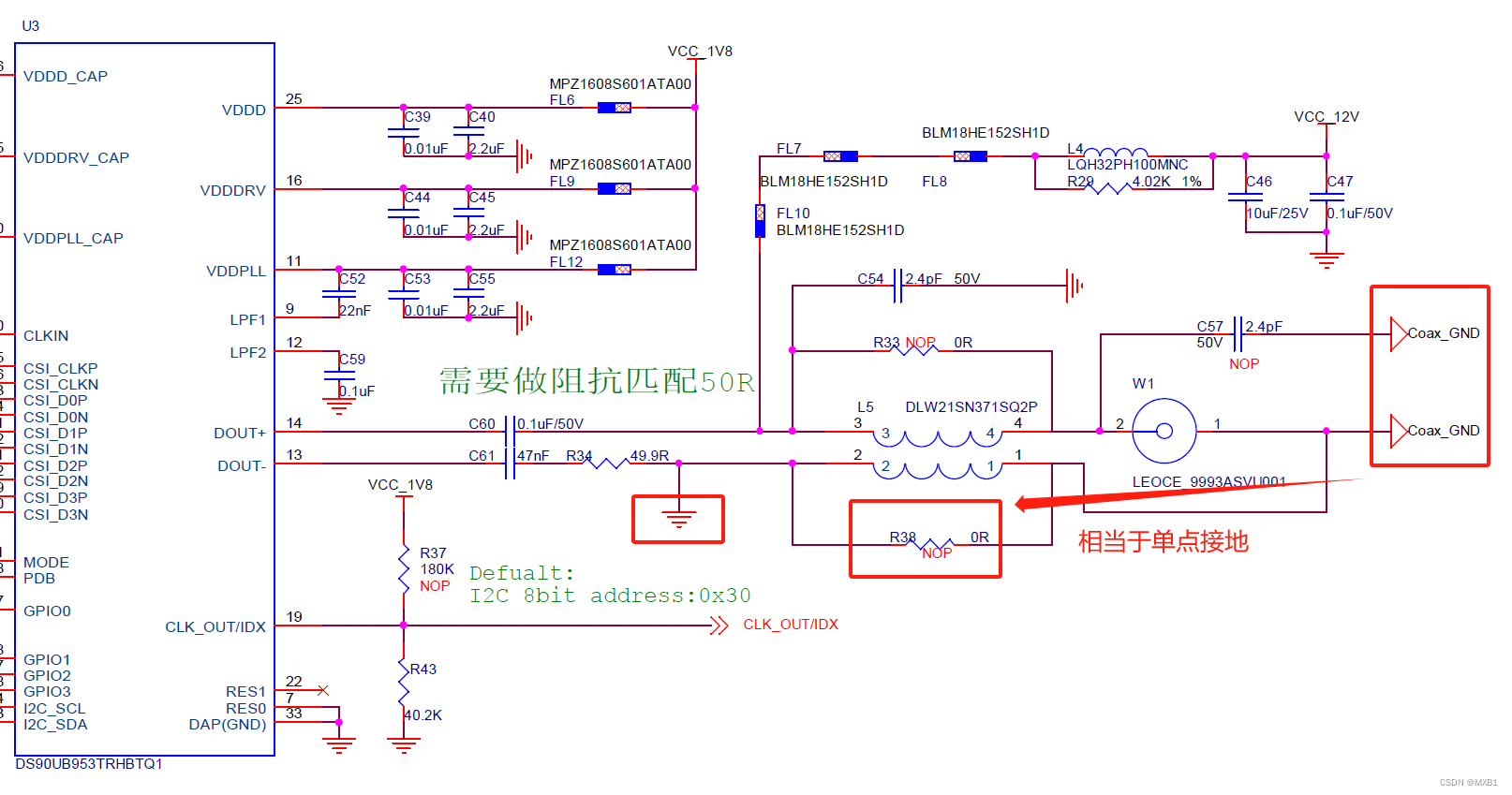

高速信号同轴线接口地处理(Serdes 953)

现象:高速通道的通信不稳定,出现图像丢帧、图像黑屏等 描述:通过开发板测试同轴信号通信质量,排查到接口共模去掉后换成了两个0欧姆电阻连接,相当于信号地单点连接,0欧在高速通信情况下一般用于数字/模拟参考地的分割,但此时不适用,应该保持参考地的完整性,不应该使用0欧姆连接,相当于起到了电感/磁珠的高频信号隔离的作用。在同轴地处直接刮铜连接,信号直连恢复OK。

PCIe Electrical PHY(2)-SerDes中的均衡技术

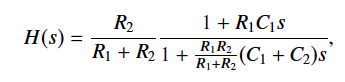

均衡的主要作用就是减小Jitter中ISI部分的影响。前面已经讲了ISI产生的原因主要是因为信道带宽不足,使脉冲信号经过信道之后产生长长的拖尾。 1.1 CTLE 均衡电路分为连续时间均衡器和离散时间均衡器。从频域角度做均衡的电路通常是具有高通特性的模拟电路,所以被称为连续时间线性均衡器(CTLE)。其结构通常如下图所示,其优点是线性度高,并且能对信号提供一定的增益。 业界主流的做法通常会把均

(转)xilinx 高速收发器Serdes深入研究-Comma码

一、为什么要用Serdes 传统的源同步传输,时钟和数据分离。在速率比较低时(<1000M),没有问题。 在速率越来越高时,这样会有问题 由于传输线的时延不一致和抖动存在,接收端不能正确的采样数据,对不准眼图中点。 然后就想到了从数据里面恢复出时钟去采样数据,即CDR 这样就不存在延迟不一致的情况,有轻微的抖动也不会影响采样(恢复的时钟会随着数据一起抖动)。 二 、为什么要用8b10b

串行总线技术(二)-串行总线中的先进设计理念及SerDes/PMA介绍

串行总线技术(二)-串行总线中的先进设计理念及SerDes/PMA介绍 字节分割/链路聚合 下面以PCIe为例对字节分割加以讨论,如图所示。 PCIe使用链路和线路来发送串行数据。链路是一个逻辑实体,能够具有单个线路或多个线路。当逻辑链路包括一个线路时,TLP和DLLP通过单一的线路发送,每次发送一字节。当链路包括多个线路时,TLP和DLLP分布在多个线路中,此时不是在不同的线路中发送不同的TL

【源码】用于SiSoft QCD和QSI通信软件接口的SerDes工具箱

SerDes工具箱基于Simulink的IBIS-AMI模型,用于SiSoft QCD/QSI的自动工程创建。 The SerDes Toolbox™ interface for SiSoft QCD/QSI automatically creates projects for channel simulation in QCD/QSI using IBIS-AMI models gener