本文主要是介绍LVDS与SerDes到底是什么关系?,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

随着智能座舱和智能驾驶功能的应用,汽车中的摄像头和液晶屏越来越多,多种图像显示和多屏互动也成为增强汽车智能化和用户体验的重点内容。

这些图像显示功能需要在不同的控制器之间或者控制器与远端的液晶屏或摄像头之间进行数据传输。

比如中控与仪表之间,座舱域控制器与各个显示屏之间,摄像头与控制器之间等等。

而远程的数据传输就需要串行通信。汽车中最常用的串行通信协议是CAN总线,各个控制器之间的数据传输、诊断等功能大部分都是通过CAN总线通信来完成的。

那么液晶屏显示数据的传输是否可以用CAN或CAN-FD呢?

首先要考虑的就是速率问题,经典CAN协议规定的最高速率是1Mb/s。新的CAN-FD协议保持了物理层不变,对数据链路层协议进行了升级,数据速率最大可达8Mb/s。

那么液晶屏的图像显示数据的传输速率需要多少呢?

我们以7寸彩色TFT液晶为例,常用的分辨率是800*480,色深是RGB888,即24位色,为了保证显示动画效果,图像刷新率不能低于60Hz。

如果采用单路的串行通信传输,简单分析先不考虑控制位,则每一帧画面的数据传输率就不能低于60*800*480*24=552Mb/s。

由此可见,即使是采用CAN-FD的8M速率,也远远无法满足图像显示的要求,如果液晶屏的尺寸和分辨率更大,则要求的速率会更高。

那么车载液晶屏的图像数据传输是用什么总线呢?

1.差分技术

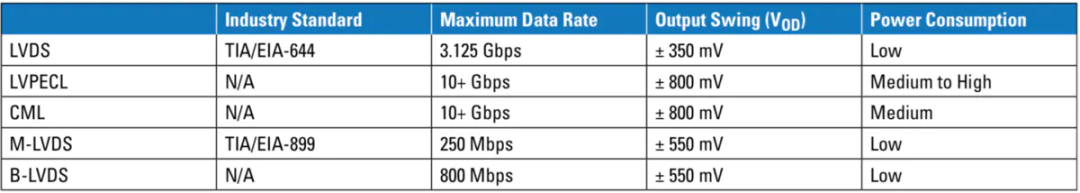

串行通信中低速率可以使用单端信号,而中高速率就需要使用差分信号,比如CAN总线就是一种中速率的差分信号。而为了实现更高速数据传输,还有多种差分技术可供选择,下图列举了最常用的几种差分信号技术和它们的主要参数。

1.1常用高速差分技术

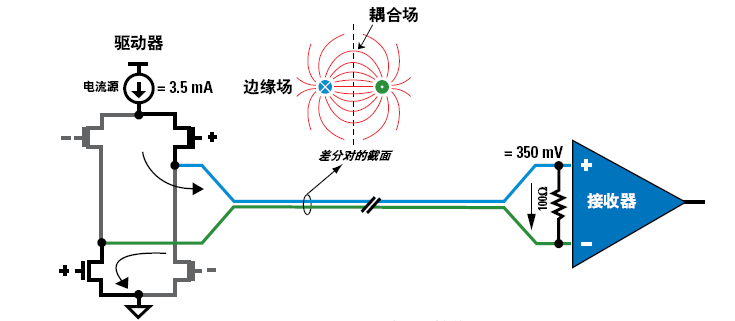

其中的LVDS是Low-Voltage Differential Signaling的缩写,表示低压差分信号。其信号摆幅最低,为350mv,功耗低,最大速率达到3.125Gbps。

1.1.1LVDS驱动器和接收器

总的来说,终接方法简单、功耗和噪声低等优点,使得LVDS成为几十Mbps至3Gbps的应用之首选。

此外,随着汽车对通信速率的要求越来越高,其中高速率的LVPECL和CML技术也开始得到了应用。尤其是CML,它的性能与LVPECL相当,但具有技术简单和集成了终接电路的优点。

CML是一种高速的点到点接口,在驱动器和接收器上均集成了终接网络。CML使用一个无源的上拉电路,阻抗一般50欧姆,采用交流耦合的实现方案,可以实现超过10Gbps的高数据率。

1.1.2典型的CML实现方案

CML的速率高,但是由于它的摆幅也高,所以它的功耗比LVDS更高。

1.1.3LVDS与CML两种差分技术速度与功耗对比

1.1.3LVDS与CML两种差分技术速度与功耗对比

LVDS、CML和LVPECL都是专门针对点到点信号传输而设计的。

点到点拓扑

点到点拓扑

另外两个B-LVDS和M-LVDS是在LVDS的基础上针对多点结构进行了优化,可以支持多分支和多点传输。

总之,LVDS和CML是常用的高速接口,其中的LVDS是差分信号中最常用的高速接口!

2.SerDes架构

早期在高速接口出现之前,提高带宽的唯一方法就是增加并行的信道,于是出现了大宽度的并行TTL信号。而远程传输时就需要通过串行器(serializer)将并行的TTL信号转化为单bit的数据流。

然后在接收处通过解串器(deserializer)再将单bit的数据流转化为并行的TTL信号使用,这种方法常被称为串化器/解串器,即SerDes。

SerDes根据不同的应用,又分为不同的架构,我们介绍下其中主要的4种架构,分别是并行时钟SerDes、嵌入式时钟SerDes、8b/10b SerDes和FPGA连接SerDes。

2.1 并行时钟SerDes

并行时钟SerDes通常用于对“数据+地址+控制”并行连接的总线进行串行化,例如PCI、UTOPIA、处理器总线和控制总线。它的主要特点就是与数据同时传输的还有一路时钟信号对,供接收器用来对数据进行锁定和恢复。

并行-时钟-串化器编码示例

并行-时钟-串化器编码示例

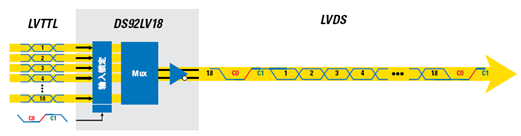

2.2嵌入式时钟SerDes

嵌入式时钟SerDes中的发送器将数据总线上的数据信号和时钟串行化,形成单路串行信号对。时钟位用于界定串化后每个字的起点和终点,即起止位。非常适合于需要同时完成原始数据、控制、奇偶校验、帧、同步、状态等信息传输的应用。它的特点是适合于非面向字节的应用,如那些需要传送未编成数据包的原始数据外加控制信号的应用场合。

18bit嵌入式时钟串化器编码示例

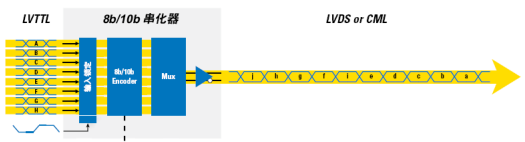

2.3 8b/10b SerDes

8-bit/10bit串化器可将每个并行数据字节映射为一个10bit的代码,然后将该10bit码串行化,传送到一个串行对上。

8b/10b-串化器编码实例

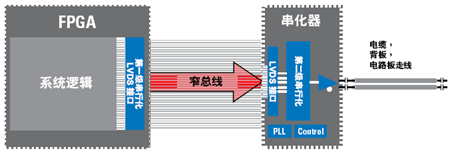

2.4 FPGA连接SerDes

FGPA连接SerDes提供了所有涉及大量模拟信号处理的功能,如时钟和数据信号恢复、信号调理、时钟合成和抖动清理,它将串化分为两级来实现。

FPGA连接串化器可优化大量处理模拟信号的功能

总之,随着行业和技术的发展,SerDes出现了各种不同的架构协议,但是LVDS仍然是SerDes中最常用的硬线接口。

3.车载高速SerDes方案

LVDS是一种差分信号的传输方式,是高速硬线接口之一,而SerDes是串行和解串的架构,可分为不同的架构协议。

如果统一硬件接口和协议标准,就可以产生通用的SerDes方案标准总线,这就像CAN总线是由ISO标准统一制定一样!

但是由于技术、市场和时间等原因,SerDes的公有协议标准一直没有得到推广和大规模应用,目前市场应用的产品主要是按各个公司的私有协议提供的解决方案,也就是说每个公司的协议都不一样,这些方案包括FPD-LINK、GMSL、APIX、GVIF等等。其中FPD-LINK和GMSL占据了全球95%的市场份额,成为SerDes方案的代表。

3.1FPD-LINK

FPD-LINK全称是Flat Panel Display Link,是由TI公司推出的高速数字视频接口,用于将笔记本电脑、平板电脑、平板显示器或 LCD 电视中图形处理单元的输出连接到显示面板的时序控制器,它也是LVDS标准第一个大规模应用的总线标准。

在车载应用中,FPD-LINK通常用于导航系统、车内娱乐、摄像头以及高级辅助驾驶系统中。由于车载环境对于电子设备来说是最严苛的要求,当前主要的FPD-LINK II及III芯片都满足AEC-Q100的汽车可靠性标准。

TI的FPD-LINK III方案

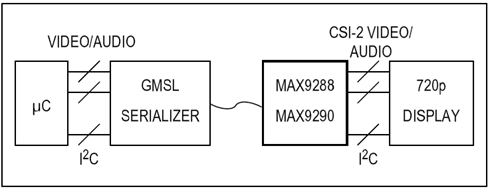

3.2GMSL

GMSL是美信公司的车载SerDes总线,用于高性能摄像头及高清视频连接,GMSL具备菊花链式连接多个摄像头模组的能力。

美信的GMSL方案

4.方案说明

以TI公司的SerDes芯片DS90UB949-Q1和DS90UB940-Q1为例,采用的是FPD-Link III接口。与FPD-Link II相比,FPD-Link III停止使用LVDS,改为使用CML的序列化高速信号接口,它支持通过同一条差分链路进行视频和音频数据传输以及全双工控制(包括I2C和SPI通信),通过两个差分对实现视频数据和控制的整合。

TI的FPD-Link III方案

TI的FPD-Link III方案

发送端的DS90UB949-Q1是一个HDMI转FPD-LinkIII的串行器,能够将高清多媒体HDMI的输入信号串行化后发出。

接收端的DS90UB940-Q1是一个FPD-Link III转CSI-2的解串器,它具有单通道或双通道FPD-Link III接口,能够从串行流中恢复数据,然后将其转换为摄像机串行接口CSI-2输出,每个CSI-2端口最多支持4个数据通道,每个通道最高1.3Gbps。

这个方案适合中控和仪表间的互联显示,比如中控向仪表发送导航或多媒体图像信息时,中控主芯片先将图形信息通过HDMI接口和串行器发送出去。仪表主芯片接收到解串为MPIC CSI-2接口图形信息,再驱动仪表显示屏来显示。

5.总结

LVDS是早期最常用的高速硬线接口,SerDes是高速串行通信的架构协议。基于LVDS接口和SerDes产生了多种不同的解决方案,甚至新的高速方案已经不使用LVDS,但是由于LVDS是这个方案的最早和最典型的应用,也是其它硬件接口的基础,所以大家还是习惯于把这类高速的SerDes方案称为LVDS总线!

这篇关于LVDS与SerDes到底是什么关系?的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!