lvds专题

RK3288 点亮LVDS屏

本文记录调试 LVDS接口屏的一些关键步骤,主要是dts文件中关于 频率、分辨率 、时序参数的设置 环境: RK3288 9tripod CV5 linux 4.4.189 LCD:JYT121XQ01 (追曦 DS1212)12.1电容触控屏 查看屏幕规格书 只要在rockchip dts 中 设置 T(HB)=Thb+Thf+Thsyn=320clock T

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。本文介绍的实例可方便扩展到具有类似接口格式的其他高速数据转换器设计。 1.概述 ADS4249是一款双通道、14位、250MSPS ADC,具有双总线、字节级数字接口。ADS4249接口示例适用于许多TI高速ADC,包

新路程------imx6 lvds ioctl

最近有个需求,做一些接口给上层应用调用 于是看了一下驱动,linux有一套标准的framebuffer机制让我们做接口,就是fb_ioctl 首先看对应的framebuffer驱动,在之前的ldb.c中,确实配置了对应的fb_info结构体,但是要修改这个结构体的参数并不需要在ldb.c中做,在mxc_ipuv3_fb.c里 static struct fb_ops mxcfb_ops

新路程------英飞凌imx6的lvds驱动

最近拿到一块开发版,打算在lvds上做些小修改,之前也接触过一点驱动,但是现在的驱动框架看起来和之前的有点差异。 关于lcd的参数信息请参考这篇文章 http://blog.csdn.net/longxiaowu/article/details/24319933 lvds的驱动在framebuffer驱动之下,也就是上层应用只知道有个framebuffer设备也就是dev/fb,而至于下

LVDS与SerDes到底是什么关系?

随着智能座舱和智能驾驶功能的应用,汽车中的摄像头和液晶屏越来越多,多种图像显示和多屏互动也成为增强汽车智能化和用户体验的重点内容。 这些图像显示功能需要在不同的控制器之间或者控制器与远端的液晶屏或摄像头之间进行数据传输。 比如中控与仪表之间,座舱域控制器与各个显示屏之间,摄像头与控制器之间等等。 而远程的数据传输就需要串行通信。汽车中最常用的串行通信协议是CAN总线,各个控制器之间的数据

使用泰克示波器DPO7254C测量LVDS时钟信号眼图

1.连接差分探头,开机,将差分探头接触到需要测量的P,N时钟上(整个测量过程手不能抖动,否则会影响测量效果)。 2.如图所示,点击Analyize。 3.点击Jitter and Eye Analyize(DPOJET)。 4.点击One Touch Jitter。 5.等待一会,就会出现眼图(Eye Diagram)。 6.点击放大第三幅图,全屏显示眼图。

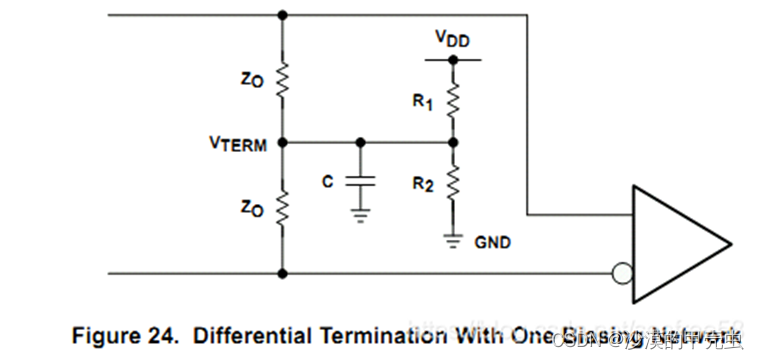

FPGA与高速ADC LVDS数据接口设计考虑

引言:本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点。 1. LVDS简介 1.1 什么是LVDS? LVDS(低压差分信号)标准是业界流行的差分数据传输标准,它是双线、低摆幅差分信号。其优点包括以下几点: •低电源电压运行 •高速数据传输 •良好的共模噪声抑制 •噪音产生更少 图1:LV

『FPGA通信接口』LVDS接口(4)LVDS接收端设计

文章目录 1.LVDS接收端概述2逻辑框图3.xapp855训练代码解读4.接收端发送端联调5.传送门 1.LVDS接收端概述 接收端的传输模型各个属性应该与LVDS发送端各属性一致,例如,如果用于接收CMOS图像传感器的图像数据,则接收端程序的串化因子、通道个数等将要与设备一致。在硬件设计上,LVDS时钟线和LVDS数据线应该等长设计,但由于布线制板工艺的影响,难免数据线和

『FPGA通信接口』LVDS接口(2)硬件设计

文章目录 1.LVDS原理2.xilinx器件对于LVDS的支持3.LVDS信号PCB布线要求4.传送门 1.LVDS原理 如上图所LVDS的工作原理示意图,其Driver驱动器由一个恒流源是LVDS发送端(通常为 3.5mA)驱动一对差分信号线组成。驱动状态会翻转就产生正负电压的变化,在接收端表现为01状态切换。在接收端有一个高的直流输入阻抗(几乎不会消耗电流),所以几

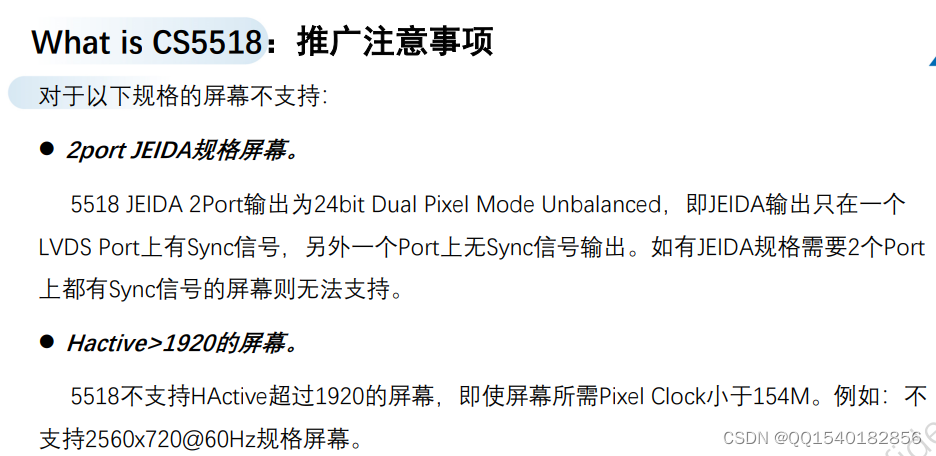

CS5518芯片设计|替代GM8775设计方案|MIPI转LVDS芯片方案|DSI转LVDS芯片方案

CS5518支持常见的1920*1080分辨率的屏,支持视频格式为 FULL HD(1920 x 1200)。为MIPI DSI 转LVDS 双通道桥接芯片,实现将MIPI DSI信号转换为单/双通道 LVDS输出功能,MIPI 支持1/2/3/4 通道可选,支持 4Gbps 速率。LVDS 时钟频率154MHz,该芯片主要应用于手持设备、双屏显示,大屏幕显示等应用需求。 CS5518和其他品牌

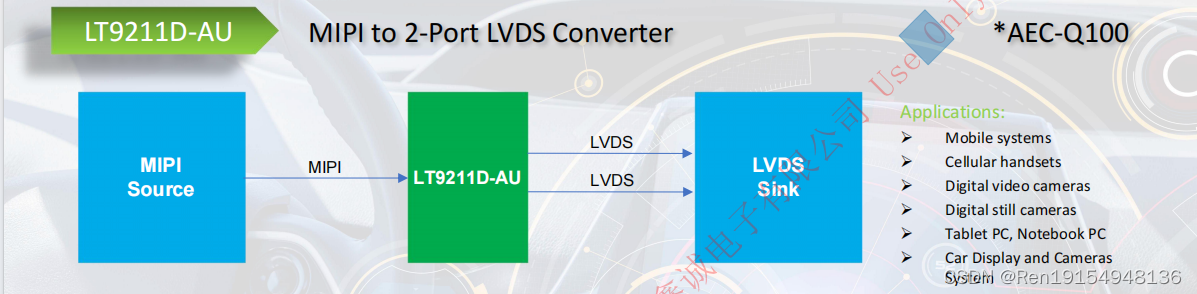

龙迅LT9211D MIPIDSI/CSI桥接到2 PORT LVDS,支持 3840x2160 30Hz分辨率

龙迅LT9211D描述: LT9211D是一款高性能的MIPI DSI/CSI-2到双端口LVDS转换器。LT9211D反序列化输入的MIPI视频数据,解码数据包,并将格式化的视频数据流转换为AP和移动显示面板或摄像机之间的LVDS发射机输出。LT9211D支持最大12.5 dB输入均衡和可编程预强调,以提高性能。 MIPI接收器: ▪兼容DCS1.02,D-PHY1.2,DSI1.2和

MS21112S单通道 LVDS 差分线路接收器

MS21112S 是一款单通道低压差分信号 (LVDS) 线 路接收器。在输入共模电压范围内,差分接收器可以 将 100mV 的差分输入电压转换成有效的逻辑输出。 该芯片可应用于 100Ω 的受控阻抗介质上,进行点对 点基带数据传输。传输介质可以是印刷电路板、背板 或电缆。数据传输速率和距离取决于介质的衰减特 性、工作的噪声环

LVDS与单端信号比较

高速差分信号电气规范要求其发送端和接收端之间串接一个电容,以进行AC耦合。该电容也被称为AC耦合电容。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。 1. 差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”

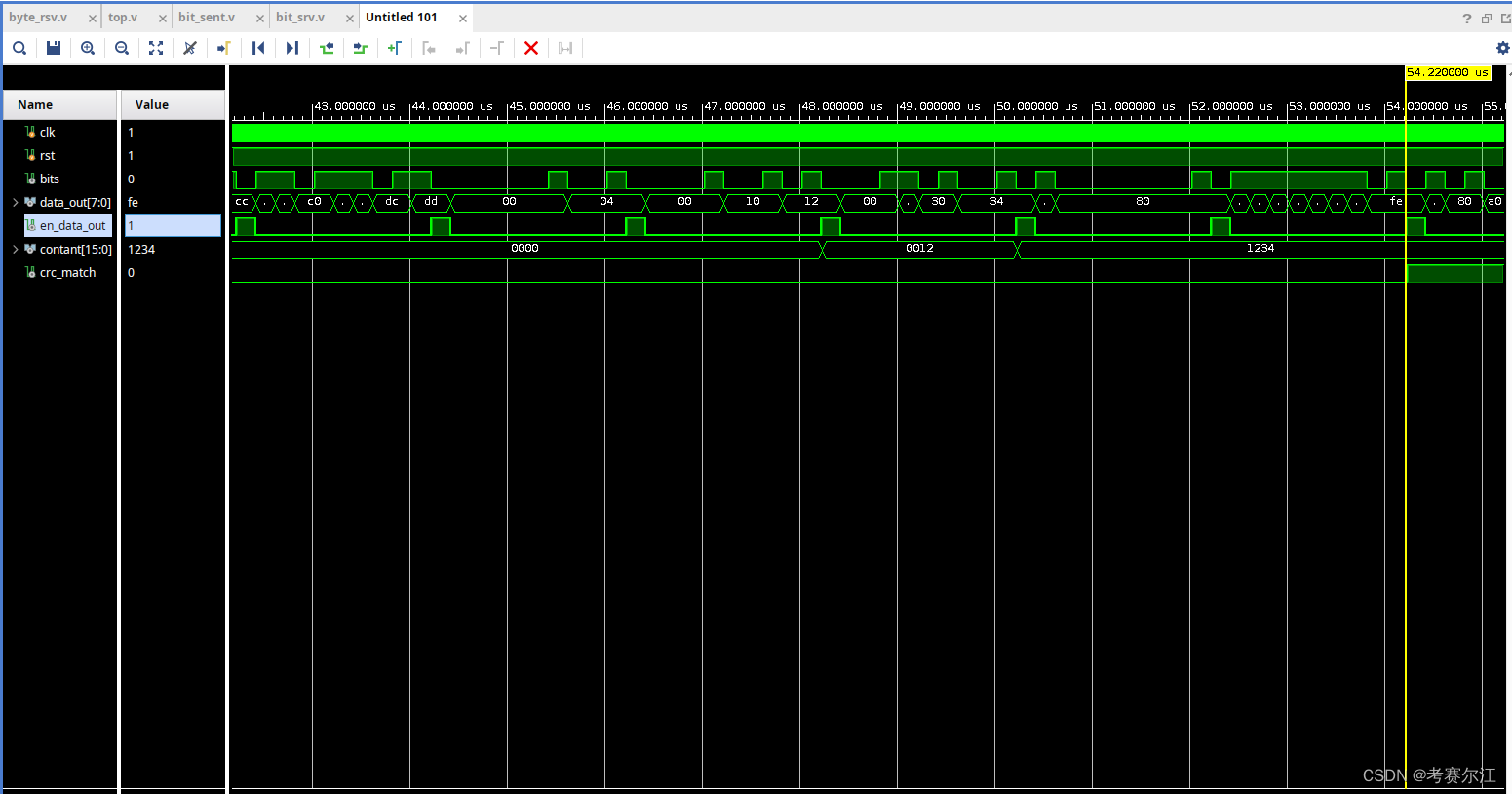

FPGA verilog LVDS通信协议笔记

一幅图胜过千言万语 直接开始挫代码,先写top.v。 module top();reg clk; // 生成时钟的寄存器reg rst; // 生成复位信号的寄存器initial clk = 1; // 初始值取1always #1 clk = ~clk; //1ns取反一次initial begin // 复位信号,先0,过段时间赋1rst = 0;# 20;r

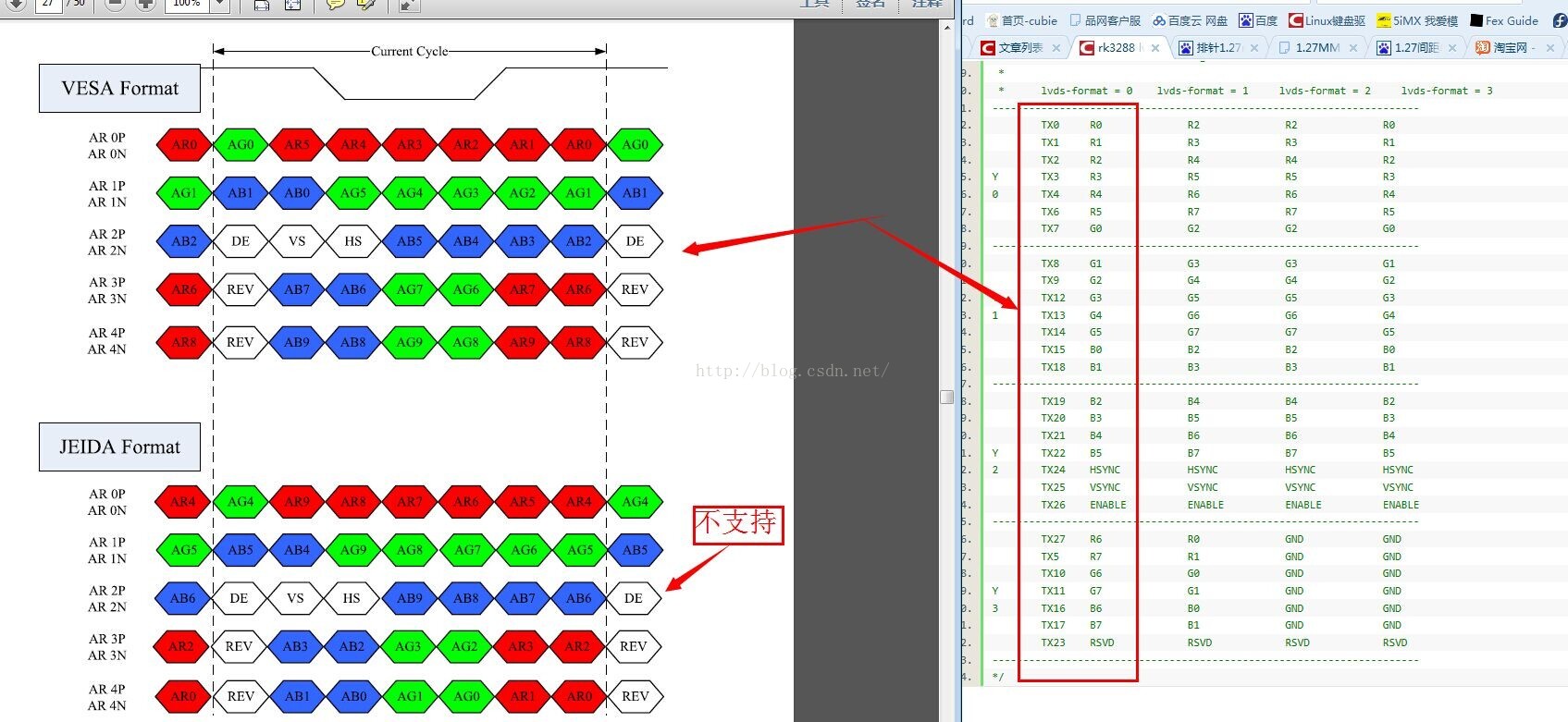

rk3288 lvds TF卡修改屏参

1,,以宽视屏M215HGE-L21_-奇美21.5液晶显示屏 为例说明修改屏参为题!! 奇美21.5寸规格书下载: 屏参文件dis.cfg, 如下: [display_param]screen-type = 3; //=2;为单8 =3;为双8 for LVDSlvds-format = 0; //0=LVDS_VESA 1=LVDS_JEIDA

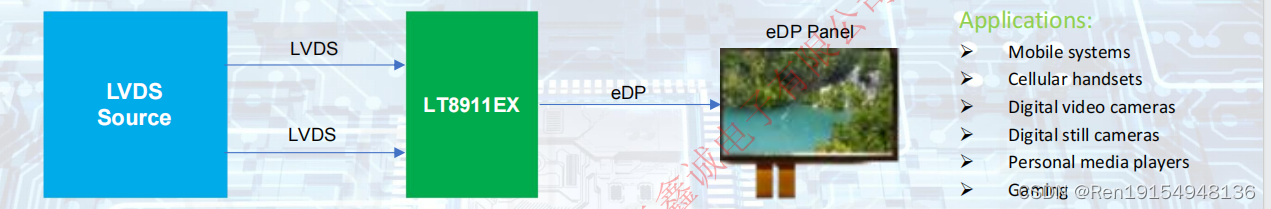

龙迅LT8911EX 双端口LVDS桥接到EDP,支持4K30HZ的分辨率

龙迅LT8911EX描述: Lontium LT8911EX是LVDS到eDP转换器,具有单端口或双端口可配置的LVDS接收器,有1个时钟通道和最多8个数据通道,每个数据通道最大运行1.2Gbps,最大输入带宽为9.6Gbps。转换器将输入LVDS数据去序列化,解码包并将格式化的视频数据流转换为单链路VESA eDP1.4兼容的输出,具有1/2/4可配置数据通道,支持RBR(1.62Gbps)和

ECL、LVDS和CML电平

芯片间互连通常有三种接口:PECL(Positive Emitter-Coupled Logic)、LVDS(Low-Voltage Differential Signals)、CML(Current Mode Logic)。 各接口电平规范 ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。以上三种均为射随输出结构,必须有电阻

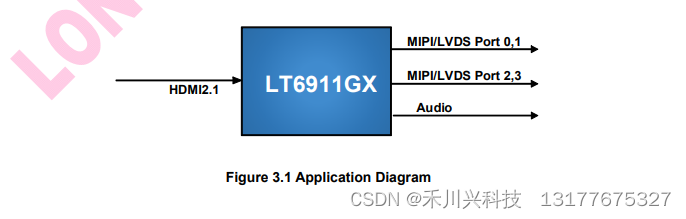

LT6911GX HDMI2.1 至四端口 MIPI/LVDS,带音频 龙迅方案

1. 描述LT®6911GX 是一款面向 VR / 显示应用的高性能 HDMI2.1 至 MIPI 或 LVDS 芯片。HDCP RX作为HDCP中继器的上游,可以与其他芯片的HDCP TX配合使用,实现中继器功能。对于 HDMI2.1 输入,LT6911GX 可配置为 3/4 通道。自适应均衡功能使其适合长电缆应用,最大带宽高达 32Gbps。对于 MIPI 输出,LT6911GX 具有可配置的

LT2611UXC HDMI2.0 (3Gbps)转 发射器(2 端口 LVDS)

1. 描述LT®2611UXC 是一款面向机顶盒、DVD 应用的高性能 LVDS 至 HDMI2.0 转换器。LVDS输入可配置为单端口或双端口,具有1个高速时钟通道和3~4个高速数据通道,工作速率最高为1.2Gbps/通道,可支持高达9.6Gbps的总带宽。LT2611UXC 支持用于 2D 和 3D 应用的灵活的视频数据映射路径。HDMI2.0输出支持高达3Gbps的数据速率,可为4k@30H

LT2611UX四端口 LVDS转 HDMI2.0,带音频

描述LT®2611UX 是一款面向机顶盒、DVD 应用的高性能 LVDS 至 HDMI2.0 转换器。LVDS输入可配置为单端口、双端口或四端口,具有1个高速时钟通道和3~4个高速数据通道,工作速率最高为1.2Gbps/通道,可支持高达19.2Gbps的总带宽。LT2611UX 支持灵活的视频数据映射路径,适用于 2D 和 3D 应用。HDMI2.0输出支持高达6Gbps的数据速率,可为4k@60

国产POL8903 LVDS转MIPI带旋转功能方案介绍

一、芯片简介 1、系统 高性能 MIPS 32bit CPU 内核: 高性能 DSP 内核图像处理单元 16KB指令 Cache 16KB数据 Cache 96KB片上 SRAM 内嵌DDR3控制器 2、 LVDS 输入 支持1或者2通道 LVDS 输入 支持最大1920x1080@60Hz输入 兼容 VESA 和 JEIDA 格式 通道内5条差分信号对,支持1clock/

液晶屏MIPI接口与LVDS接口区别

原文链接:http://bbs.elecfans.com/jishu_887561_1_1.html 液晶屏接口类型有LVDS接口、MIPI DSIDSI接口(下文只讨论液晶屏LVDS接口,不讨论其它应用的LVDS接口,因此说到LVDS接口时无特殊说明都是指液晶屏LVDS接口),它们的主要信号成分都是5组差分对,其中1组时钟CLK,4组DATA(MIPI DSI接口中称之为lane),

振兴国腾GM8775C MIPIDSI桥接到双 PORT LVDS

GM8775C描述: GM8775C 型 DSI 转双通道 LVDS 发送器产品主要实现将 MIPI DSI 转单 / 双通道 LVDS 功能,MIPI 支持 1/2/3/4 通道可选,每通道最高支持 1Gbps 速率,最大支持 4Gbps 速率。LVDS 时钟频率高达 154MHz ,最大支持视频格式为 FULL HD ( 1920 x 120

SAMSUNG 2440用LVDS传输时闪屏

现象: 一端用了DS90C383B把RGB信号转换成LVDS,另一端用DS90C384接受转换为TTL信号连接到AT070TN92上。时钟设置的是25M,结果是屏亮了,但是系统在读写NANDFLASH或者进行网络操作时屏幕会闪烁。这个可能是什么原因?谢谢! 解决办法: 摘自CSDN的论坛 仅作记录 需要时查看 (1)时钟和数据是同步输出的; (2)如果AHB总线冲突,会优先保证

差分逻辑电平 — LVDS、CML、LVPECL、HCSL互连

前言 首先了解差分逻辑电平、单端逻辑电平的基础知识 地址:常见的逻辑电平_常用的逻辑电平-CSDN博客 注: ECL >> PECL >> LVPECL演变; ECL速度快,驱动能力强,噪声小,但是功耗大,使用中需要负电源。为了简化电源,出现了PECL和LVPECL的输出模式。PECL电路速度快,驱动能力小,噪声小,高频。高功耗是PECL输出的主要缺点,且不同电平不能驱动

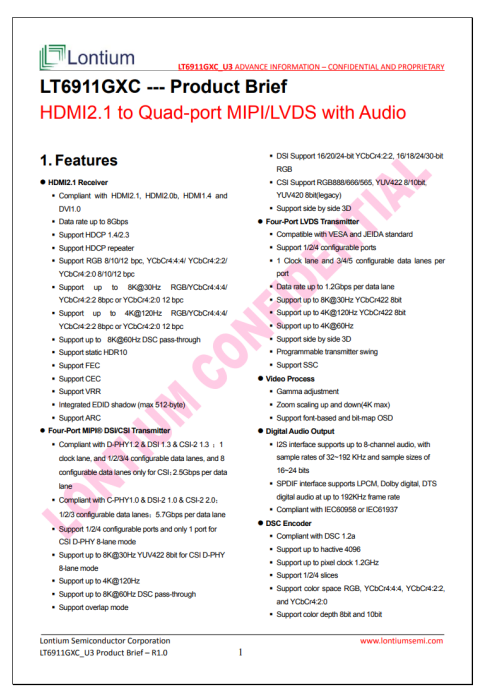

LT6911GXC HDMI2.1 至四端口 MIPI/LVDS,带音频

说明 LT®6911GXC 是一款面向 VR / 显示应用的高性能 HDMI2.1 至 MIPI 或 LVDS 芯片。 HDCP RX作为HDCP中继器的上游,可以与其他芯片的HDCP TX配合使用,实现中继器功能。 对于 HDMI2.1 输入,LT6911GXC 可配置为 3/4 通道。自适应均衡功能使其适合长电缆应用,最大带宽高达 32Gbps。 对