本文主要是介绍串行总线技术(二)-串行总线中的先进设计理念及SerDes/PMA介绍,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

串行总线技术(二)-串行总线中的先进设计理念及SerDes/PMA介绍

字节分割/链路聚合

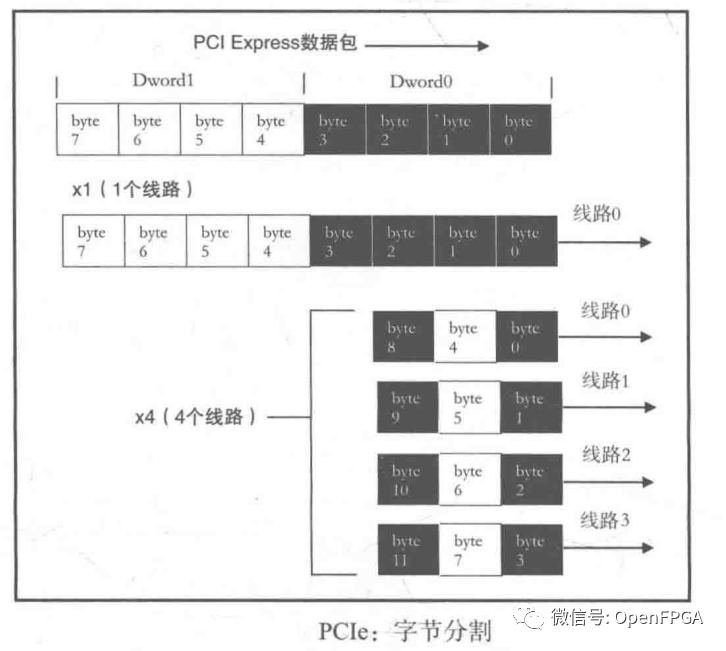

下面以PCIe为例对字节分割加以讨论,如图所示。

PCIe使用链路和线路来发送串行数据。链路是一个逻辑实体,能够具有单个线路或多个线路。当逻辑链路包括一个线路时,TLP和DLLP通过单一的线路发送,每次发送一字节。当链路包括多个线路时,TLP和DLLP分布在多个线路中,此时不是在不同的线路中发送不同的TLP而是所有的线路共同发送TLP在一个x4 PCIe链路(拥有4条线路)中,第一字节通过线路0、第二字节通过线路1、第三字节通过线路2、第四字节通过线路3、第五字节又回到线路0进行传输。这种传输机制被称为字节分割,字节分割在连续的线路上持续进行,直到最后一字节被发送。

正如我们所注意到的,可以通过使用更宽的链路来增加带宽。一个X4链路发送数据的带宽是xl链路的4倍。虽然线路是并行使用的,宽链路需要更多的引脚,其与并行总线结构也是有本质不同的。宽链路中每个独立的线路仍然是以串行方式工作的。每个线路都有自己的差分传输信号线和独立的数据恢复电路,都具有串行传输所具有的优点。它们是独立的串行传输通道,通过使用字节分割机制合并起来作为一个逻辑实休使用。字节分割是MAC的功能。但是并不是所有的串行协议都使用字节分割,SATA和USB没有使用字节分割技术。

如果希望增加SATA硬盘的传输带宽,需要使用多个相互独立的SATA驱动器,使用不同的事务层包 (FIS ) 进行通信,如图所示。USB也是采用类似的机制,每个USB设备采用单线路连接。

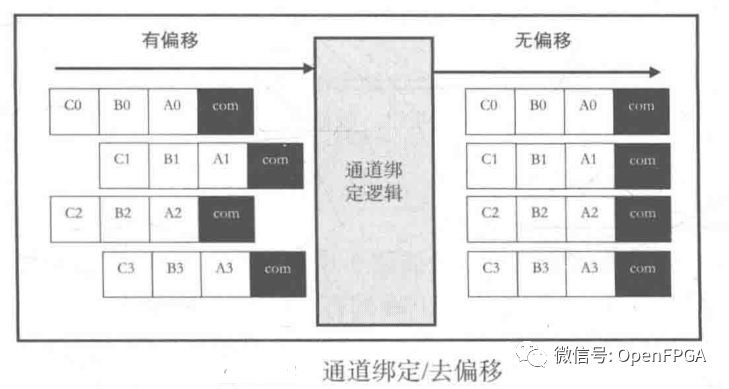

通道绑定与去偏移

前而我们讨论了字节分割技术,它将一个TLP分布到多个线路中进行传输。当接收电路从不同的线路收到这些分布传输的数据后,对其正确合路处理会遇到一些实际闲难,在电路板上,不同的传输路径会带来不同的传输延迟。当接收电路收到来自不同线路的数据时,它们 经过的延迟存在差异并且处于不同的时钟域。接收电路需要将不同线路上收到的数据进行级联,合并得到原始的TLP,此时所接收的数据之间已经失去了发送时相互之间的字节同步关系,需要使用通道绑定技术在接收端重新恢复不同线路之间的字节对准关系,如图所示。

在所有的线路上传输的数据流中有一种特殊的COMMA字符。在链路训练阶段,在所打线路上都会发送包含COMMA字符的用于训练的有序字符集合。与TLP和DLLP不同,训练字符集合不是以字节分割方式发送的。通道绑定逻辑在1个线路(例如,线路0)中査找COMMA,接着它在其他线路中定位COMMA字符并记录它们的相对位置。一旦它锁定了COMMA字符出现的位置,它就停止搜索COMMA字符并记录下这些相对位置信息。通道绑定逻辑使用这些相对位置信息来对准存在偏移的接收数据字节流。通道绑定逻辑会始终保持基线路(线路0)字节位置不变。对于其他线路,它会根据所检测到的COMMA的相对位置写入或读出数据,在此期间这些相对位置信息会保持不变。即使输入数据相对于通道绑定逻辑发生了延迟偏移,从通道绑定逻辑输出的数据仍然是对准的,TLP和DLLP能够被正确处理。通道绑定也被称为去延迟偏移操作。通道绑定逻辑通常属于MAC层功能,只应用于包含多个线路、采用字节分割技术的链路中。

在所有的线路上传输的数据流中有一种特殊的COMMA字符。在链路训练阶段,在所打线路上都会发送包含COMMA字符的用于训练的有序字符集合。与TLP和DLLP不同,训练字符集合不是以字节分割方式发送的。通道绑定逻辑在1个线路(例如,线路0)中査找COMMA,接着它在其他线路中定位COMMA字符并记录它们的相对位置。一旦它锁定了COMMA字符出现的位置,它就停止搜索COMMA字符并记录下这些相对位置信息。通道绑定逻辑使用这些相对位置信息来对准存在偏移的接收数据字节流。通道绑定逻辑会始终保持基线路(线路0)字节位置不变。对于其他线路,它会根据所检测到的COMMA的相对位置写入或读出数据,在此期间这些相对位置信息会保持不变。即使输入数据相对于通道绑定逻辑发生了延迟偏移,从通道绑定逻辑输出的数据仍然是对准的,TLP和DLLP能够被正确处理。通道绑定也被称为去延迟偏移操作。通道绑定逻辑通常属于MAC层功能,只应用于包含多个线路、采用字节分割技术的链路中。

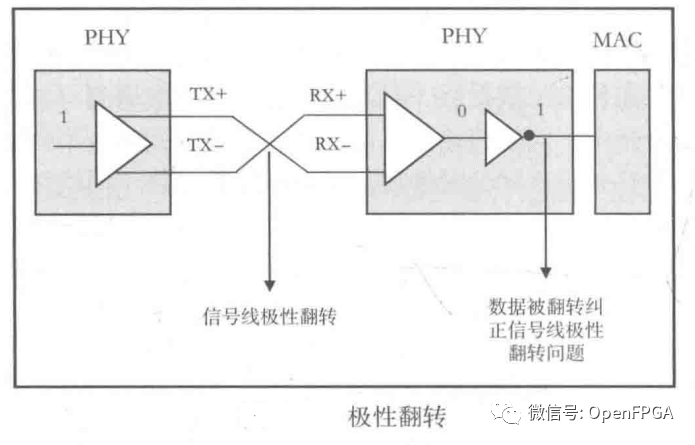

极性翻转

串行数据比特通过TX+和TX-信号线发送。信号线在印制电路板(PCB)上布线时,TX+应该连接收端的RX+,TX-应该连接收端的RX-。但随着PCB板的层数不断增加,布线密度不断增大,走线距离可能较长,有时还可能要通过连接器,所以经常因为疏忽而发生TX+连接收端的RX-、TX-连接收端的RX+的情况。发生这种情况后,有时可以通过重新布线加以解决,但有时重新布线的代价会比较高。

在PCIe中,使用了一种机制来解决极性连接错误问题。在链路训练阶段,接收端查找常规的训练练字符集合或者反相的训练字符集合。如果发生了极性翻转,那么接收的串行比特会发生逐比特翻转(1变为0,0变为1)。如果链路训练逻辑检测到了逐比特翻转的训练字符,那说明出现连线错误。发送电路无法获知是否发生了连接极性错误,接收电路检测到这一错误并通过逐比特取反在不进行硬件重新设计和PCB重新加工的情况下解决了这一问题,如图所示。

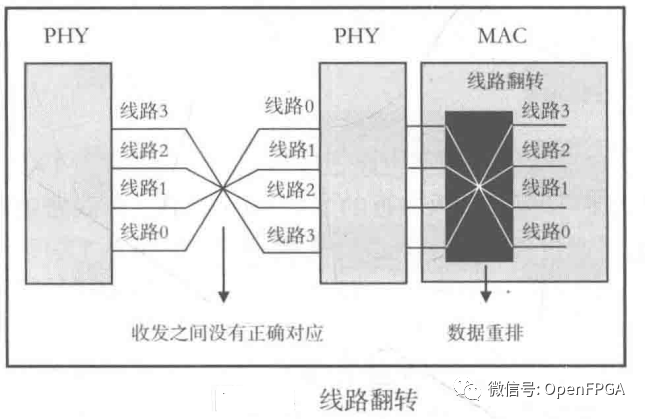

线路翻转

在多线路链路(例如,x8 PCIe有8条线路)中,数据包按照字节分割方式进行传输。所有的线路通过电路板连接到接收设备。正确的连接方式是TX线路0连接到RX线路0,TX线路1连接到RX线路1,以此类推。在实际设计和布线时,可能会因为疏忽造成收发之间没有正确对应的情况。这些线路在多层PCB上布线时,会在不同层次之间穿过,会进行90°弯曲,这些都可能导致连接失误。在某些情况下,常规连接会导致布线闲难,此时也会有意识地希望能够进行错序连接。PCIe采用了一种名为线路切换的技术来解决这种无意或有意的板级错 序连接。

如图所示,其基本思路是在链路训练过程中发现错序连接并进行数据重排。

属于一个链路的多个线路被编号为0、1、2、3、4、5、6、7等。当信号线两端试图发现线路编号时(在训练字符集中的特定区域内写入了所属线路的编号),它们各自都有期望的编号值。线路0希望收到的训练字符集合中的编号为0,线路7希望收到的编号为7。如果接收电路收到的编号与期望值不同,它会记录下来其实际连接的对端发送电路的编号。信号线两端的电路都可以根据实际连接的通道编号调整本端的实际编号,但需要注意的是,只能有一端可以进行调整,不能两端同时进行,否则会继续出错。双方选择的用于解决错序问题的一端在发送数据之前先要切换发送数据的通路(例如,线路0的数据切换到线路7上,线路7的数据切换到线路0上)。同时它还要切换接收通路RX通路0上的数据与通路7连接,通路7与通路0连接,剩余的通路依次切换)。正如我们所能看到的,这里没有逻辑修改,通过内部的连接重定位解决了板级连接存在的问题。

锁相环 PLL

PLL在数字系统中有很多应用,常见的典型重要应用如下:

-

数据时钟恢复(Clock Data Recovery,CDR)

-

去除时钟偏移

-

作为倍频器使用

CDR

在很多高速串行数据传输应用中,数据在传输过程中没有伴随着时钟的传输。然而,在数据流中存在着足够的数据跳变(0到1和1到0的跳变),接收端电路可以据此提取与数据同步的时钟。在接收端,可以使用参考时钟为时钟提取提供帮助。在没有参考时钟的情况下也 可以提取接收时钟的。下面我们将针对这两种情况对PLL电路加以讨论。

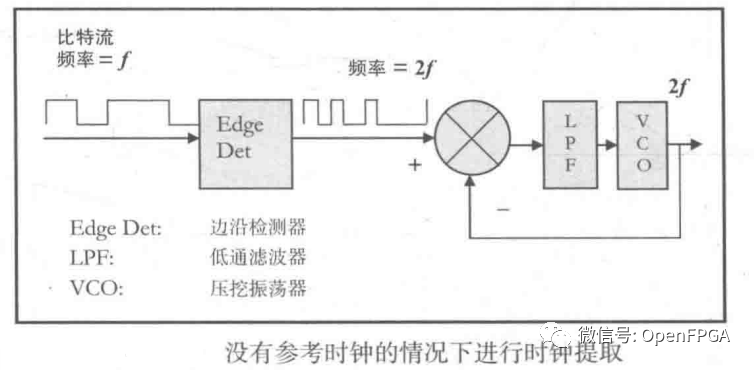

不带参考时钟的CDR(见下图)

如果接收端接收的比特流速率为f,那么接收端的边沿检测器检测到的数据跳变频率为2f,VCO产生的自由震荡时钟频率为2f。

如果接收端接收的比特流速率为f,那么接收端的边沿检测器检测到的数据跳变频率为2f,VCO产生的自由震荡时钟频率为2f。

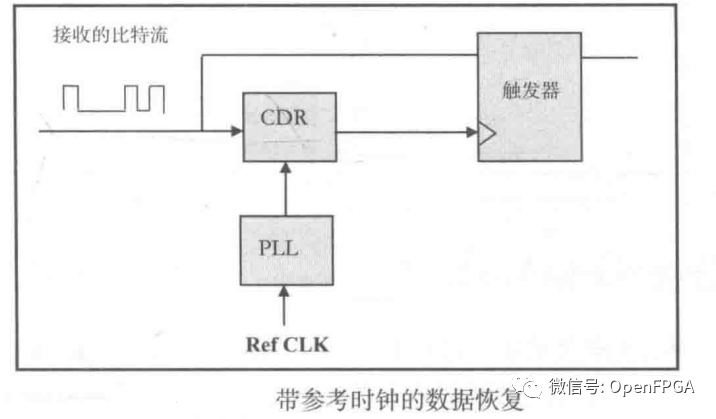

带参考时钟的CDR (见下图)

这种方式就不需要过多介绍,常见的传输方式。

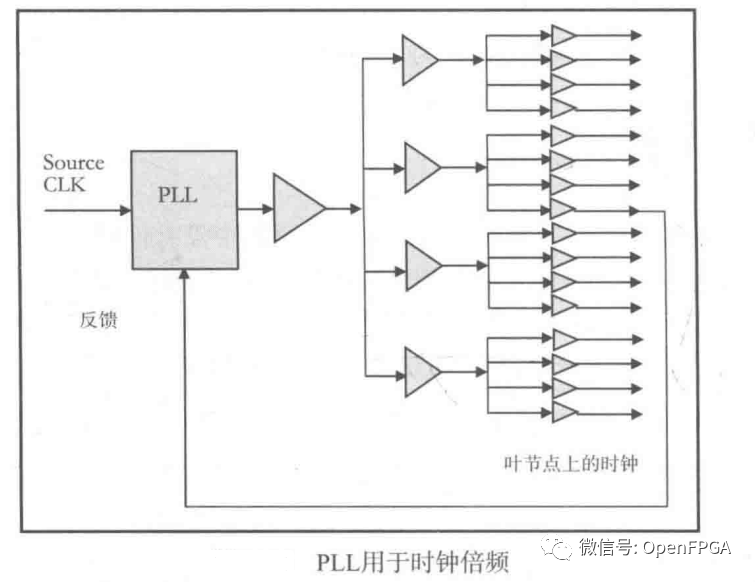

使用PLL去除时钟偏移

在SoC中,时钟树被用于将时钟信号分配给物理上分布在芯片各个区域的触发器。在时钟树的通路上,分布着带有延迟的驱动器。由于时钟分布路径上存在延迟,叶节点上的时钟与根节点上的时钟相比,存在相移(相位滞后)。此时,可以使用PLL消除叶节点上时钟的相移使之和根节点上的时钟相位对准,如图所示。

PLL还可用于产生与输人时钟存在指定相移的输出时钟,例如,产生和输入时钟存在90°相移的输出时钟。

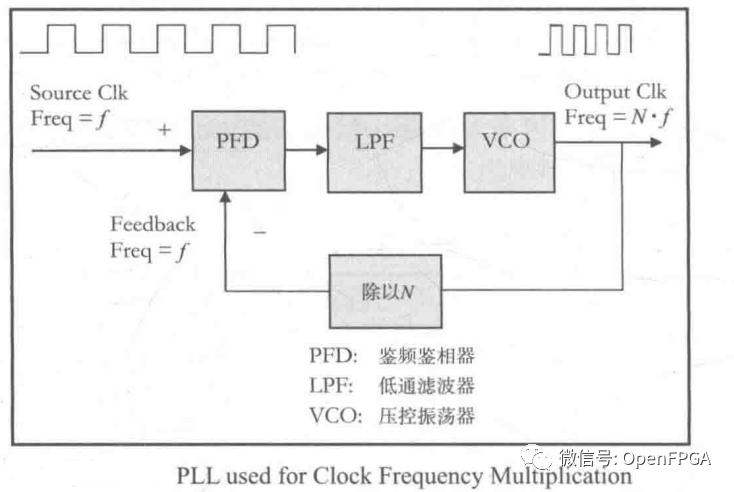

使用PLL实现倍频器

PLL可用于根据时钟源产生更高频率的时钟信号。将输岀时钟信号除以N作为PLL的反馈信号与时钟源相比较,可以得到N倍于时钟源的输出时钟信号,同时二者具有相同的相位。

串行总线的PMA层功能

PMA层主要实现模拟电路功能。PMA层电路也被称为SerDes(Serializer & Deserializer),是一个非常特殊的电路。我们的目标是从电路的系统设计层面对其加以介绍,以便对串行总线技术形成完整的理解。

发送均衡

采用串行传输机制时,数据以比特流的方式在差分对(TX+ TX-)上传输。在线路上传输的数据波形可以看成是大量不同频率、不同幅度的正弦波叠加作用的结果。

当数据速率很高时,存在一个占主导地位的高频正弦波分量。在高速传输时,差分传输线路的通路特性与低通滤波器(RC滤波器)接近,但相对于低频成分,高频成分的衰减更大一些。这意味着在接收端,接收信号中的不同的频率成分所占的比例与发送时不同。接收到的信号与发送端信号相比会发生畸变,造成ISI(码间串扰),这会使得CDR恢复的数据中存在误码。

什么是码间串扰?

如果我们发送一个阶跃函数波形(在一个时钟周期内为1的脉冲信号),在接收端波形会发生变化。接收脉冲会展宽并进入相邻时钟周期中。从第N个时钟周期展宽到第N+1个时钟周期的信号与第N+1个时钟周期的信号波形叠加,使得第N+1个周期内的波形发生畸变,这种畸变可能会造成对该时钟周期逻辑值的判决发生错误,这被称为符号间的串扰,即码间串扰(IS1)。

前有很多种技术可以解决传输线频率响应的问题。可以通过采用发送端均衡技术,或采用接收端均衡技术加以解决。

发送端预加重技术

发送驱动时,对高频成分的增益大于低频成分,频率越高增益越大。信号到达接收端时,所有的频率成分得到的总体增益相同。

发送端后加重技术

另一种技术是后加重技术。采用后加重技术时,边沿翻转(0到1或1到0)之后的比特被正常放大,但此后的其他比特(没有边沿翻转的比特)增益相对降低。由于信号的高频成分主要出现在信号翻转部分,这样做等效于为高频成分提供了更大的增益。当数据到达接收端时,所有比特位的最终等效增益是相同的。PCIe和SATA都使用了后加重传输技术。

接收均衡

在接收端,可以为高频成分提供相对于低频成分更大的增益。针对高频成分给予补偿的结果是整个传输系统为所有频率成分提供了相同的增益。经过补偿后,接收波形与发送波形更加相似。接收器均衡技术有利于减少1SI。

端接电阻

TX+和TX-信号是一对传输线,在发送端和接收端需要进行传输线阻抗匹配,以避免产生信号反射,使发送信号产生畸变。当信号发生反射时,它与原始的发送信号发生叠加,使发送信号增强或减弱。如果反射的信号强度较大,可能会使发送信号产生较大的畸变从而导 致接收错误。终端匹配的目的就是减少或消除接收端对发送信号的反射。

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思® UltraFast™ 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程

【Vivado使用误区与进阶】总结篇

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

SystemVerilog数字系统设计_夏宇闻 PDF

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

简谈:如何学习FPGA

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

AD936x+ZYNQ搭建收音机(一)

AD936x+ZYNQ搭建OpenWIFI

无招胜有招-Vivado非工程模式下的详细设计

面试中经常会遇到的FPGA基本概念,你会几个?

推荐一些可以获取免费的国外的原版书籍(电子版)网站

FPGA 的重构

国产CPU概括

从电子游戏历史看IC发展的助推剂

80年代电子游戏及电脑游戏的发展历史

PCIe总线的基础知识

万字长文带你回顾电子游戏的七十多年历史(完整版)

FPGA中异步复位,同步释放的理解

OpenFPGA系列文章总结

用Verilog设计一个16 位 RISC 处理器

介绍一些新手入门FPGA的优秀网站(新增)

Verilog数字系统基础设计-CR

Verilog数字系统基础设计-奇偶校验

建立和保持时间及时序简单理解

(Xilinx)FPGA中LVDS差分高速传输的实现

Xilinx Multiboot实例演示

高速串行通信常用的编码方式-8b/10b编码/解码

Verilog计时(微秒、毫秒和秒)脉冲的产生及同步整形电路

图书推荐|一本图像/视频处理的强大工具书

Verilog HDL-同步技术

再说System Verilog 与 Verilog 的关系

数模混合信号建模语言Verilog-AMS

Intel/Altera 系列FPGA简介

一块带给无数人年少欢乐的CPU,别说你没用过它

Verilog在编写第一行代码之前

【例说】Verilog HDL 编译器指令,你见过几个?

穿越时空的爱恋-Z80 CPU的前世今生

【Vivado】那些事儿-汇总篇

古老CPU启示录-晶体管之路

【Vivado那些事儿】约束的顺序

童年修复系列-SNES芯片组介绍及FPGA实现

优秀的 Verilog/FPGA开源项目介绍(二)-RISC-V

串行总线技术(一)-串行总线结构(以PCIe为例)

这篇关于串行总线技术(二)-串行总线中的先进设计理念及SerDes/PMA介绍的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!