fir专题

【MATLAB】FIR滤波器的MATLAB实现

FIR滤波器的MATLAB实现 FIR滤波器的设计fir1函数fir2函数 与IIR滤波器相比,FIR滤波器既有其优势也有其局限性。FIR滤波器的主要优点包括: 精确的线性相位响应;永远保持稳定性;设计方法通常是线性的;在硬件实现中具有更高的运行效率;启动传输仅需有限的时间。 然而,FIR滤波器也存在一些显著的缺点: 为了达到与IIR滤波器相同的性能要求,FIR滤波器通常需要

【FPGA数字信号处理】并行FIR滤波器

在数字信号处理领域,FIR(Finite Impulse Response)数字滤波器是一种非常重要的工具。它具有线性相位、稳定性好等优点,被广泛应用于通信、音频处理、图像处理等领域。 今天介绍一下并行 FIR 数字滤波器的原理以及实现。 一、FIR数字滤波器原理解析 1、数字滤波器 数字滤波器是数字信号处理领域的核心组件,它们对信号进行数学处理以增强或抑制某些特性。 数字滤波器按照

如何制作一个可以上传到fir.im的ipa文件(包含最新的Xcode打包方式)

1、拥有一个开发者账号(99美刀)2、登录苹果开发者网站,添加想要安装测试应用的设备的UDID,可以使用 fir.im 提供的的接口快速获取 UDID (fi r.im-工具-UDID获取工具)(1)添加UDID:Devices---All或者iPhoneimage1.png(2)+添加image2.png(3)Register Deviceimage3.png3、得到电脑的钥匙串左上角-钥匙串

自动化打包上传至 fir.im 蒲公英 pre.im

http://www.jianshu.com/p/b2337700b9be http://www.jianshu.com/p/b2337700b9be http://www.jianshu.com/p/b2337700b9be 自动化打包上传至 fir.im 蒲公英 pre.im 字数439 阅读167 评论0 喜欢1 蒲公英平台请移步http:/

FPGA - 滤波器 - FIR滤波器设计

一,数字滤波器 滤波器是一种用来减少或消除干扰的器件,其功能是对输入信号进行过滤处理得到所需的信号。滤波器最常见的用法是对特定频率的频点或该频点以外的频率信号进行有效滤除,从而实现消除干扰、获取某特定频率信号的功能。一种更广泛的定义是将具有能力进行信号处理的装置都称为滤波器。 滤波器的分类方法有很多种,从处理的信号形式来讲,可分为模拟滤波器和数字滤波器两大类。

IIR和FIR两种滤波器有什么区别?

概念的区分 IIR(Infinite Impulse Response,无限脉冲响应)和FIR(Finite Impulse Response,有限脉冲响应)滤波器是两种常见的数字信号处理滤波器类型,它们在结构、性能和用途上有显著区别: 结构差异: IIR滤波器具有反馈结构,即滤波器的输出不仅取决于当前和过去输入信号的值,还包括过去的输出信号。这意味着IIR滤波器的冲激响应永远不会完全衰减到零,

fir.im Weekly - 1000 Android 开源项目集合

冬天到了,适宜囤点代码暖暖身。本期 fir.im Weekly 收集了最近一些不错的 GitHub 源码、开发工具和技术实践教程类文章分享给大家。 codeKK — 集合近 1000 Android 开源项目 @Trinea 说道: codeKK 集合了近 1000 Android 开源项目,支持搜索。功能已经比较完善,超过国内外同类网站,可以正式对外了。支持: 每小时自动同步最新的开

iOS 自动打包-- fir.im

IOS的开发过程中,当需要给测试人员发布测试包的时候,直接使用xcode来做的效率是非常低下的。尤其是当有一点小改动需要重新出包时,那简直是个折磨的人的工作。 通过fir.im 可以轻松实现,具体操作如下: http://blog.fir.im/fir_cli/

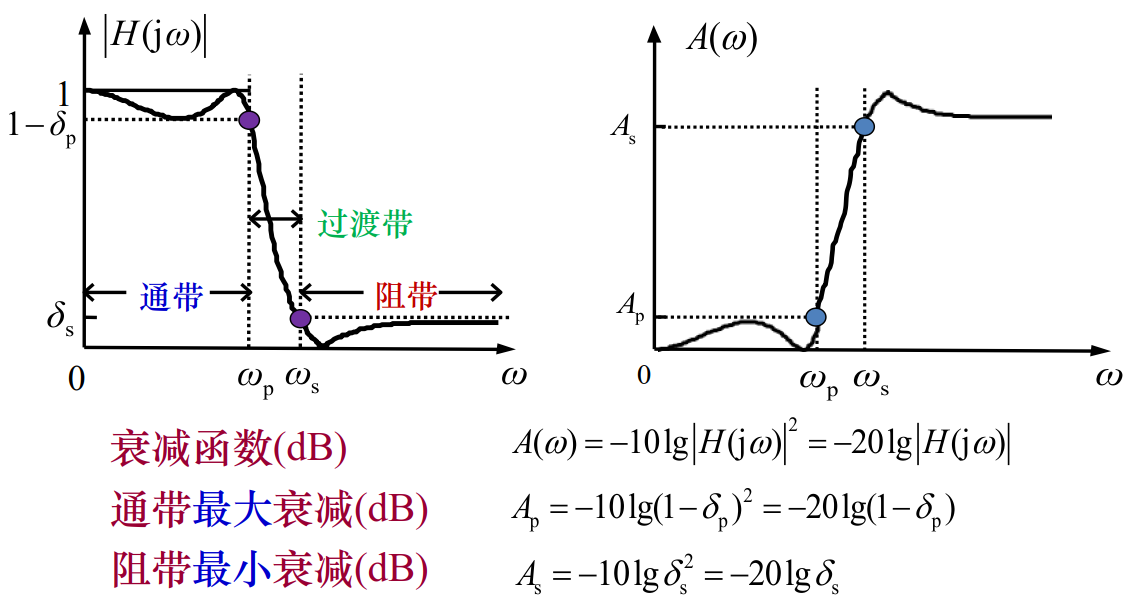

等波纹FIR带通滤波器的设计

等波纹FIR带通滤波器的设计过程可以分为以下几个步骤: 定义滤波器的特性:首先,需要确定FIR滤波器的设计参数,包括滤波器的截止频率、通带和阻带的要求等。这些参数将指导滤波器设计的具体过程。选择滤波器的长度:FIR滤波器的长度由滤波器的阶数(taps的数量)决定。阶数通常由滤波器设计的要求和计算能力等因素确定。设计滤波器系数:利用设计参数和选择的滤波器长度,可以使用不同的设计方法来计算FIR滤波

Scipy库中FIR滤波器的应用

在上一篇文章《Scipy库中IIR滤波器的应用》中,我们阐述了利用Scipy库进行IIR滤波器设计的一些基本做法。在这篇文章中我们将进一步总结Scipy库在FIR滤波器设计中1的应用。 1. FIR滤波器基本概念 在上篇文章中,我们在给出线性滤波器的差分方程喝系统函数的一般形式时指出FIR滤波器是一个无反馈的全零点型滤波器。设输入序列为 x n x_n xn,系数为 b m b_m b

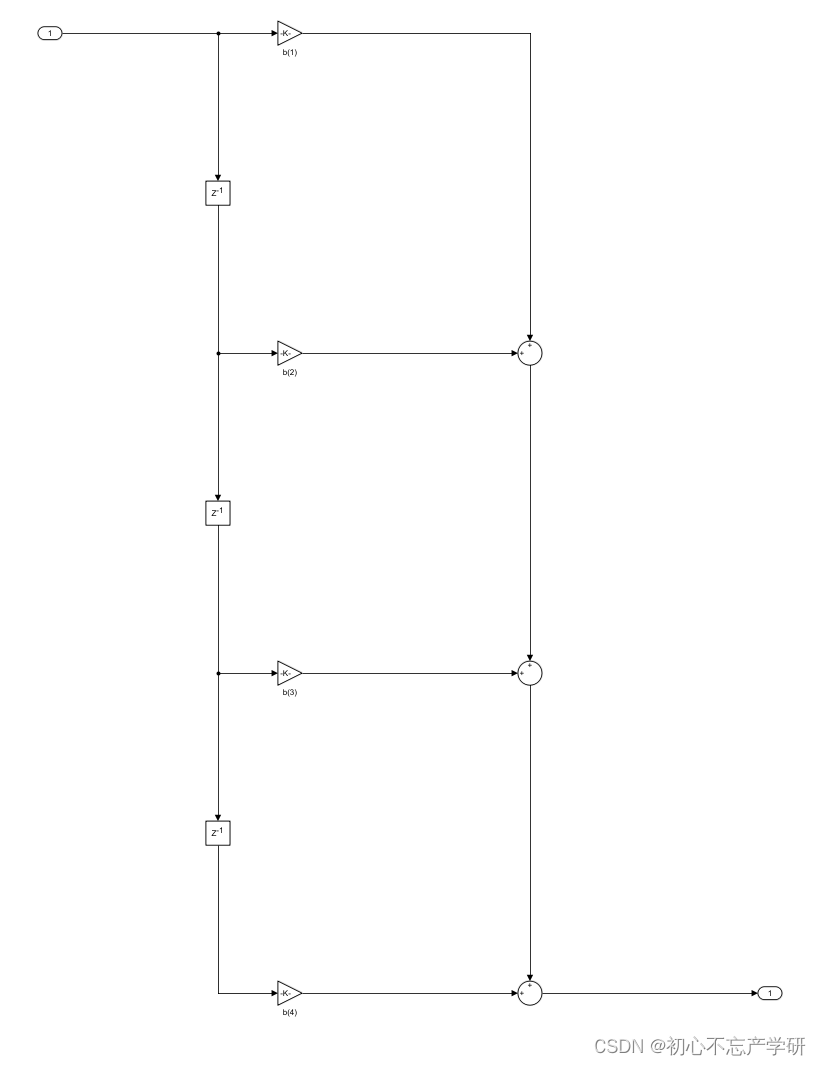

FIR滤波器抽头系数和冲激响应的关系

图1. FIR滤波器结构示意图 设输入序列为 x ( n ) x(n) x(n),抽头系数为 ω ( m ) \omega(m) ω(m),则输出序列可表示为 y ( n ) = ∑ m ω ( m ) x ( n − m Δ ) (1) y(n)=\sum_m \omega(m)x(n-m\Delta) \tag{1} y(n)=m∑ω(m)x(n−mΔ)(1) 其中,

【滤波器】基于matlab GUI高通+低通+带通+带阻FIR滤波器设计【含Matlab源码 699期】

⛄一、获取代码方式 获取代码方式1: 完整代码已上传我的资源: 【滤波器】基于matlab GUI高通+低通+带通+带阻FIR滤波器设计【含Matlab源码 699期】 点击上面蓝色字体,直接付费下载,即可。 获取代码方式2: 付费专栏Matlab信号处理(初级版) 备注: 点击上面蓝色字体付费专栏Matlab信号处理(初级版),扫描上面二维码,付费29.9元订阅海神之光博客付费专栏Matl

Jenkins+GitLab+Gradle+fir.im持续集成安卓

写在前面 最近一直搞Jenkins,各种坑,一步一个坑的弄,本人不是安卓开发,搜了很多的资料,总算是跑通了。。。 一、安装Gradle 下载地址: http://gradle.org/gradle-download/ 下载后,放在了 /usr/local/lib下 配置bash_prifile文件 vim ~/.bash_profile

Jenkins获取git提交记录并上传fir.im

写在前面 Jenkins持续集成就不多介绍了,用过的人都知道。 这里有个背景,fir.im上可以看到版本号,但是不知道每次版本都更新了什么,如果每次人为的添加更新记录,就违背了自动化持续集成的初衷。 自动化生成版本的时候,自动更新版本记录是一个很妙的体验。 一、寻找 浏览了各大论坛和网站,发现这个功能并不是有很多人需要,谈论者寥寥。 抱着不撞南

FDATool设计FIR低通滤波器

(一) 设计一个低通滤波器 采样频率 Fs = 50Hz Fpass = 10Hz Fstop = 20Hz 打开matlab,键入fdatool后,会弹出该工具的对话框。然后按照下图设置相关参数,参数列表中的Fs应该是采样频率,Fc是截止频率,即幅频特性曲线-3dB对应的频率。点击“Design Filter”后,幅频特性曲线会被更新。 Targe

切比雪夫逼近法设计FIR滤波器

切比雪夫逼近法设计FIR滤波器 概念 切比雪夫逼近法,是在所需要的区间[a,b]内,使误差函数E(x)=|p(x)-f(x)|较均匀一致,并且通过合理选择p(x),使E(x)的最大值En达到最小。切比雪夫最佳一致逼近的基本思想是,对于给定区间[a,b]上的连续函数f(x),在所有n次多项式的集合中,寻找一个多项式,使其在[a,b]上对f(x)的偏差和其他一切属于集合的多项式对f(x)的偏差相比

基于matlab通过多个FIR,IIR形成对violin信号进行均衡

基于《数字信号处理》这门课程的课程设计,特意写下这篇博客,仅供有需要的看官参考。 理论知识: FIR和IIR滤波器是数字信号处理中常用的滤波器类型。设计带通滤波器时,需要考虑滤波器的通带、阻带、过渡带等参数,以及滤波器的阶数、截止频率等设计参数。 FIR滤波器是一种无限脉冲响应滤波器,其基本理论是通过对输入信号的加权和延迟来实现滤波。FIR滤波器的特点是稳定性好、易于设计和实现。 IIR滤

FIR滤波器C语言代码

/********************************************************************************* 程序名称:FIR低通滤波器 ** 程序描述:50阶FIR低通滤波器,通过频率2500Hz,截止频率3000Hz ** 性能提升:** 程序版本:V1.0** 程序作者:syrchina** 最后修改:2011年8月1日

Jenkins自动打包 配置Jenkins环境,以及ipa包上传fir

Jenkins自动打包 Windows上配置Jenkins环境,我现在的需求是在一台Windows上部署Jenkins环境,然后配置一些节点,在其他机器上打包;今天终于算是搞定了(配置mac节点,打ipa包);因为Jenkins是基于Java开发的一种持续集成工具,所以若要安装Jenkins,必须安装Java环境JDK,地址:http://www.oracle.com/technetwork/ja

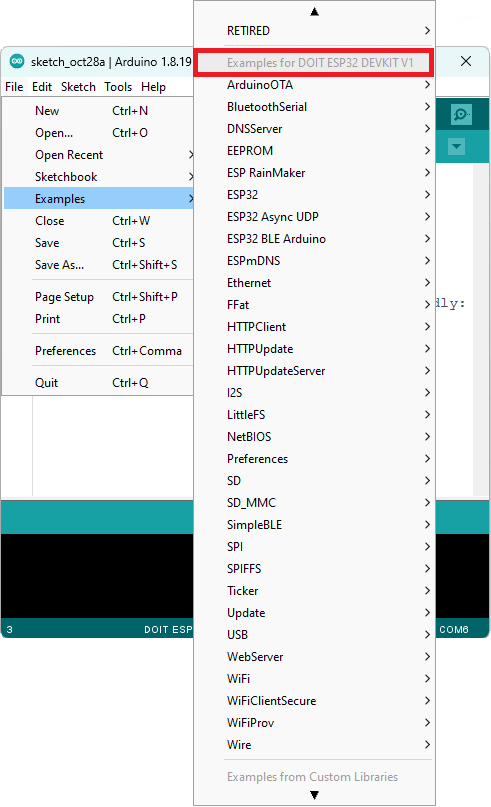

MATLAB_ESP32有限脉冲响应FIR无限脉冲响应IIR滤波器

要点 ESP32闪烁LED,计时LEDESP32基础控制:温控输出串口监控,LCD事件计数器,SD卡读写,扫描WiFi网络,手机控制LED,经典蓝牙、数字麦克风捕捉音频、使用放大器和喇叭、播放SD卡和闪存MP3文件、立体声网络广播、文字转语音、音频播放事件计数MATLAB设计离散时间信号,Z-变换和数字滤波器,有限脉冲响应FIR无限脉冲响应IIR滤波器,ESP32高级控制:正弦波发生器、使用 I

FIR和IIR去噪算法

文章目录 FIR—有限冲激响应滤波器概述FIR滤波器中的卷积对比 octave滤波器设计FIR滤波器设计audioread函数用法高频噪声和低频噪声的区别信号的频域分析——频谱、能量谱、功率谱、倒频谱、小波分析 汉明窗fir1函数FIR窗函数设计低通滤波器的设计三角窗(巴特利特Barlett窗)傅里叶变换波形图 IIR滤波器YUV颜色模型高斯噪声和椒盐噪声高斯白噪声中值滤波 F

Jenkins部署Android项目并上传fir平台及显示二维码下载

需求来源:项目提测后,修改完bug总是需要自己手动打包,然后上传到fir平台上再通知测试下载安装,浪费了时间和人力,因此我们可以把Android项目部署到Jenkins平台上,每次修改完bug后只需要在gitlib上提交下代码,然后通知测试即可。 Jenkins安装 下载地址:https://jenkins.io/zh/ 安装文档:https://jenkins.io/zh/doc/pi

FPGA数字频率合成器及fir滤波器设计(利用vivado dds、fir ip核)

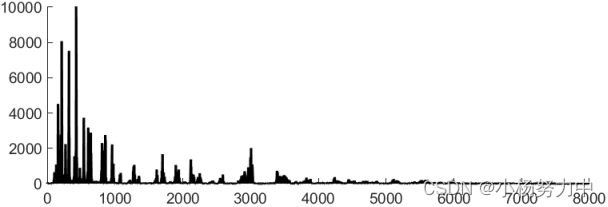

工作任务 1.逻辑使用200MHz时钟做参考,做一个DDS数字频率合成器产生1MHz、10MHz和50MHz的正弦波,然后相加得到一个三音正弦波形。\ 2.然后用MATLAB设计一个带通FIR滤波器,16bit量化,导出抽头文件,在FPGA上实现,对前面的三音信号进行带通滤波,滤掉1MHz和50MHz频率,得到一个10MHz的正弦波。\ 3.编写TestBench对工程进行仿真,并在米联客703

webrtc 中 FIR PLI 有何区别? 分别适用于什么场景

在WebRTC中,FIR(Full Intra Request)和PLI(Picture Loss Indication)是两种用于视频通信的控制消息,用于不同的场景。 FIR是一种请求全关键帧的控制消息。关键帧是视频序列中的特殊帧,它们不依赖于其他帧进行解码,而其他帧则依赖于关键帧进行解码。当接收端需要一个关键帧来进行解码时,它可以发送一个FIR消息给发送端,请求发送端发送一个关键帧。这在网络

fir.im Weekly - 2017 年必须了解的 iOS 开源库

2019独角兽企业重金招聘Python工程师标准>>> 放假的脚步临近,每个人都在期待一个愉悦的春节假期。最近,@张嘉夫 分享了一篇 Medium 上的文章《33 个 2017 年必须了解的 iOS 开源库》,总结了 2016 年最棒的 iOS 开源库;另外,@googdev 也分享了2016 Android Top 10 Library,假期无聊的时候看一看。预祝你的 2017 开发征

vivado FIR Filters

Vivado合成直接从RTL中推导出乘加级联来组成FIR滤波器。这种滤波器有几种可能的实现方式;一个例子是收缩滤波器在7系列DSP48E1 Slice用户指南(UG479)中进行了描述,并在8抽头偶数中显示对称收缩FIR(Verilog)。从编码示例下载编码示例文件。 8-Tap Even Symmetric Systolic FIR (Verilog) Filename: sfir