exams专题

CodeForces 492C Vanya and Exams

CodeForces 492C Vanya and Exams CodeForces 492C 题目大意: 有一位同学要参加N门科目的考试,每门科目的满分固定,现在这位同学为了拿到奖学金需要达到平均分S,这就需要它在原来的基础上对某些科目的分数进行提升,然后提升每门科目需要做Ai个测试,于是希望能够做尽量少的测试能够使得分数达到平均分。 解题思路: 将所有的科目按照对应的测试数进行排

Codeforces 479C Exams(贪心)

题目链接:Codeforces 479C Exams 题目大意:期末考试了,有个人希望尽快考完所有的科目,于是和每个科任老师单独沟通,最后每个科任老师愿意给额

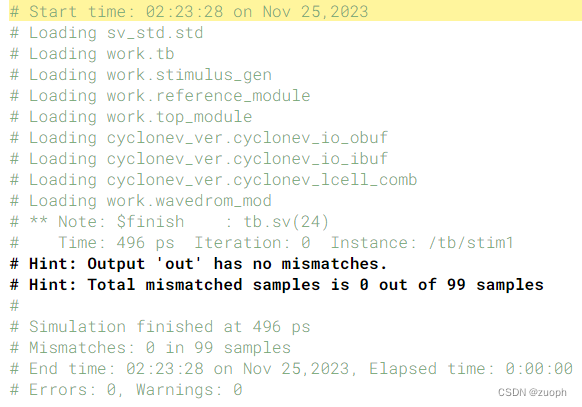

HDLbits 刷题 -- Exams/m2014 q3

Consider the function f shown in the Karnaugh map below. Implement this function. d is don't-care, which means you may choose to output whatever value is convenient. 译:考虑下面卡诺图中显示的函数f。 实现这个函数。D是

HDLbits 刷题 --Exams/m2014 q4i

Implement the following circuit: 实现以下电路: module top_module (output out);assign out = 1'b0;endmodule 运行结果:

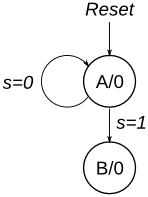

Exams/2014 q3fsm_HDLbits详解(merely状态机典型例题)

merely状态机例题 1、Consider a finite state machine with inputs s and w. Assume that the FSM begins in a reset state called A, as depicted below. The FSM remains in state A as long as s = 0, and it moves t

hdlbits系列verilog解答(exams/m2014_q4f)-47

文章目录 一、问题描述二、verilog源码三、仿真结果 一、问题描述 实现以下电路: 二、verilog源码 module top_module (input in1,input in2,output out);assign out = in1 & (~in2);endmodule 三、仿真结果 转载请注明出处!

hdlbits系列verilog解答(exams/m2014_q4g)-48

文章目录 一、问题描述二、verilog源码三、仿真结果 一、问题描述 本次我们将一次创建多个逻辑门,对两个输入a和b通过组合逻辑实现七种不同的输出: out_and: a and bout_or: a or bout_xor: a xor bout_nand: a nand bout_nor: a nor bout_xnor: a xnor bout_anotb: a

Exams/ece241 2014 q7a(Counter1-12)

项目场景: Design a 1-12 counter with the following inputs and outputs: Reset Synchronous active-high reset that forces the counter to 1 Enable Set high for the counter to run Clk Positive edge-triggered

[HDLBits] Exams/2014 q3bfsm

Given the state-assigned table shown below, implement the finite-state machine. Reset should reset the FSM to state 000. Present state y[2:0]Next state Y[2:0]Output zx=0x=1000000001000100110000100100

[HDLBits] Exams/2012 q2fsm

Consider the state diagram shown below. Write complete Verilog code that represents this FSM. Use separate always blocks for the state table and the state flip-flops, as done in lectures. Describe

[HDLBits] Exams/2014 q3fsm

Consider a finite state machine with inputs s and w. Assume that the FSM begins in a reset state called A, as depicted below. The FSM remains in state A as long as s = 0, and it moves to state B when

HDLbits:Exams/ece241 2013 q4

本题是一个实际的应用问题,一个水库,有三个传感器S1、S2、S3提供输入,经过控制电路,四个输出给到四个流量阀。也就是说,本题想让我们根据水位去控制流量阀。 问题的关键在于把什么抽象成state,答案是:水位的高低。根据题意,我们知道水位高低有四种状态,可以用传感器检测。 在第一个always块中,把三个传感器输入的值,作为next_state。 在第二个always块中,用next_sta

HDLbits:Exams/ece241 2013 q4

本题是一个实际的应用问题,一个水库,有三个传感器S1、S2、S3提供输入,经过控制电路,四个输出给到四个流量阀。也就是说,本题想让我们根据水位去控制流量阀。 问题的关键在于把什么抽象成state,答案是:水位的高低。根据题意,我们知道水位高低有四种状态,可以用传感器检测。 在第一个always块中,把三个传感器输入的值,作为next_state。 在第二个always块中,用next_sta

HDLbits: ece241 2013 q12 // Exams/m2014 q4k

两道题目,有一样的问题: 第一道:ece241 2013 q12 下面的代码错误,一直没看出来哪里有问题: module top_module (input clk,input enable,input S,input A, B, C,output Z ); reg [7:0] q;dff dff_1(clk,enable,S,q[0]);dff dff_2(clk,enable,q[0]

![[HDLBits] Exams/2012 q2fsm](https://img-home.csdnimg.cn/images/20230724024159.png?origin_url=https%3A%2F%2Fhdlbits.01xz.net%2Fmw%2Fthumb.php&pos_id=94bTcSqZ)