ddr4专题

【xilinx】Versal Soft DDR4 内存控制器 - XCVP1902-2M 速度等级设备上某些存储体的时序收敛问题

描述 当在 XCVP1902 设备上使用软核内存控制器时,如果速度等级为 -2M,目标 Fmax 为 2933 Mbps,某些设计可能无法满足某些存储体的时序要求。 解决方案 如果软核存储控制器使用 SLR0 中的存储体 704/707、SLR3 中的存储体 714/719、SLR1 中的存储体 804/807 或 SLR2 中的存储体 814/819,那么时序收敛可能会很困难。

【DRAM存储器三十九】LPDDR4/DDR4的时序训练相关内容之读方向的训练

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光LPDDR4数据手册》 、《JESD209-4B》 跟写操作一样,一切跟读相关的训练都可以归结为read leveling,包括如下内容: read DQS gate training 我们知道控制器读DDR的时

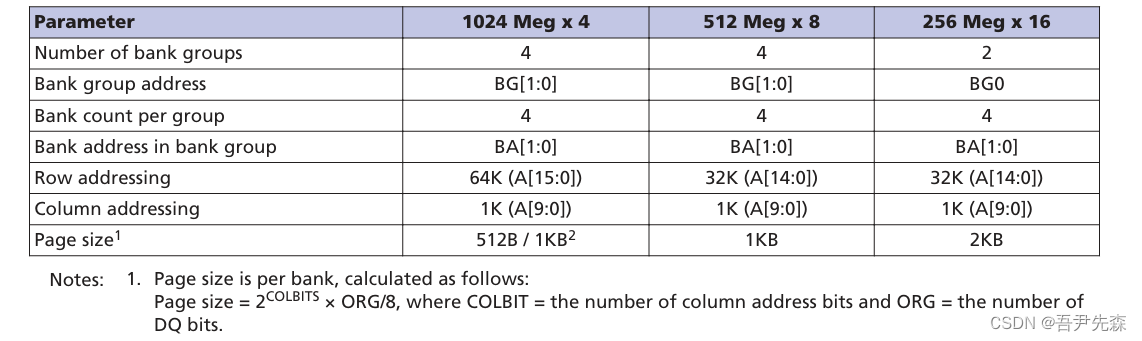

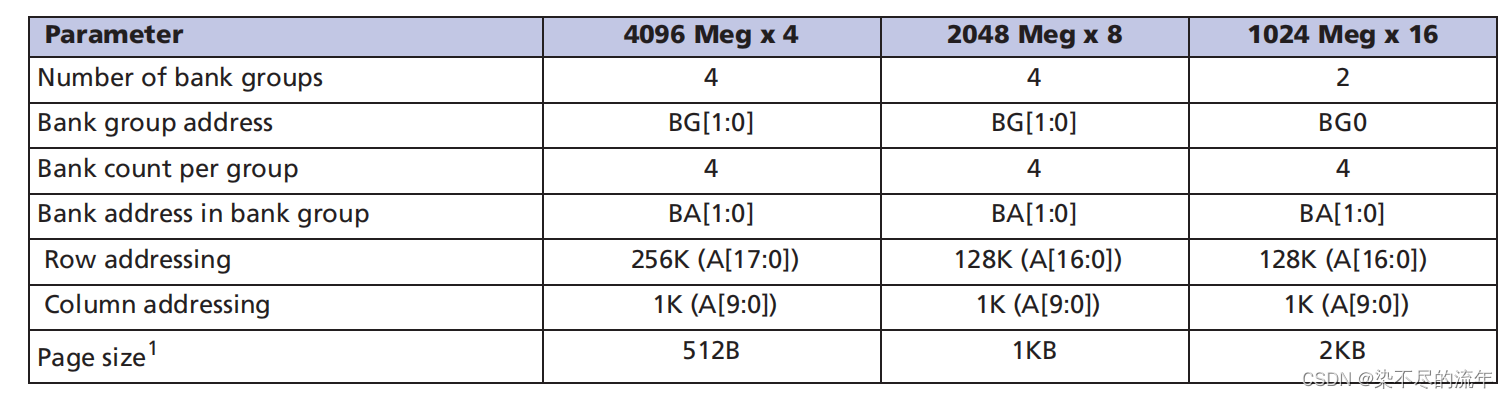

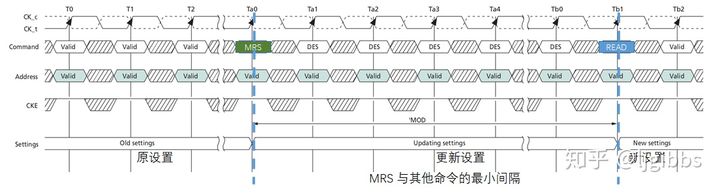

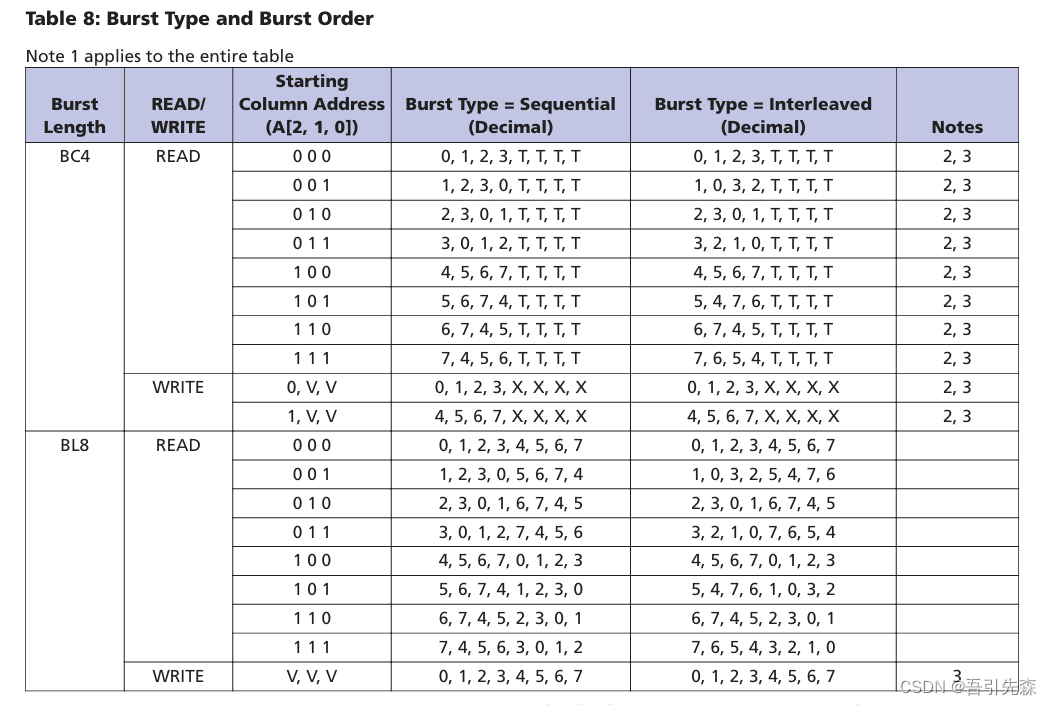

关于FPGA对 DDR4 (MT40A256M16)的读写控制 3

关于FPGA对 DDR4 (MT40A256M16)的读写控制 3 语言 :Verilg HDL 、VHDL EDA工具:ISE、Vivado、Quartus II 关于FPGA对 DDR4 (MT40A256M16)的读写控制 3一、引言二、DDR的功能性描述三、SDRAM设备中模式寄存器的可编程性四、重要的模式寄存器之MR0(1) Burst Length、Type、Ord

[DDR4] DDR1 ~ DDR4 发展史导论

依公知及经验整理,原创保护,禁止转载。 专栏 《深入理解DDR4》 内存和硬盘是电脑的左膀右臂, 挑起存储的大梁。因为内存的存取速度超凡地快, 但内存上的数据掉电又会丢失,一直其中缓存的作用,就像是我们的工作桌面, 而硬盘就像是仓库,各自扬长避短。 内存技术一直在发展, 从早期的SIMM 到 DDR, 再在 DDR 上不断子迭代, DDR1 -> DDR2 -> DDR3 -> DDR4

[DDR4] 总目录 学习路线

依公知及经验整理,原创保护,禁止转载。 传送门: 总目录 目录 基础篇 1-1 DDR4 发展历史 1-2 DDR4 和 DDR3 差异与优势 1-3 DDR4 内部结构 1-4 DDR4 工作原理 协议篇 2-1 DDR4 引脚 设计篇 实践篇 进阶篇 学习路线: 了解DDR4的基本知识: 了解DDR4的发展历史和特点,包括其相比DDR3的改进和优势。 理解DDR4的内部结

关于FPGA对 DDR4 (MT40A256M16)的读写控制 I

关于FPGA对 DDR4 (MT40A256M16)的读写控制 I 语言 :Verilg HDL EDA工具:ISE、Vivado 关于FPGA对 DDR4 (MT40A256M16)的读写控制 I一、引言二、DDR4的特性(MT40A256M16)(1) 电压和电源管理(2)内部参考电压生成(3) 命令/地址延迟(CAL)(4)写入均衡 (Write Leveling)(5)

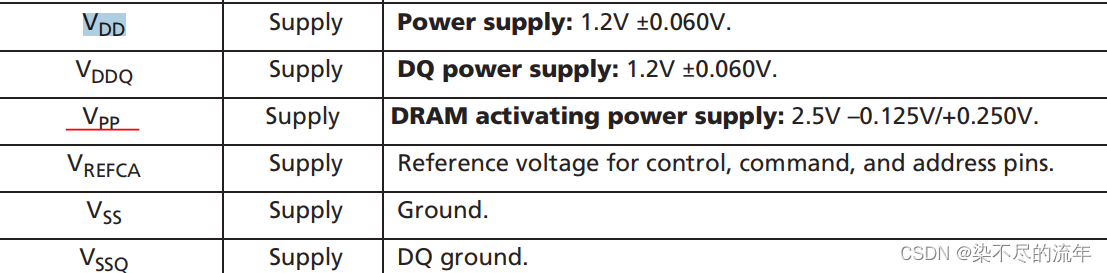

DDR4 新功能介绍

DDR4(第四代双倍数据率同步动态随机存取内存)相较于其前代DDR3,引入了一些新的功能和改进,这些新功能有助于提高内存的性能、降低功耗以及增强系统的可靠性,包括VPP、DBI(Data Bus Inversion,数据总线翻转)和DMI(与LPDDR4相关)。以下是对这些功能的简要说明: 更高的数据传输速率和带宽: DR4的起始频率是2133 MT/s,相较于DDR3的起始频率更高。此外,

【专篇】DDR4 SDRAM-01总体介绍

概念 DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory)是一种先进的高性能存储器规格,是DDR3 SDRAM的后续产品。自2011年首次由三星电子制造并公布以来,它已经成为现代计算机系统中广泛采用的内存标准。 主要特点: 更高带宽: DDR4提供比DDR3更高的数

【DRAM存储器二十八】DDR4介绍-DDR4 SDRAM的主要技术特性之ODT,为什么要新增RTT_PARK?

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光DDR4数据手册》 、《JESD79-4B》 ODT DDR4的ODT相对DDR3又有更新。我们从DDR2到DDR4一起回顾一下。DDR2的终端电阻为RTT(NOM),由EMR的EMR的bit2和bit6进行设置:

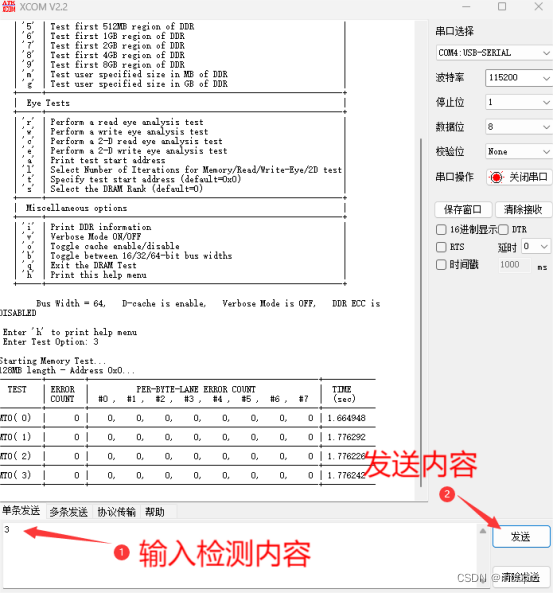

TQ15EG开发板教程:在VIVADO2023.1 以及VITIS环境下 检测DDR4

打开VIVADO2023.1 创建一个新的工程,设置工程名称和地址 选择RTL工程,勾选不添加文件 搜索15eg,选择xqzu15eg-ffrb1156-2-i 完成创建工程 添加设计模块 设置模块名称 在模块中添加mpsoc器件 双击器件进行配置 若有配置文件预设可以直接导入配置 选择 .tcl 预设文件导入即可 具体配置

15EG在VIVADO2023.1 以及VITIS环境下 检测DDR4

打开VIVADO2023.1 创建一个新的工程,设置工程名称和地址 选择RTL工程,勾选不添加文件 搜索15eg,选择xqzu15eg-ffrb1156-2-i 完成创建工程 添加设计模块 设置模块名称 在模块中添加mpsoc器件 双击器件进行配置 若有配置文件预设可以直接导入配置 选择 .tcl 预设文件导入即可 具体配置

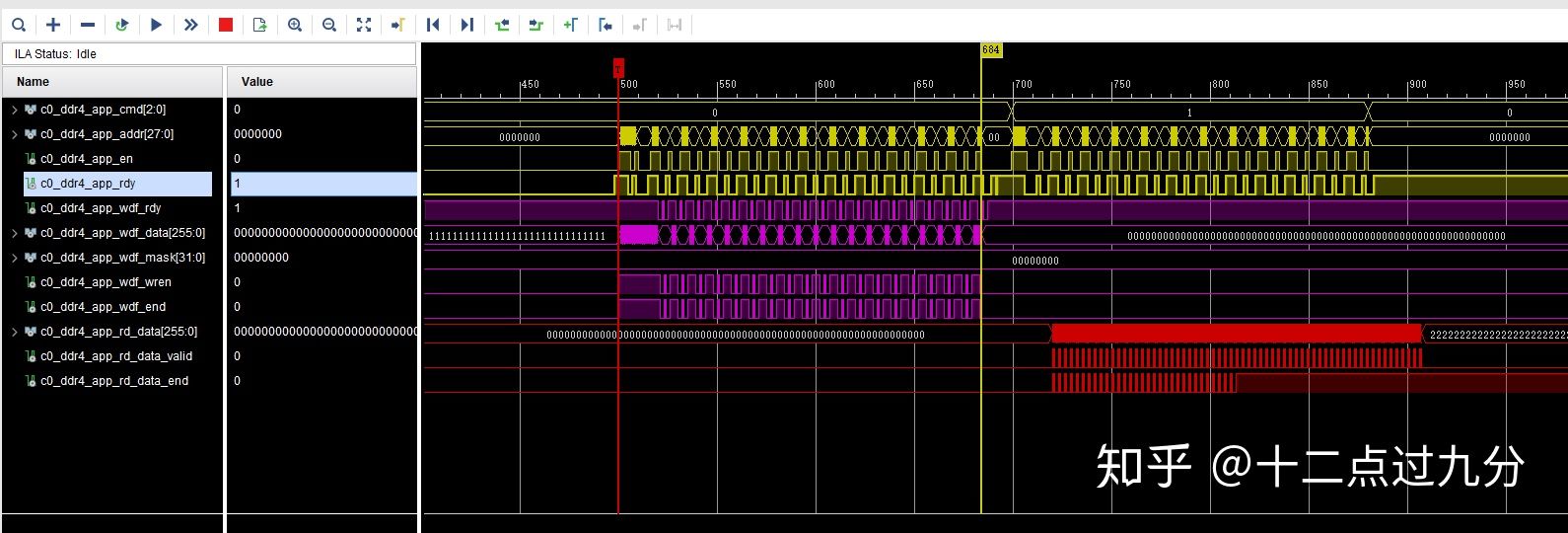

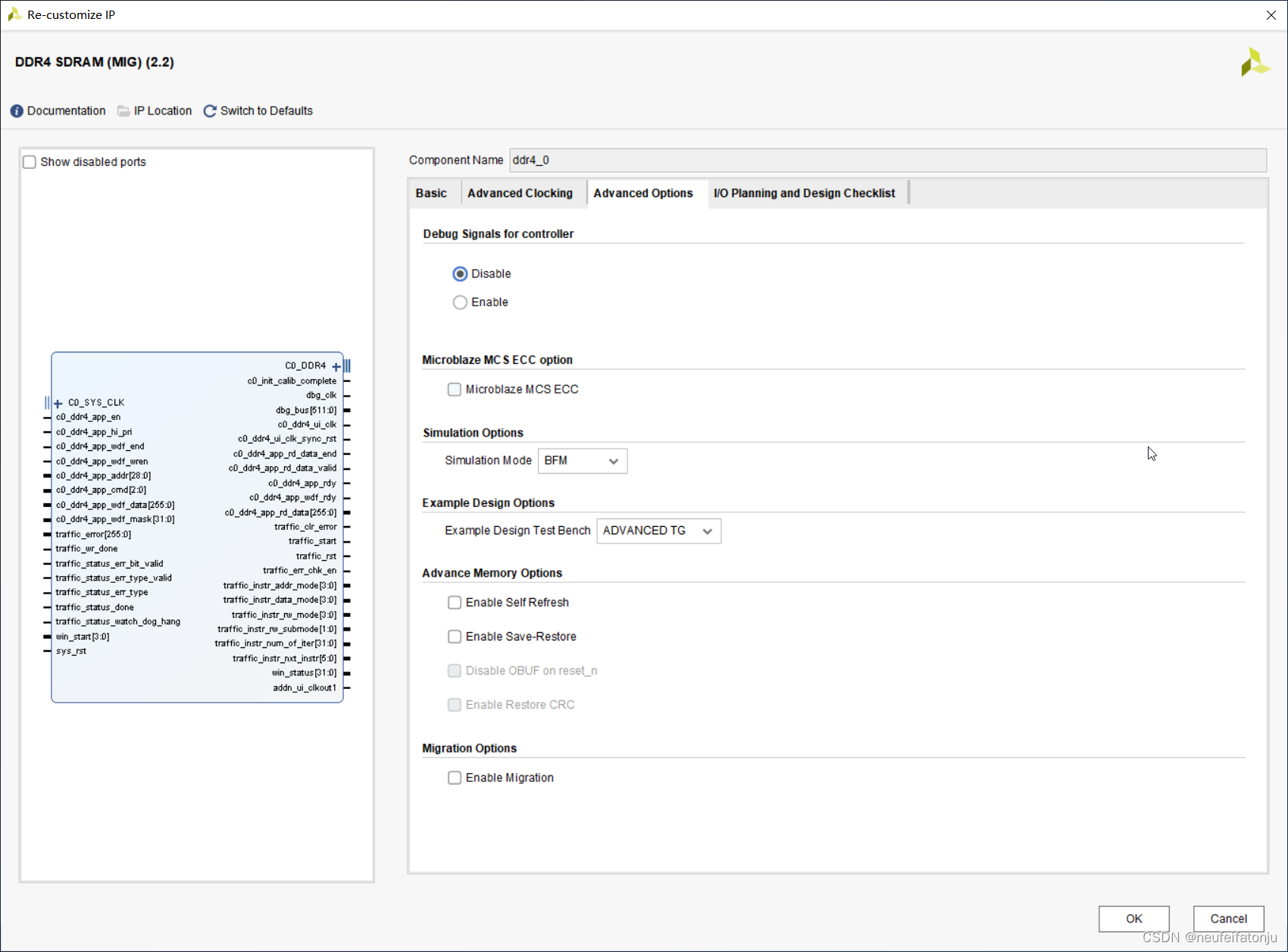

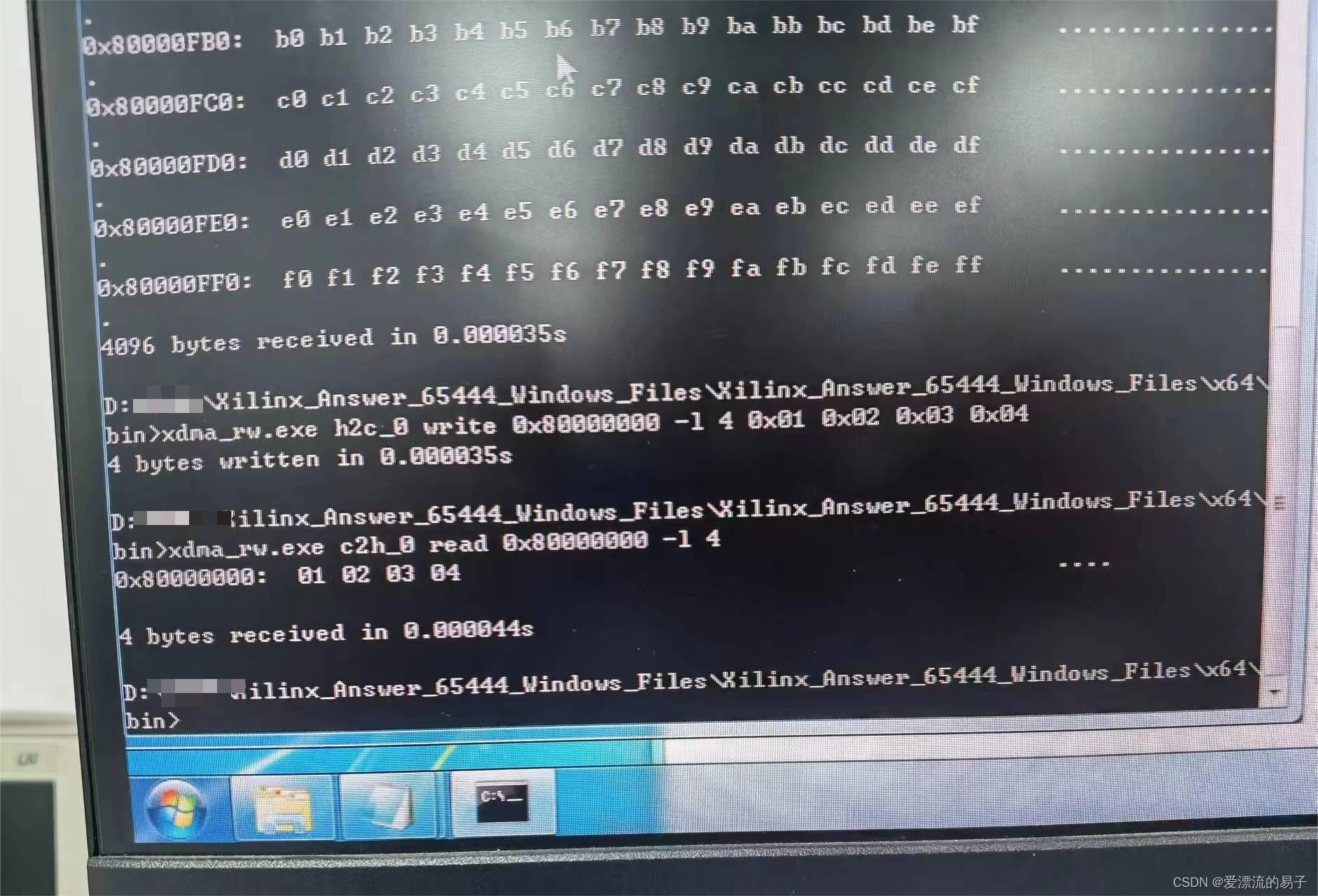

DDR4读写测试(二):基本读写测试

上次基本讲了怎么配置MIG的IP,这次继续翻译手册PG150,根据其提供用户端的app接口的读写模式,针对每种模式进行最基本的读写测试。 MIG核用户app接口信号定义 写RTL前需要了解些什么? 还需了解什么?知道个app接口定义不就好了???? 但似乎在(一):MIG IP核配置中并未提地址的事情,所以本文再探讨下地址的问题。 我们知道,一个RAM中一个地址对应存储一个数据。

Xilinx DDR4 MIG 的调试

平台:Vivado2021.1 芯片:xcku115-flva1517-2-i (active) 语言:VerilogHDL 参考文件:pg150.下载地址 pg150-ultrascale-memory-ip.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com) DDR4介绍 DDR4,即第四代双倍数据率同步动态随机存储器SDRAM。前面我们学习过DDR3,D

lx2160 DDR4调试

硬件配置:5颗ddr4,其中一颗作为ecc。 DDR问题会导致uboot无法加载运行。所以RCW配置完后最重要的就是调试DDR。首先检查ddr硬件上的设计,DQ信号设计应该是4位交叉(swap),主要原因是CW软件DQ mapping是按照4位配置的,没有8位的swap配置,如果硬件不是按照4位swizzled的,ddr的参数校准会通不过。我们的项目第一版即使因为硬件DQ信号是按照8位设计的,D

入手DDR5内存最佳时机到了,价格大跳水香过DDR4

当时 DDR5 内存刚出来那会儿大家怎么说的来着,售价离谱,提升微弱,鬼都不买… 不过嘛,随着 13 代酷睿以及锐龙 7000 系 CPU 上市,DDR5 彻底真香起来了。 先不说花重金升级 13 代酷睿平台,还用 DDR4 会不会有一种逼格差一截儿的感觉; 光锐龙 7000 平台直接不支持 DDR4,来了波强推 DDR5。 最重要的是,经过市场 DDR5 内存需求提升,对

64G超大容量内存条599,光威天策DDR4 32×2原地起飞

- 光威天策DDR4 64G套装,599元享受极速体验 - 599元升级64G内存,光威天策DDR4给你惊喜 - 光威天策DDR4 64G内存条,简约外观,强劲性能 - 超值618,光威天策DDR4 64G内存条,速度快,散热好 很多热爱电子游戏的朋友,都喜欢DIY主机,毕竟3A大作对电脑的性能要求可不低,品牌机常见的16G的内存条完全不够用,对2077之类的大制作来说,就像一块小饼干,一口就吃

DDR4技术原理详解

DDR4是DDR4-SDRAM的简写,即第4代DDR-SDRAM,DDR-SDRAM全称Double Date Rate Synchronous Dynamic Random Access Memory。本文重点解析DDR4技术规范及其背后的电子电路原理,以及编程使用DDR4过程中需要注意的性能事项。 DDR4数据存储原理 DDR4是从最初的DRAM逐步进化迭代而来,从DRAM到SDRAM、D

DDR4 SDRAM - Understanding Timing Parameters

引言 Introduction 在 DDR 标准中有很多很多时序参数(timing parameter),但当你真的和 DDR4 打交道时,会发现经常访问或者读到的参数也就那么几个,它们相比剩下的参数要常用许多。所以,本文将基于具体的 DDR 命令,讨论那些经常用到的参数。 这些命令真的很容易忘记,一段时间不怎么用到后,记忆就会马上模糊。本系列的另一篇文章:Timing Parameter C

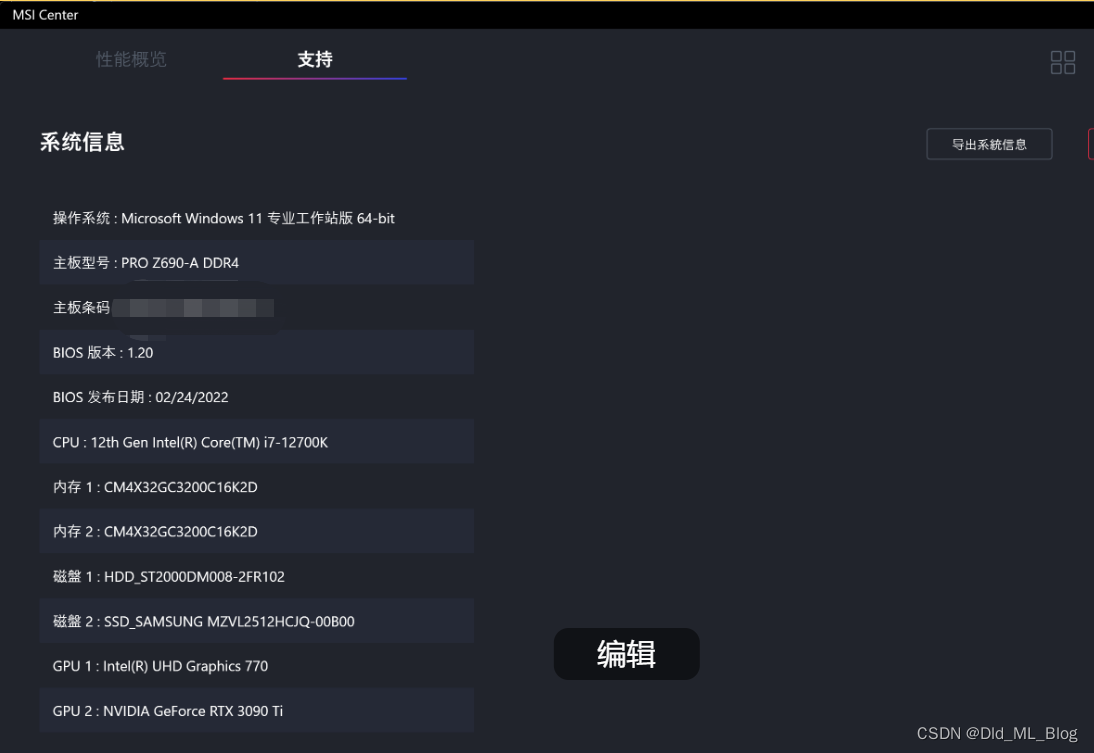

解决MSI Z690-A DDR4+win11 开机唤醒死机+随机死机问题 案例

状况描述: 将系统从win10升级到win11后,系统频繁随机卡死,需要强制重启。且睡眠状态下,会随机 无用方案: 将win11升级到专业工作站版、更新显卡驱动、更新除了bios外的所有驱动。 状况依然存在。 最终方案: 这个死机问题,实际是内存问题导致的。 win11下 开机按delete进入bios,内存电压改成默认(这一步不知道具体是否有决定作用),有一个Memory Try

![[DDR4] DDR1 ~ DDR4 发展史导论](https://img-blog.csdnimg.cn/direct/8d31fad7a28745eb81e253606f226423.png#pic_center)