本文主要是介绍DDR4技术原理详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

DDR4是DDR4-SDRAM的简写,即第4代DDR-SDRAM,DDR-SDRAM全称Double Date Rate Synchronous Dynamic Random Access Memory。本文重点解析DDR4技术规范及其背后的电子电路原理,以及编程使用DDR4过程中需要注意的性能事项。

DDR4数据存储原理

DDR4是从最初的DRAM逐步进化迭代而来,从DRAM到SDRAM、DDR、DDR2、DDR3,最后到DDR4,其背后的数据存储原理始终未变。DRAM作为存储器,其本职功能是存储数据,即计算机世界中的0/1数据,那么DDR又是如何存储0/1数据呢?

DRAM基本单元:cell

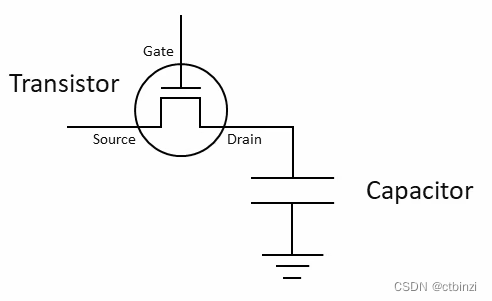

DRAM的数据存储策略是电容,电容存储了电量代表1,电容放空电量代表0,同时使用一个晶体管作为电容的充放电开关,以便实现1bit数据的读写,如下图:

当要读取 cell 的存储值,首先打开电子开关(即晶体管),然后根据电容的充放电信息获得存储值。如果 cell 保存“ 1 ”,即电容存有电荷,那么当打开开关,电容就会放电;如果 cell 保存“ 0 ”,即电容不保存电荷,那么打开开关之后电容不会放电。

当要向 cell 中写入值,仍然先打开电子开关,然后在电子开关的另一侧施加电压。如果要写入“ 1 ”,则施加高电压,此时电流会通过晶体管向电容充电;如果要写“ 0 ”,则让电子开关另一端接地。施加电压一段时间后即可断开开关,此时 cell 已经保存好写入值,因为电容很小,所以施加电压的时间会很短。

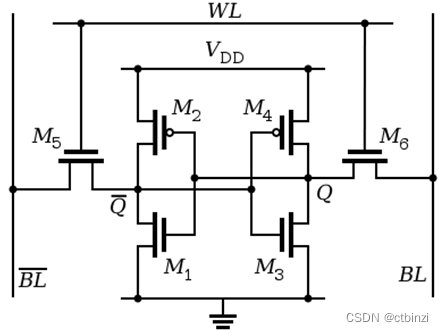

一个题外话,SRAM和DRAM同作为可读写存储器,采取了完全不同的数据存储策略,如下图:

其工作原理不是本文讨论方向,留给读者自行分析。

另外,你还知道其他数据存储策略吗?欢迎评论区留意告诉我!

cell阵列

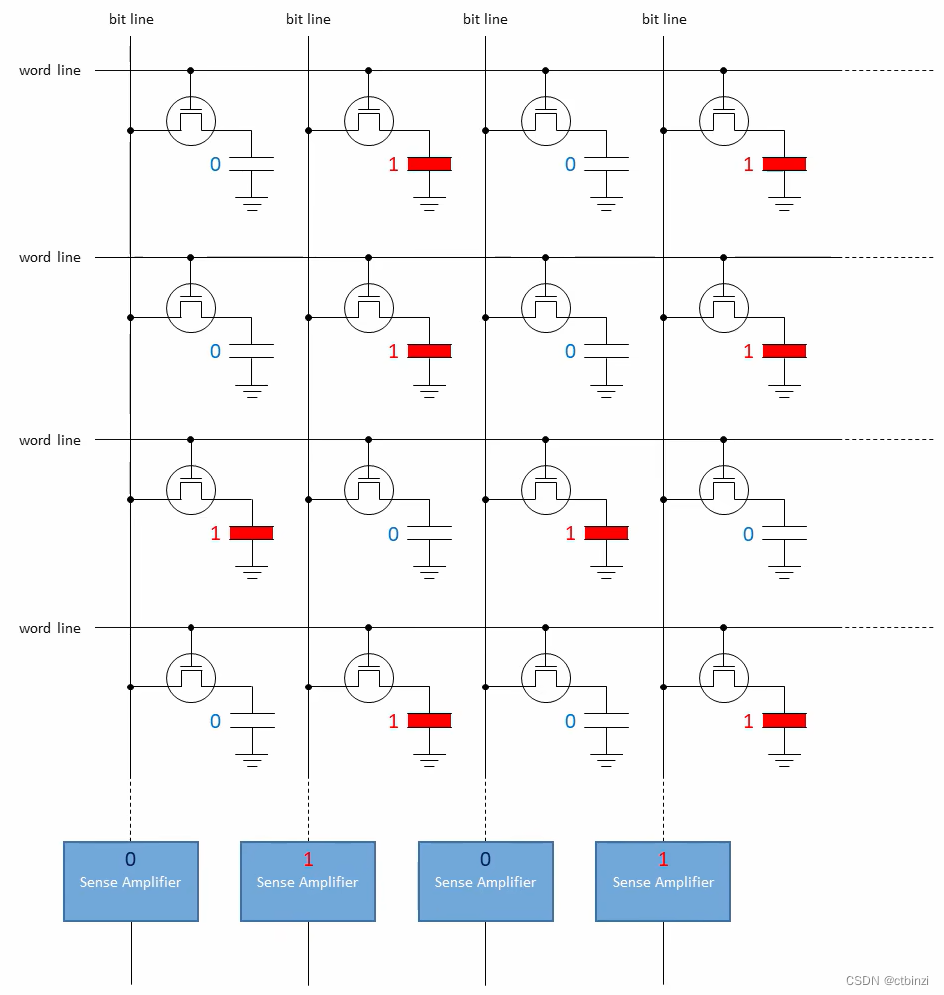

如前文所述,DRAM的一个 cell 只能存储一比特信息,即“ 0 ”和“ 1 ”,为了存储大量信息,DRAM采取了 cell 阵列策略。如下图:

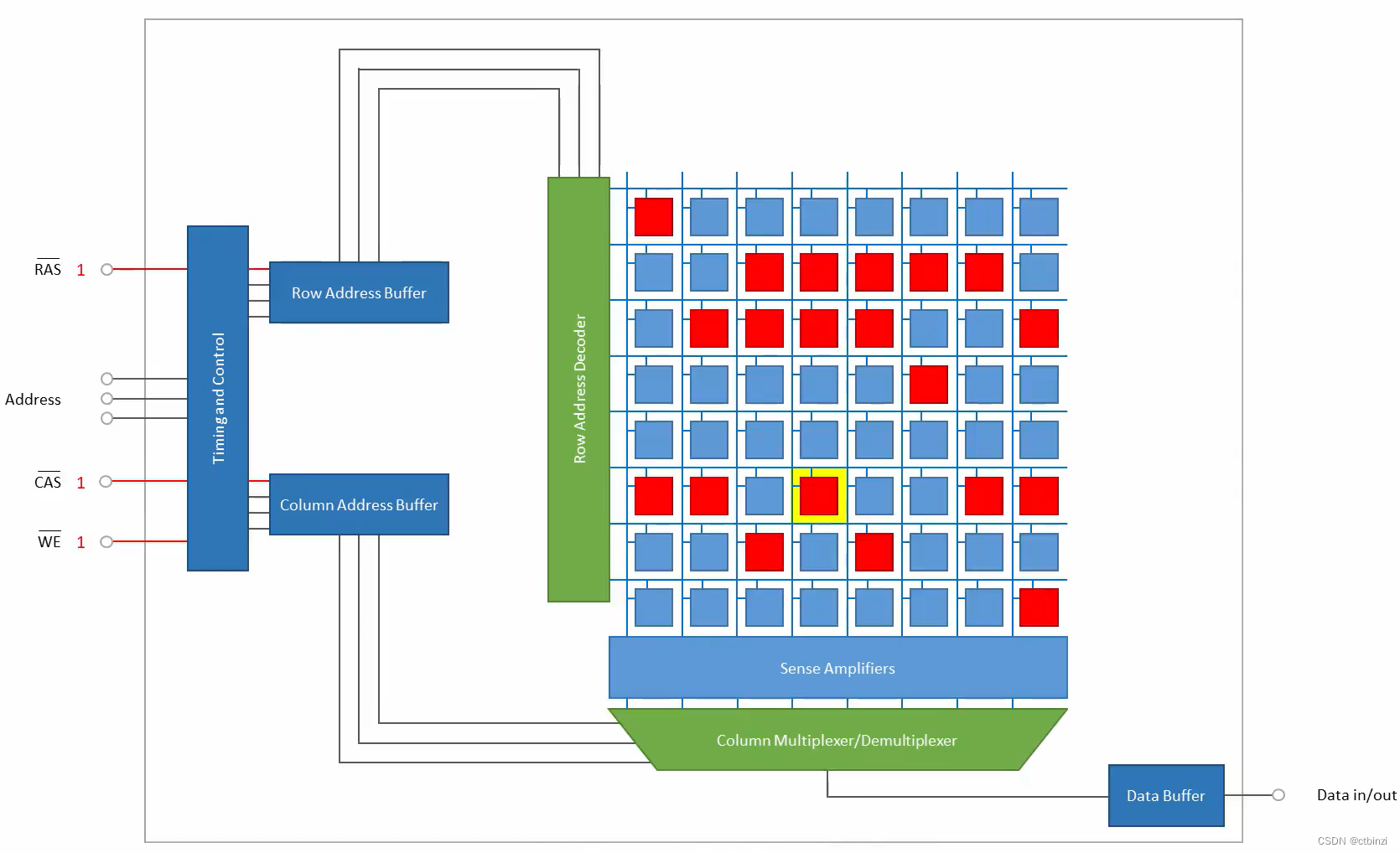

DDR4的Cell阵列大小是65536行x1024列,即65536根word line,1024根bit line,每根word line上联了1024个Cell,可以存储1Kbit数据,整个Cell整列可存储65535*1Kbit=64Mbit=8MB数据。每一列(bit line)配一个信号放大器(兼1bit数据锁存器)用于读取Cell所存储的数据值。行地址输入端配16位的地址解码器,列地址输入端配10位的选通器。为了减少引脚数,DDR4对行地址线和列地址线做了复用,整体电路示意如下图:

RAS:行地址选通信号线;

CAS:列地址选通信号线;

WE:写使能信号线;

Address:行/列复用地址总线,DDR4地址总线是16根;

Data in/out:1bit地址线;

Row Address Buffer:行地址缓存;

Row Address Decoder:行地址解码器,将DDR4的16位行地址解码位65536行中的唯一对应行;

Column Address Buffer:列地址缓存;

Column Multiplexer/Demultiplexer:列地址选通器,根据DDR4的10位列地址选通唯一对应列;

Sense Amplifiers:信号放大器组,DDR4一个Cell阵列有1024列,对应1024个信号放大器,信号放大器兼具数据锁存功能,DDR4一个Cell阵列可以保存1024bit数据;

Data Buffer:数据缓存,读/写数据时,数据先进数据缓存;

数据读取流程:

1.给所有1024根bit line预充电到1/2标准电压(即Cell存储数值为1时的电容电压),然后断开;

2.内存控制器将行地址值输入地址总线,并使能RAS,行地址被缓存;

3.行地址编码器将16bit地址解码后拉高对应word line的电压,使该行所有1024个三极管导通;

4.信号放大器读取该行1024个Cell中存储的数据,并将其锁存;

5.内存控制器将列地址值输入地址总线,并使能CAS,列地址被缓存;

5.列选通器根据10bit列地址,将对应列数据值写入数据缓存;

6.将1024个信号放大器中锁存的数据写回Cell,因为数据读取过程中破坏了Cell电容的电量值;

数据写入流程:

1.给所有1024根bit line预充电到1/2标准电压(即Cell存储数值为1时的电容电压);

2.行地址编码器将16bit地址解码后拉高对应word line的电压,使该行所有1024个三极管导通;

3.信号放大器读取该行1024个Cell中存储的数据,并将其锁存;

4.列选通器根据10bit列地址,将对应列数据值写入信号放大器;

5.将1024个信号放大器中锁存的数据写入Cell;

上述读/写流程是一个理论模式,DDR4实际读写过程中,为了提高效率,会利用信号放大器的数据锁存功能。比如前后两次读取数据位于同一个Row,那么就可以直接从信号放大器的缓存中读取数据,而没有必要去Cell中读取,节省了上述1到4步骤耗时,大大加快了数据读取速度。

Bank

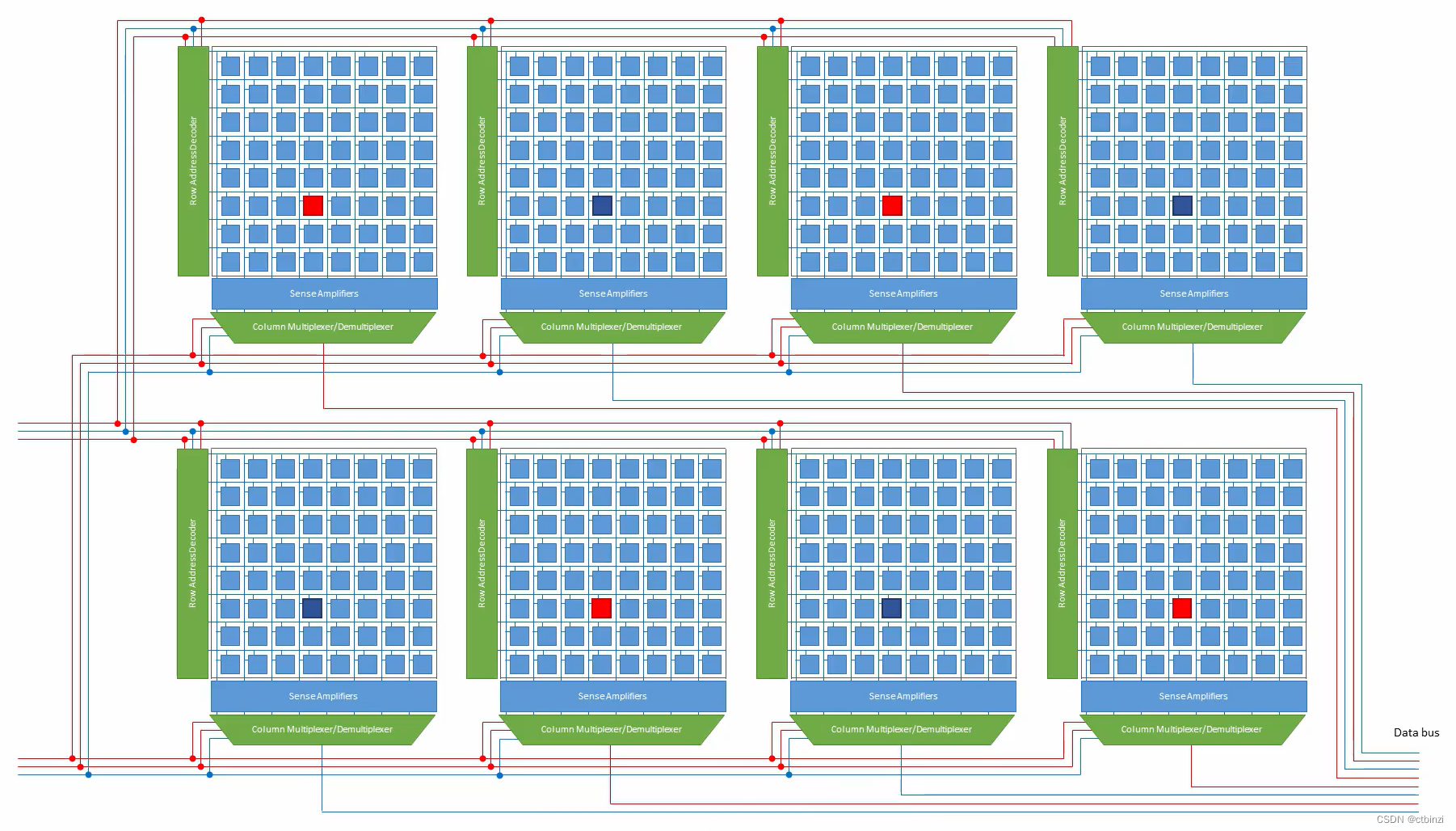

为了进一步加速数据读写效率,DDR4将16个Cell阵列进行并联,让其共用行/列地址线,通过各自独立的16根数据线,一次可以同时读写16bit数据,如下示意图(示意图展示的是8Cell并联)

DDR4将使用此种方式并联起来的16个Cell阵列称为一个Bank。Bank内16bit数据同时读写的机制也称为数据预取,即DDR4单个Bank具备16bit数据预取能力,大大提高了数据读写效率。

Bank Group

在Bank预取的基础上,DDR4还设计了Bank Group机制,每个Bank Group内含4个Bank,各个Bank Group可独立工作。

Chip

以16bit预取的1GB容量的DDR4芯片为例,其内部总共2个Bank Group,每个Bank Group内有4个Bank,每个Bank内有16个Cell阵列,每个Cell阵列有65536行/1024列。

因此一颗DDR4芯片的存储容量是2*4*16*65536*1024*1bit=8589934592bit=8Gb=1GB。

至此,一颗16bit预取1GB容量DDR4芯片的存储结构梳理完毕。当然DDR4还有其他规格的芯片,总共有三种数据位宽4bit、8bit、16bit,单颗芯片容量从2Gb到16Gb不等,如下图:

DDR控制器

DDR芯片预留了地址总线接口、数据总线接口、各种控制线接口,要通过这些接口将数据写入或读出,需要外部发起读写控制信号,以及做数据搬运,DDR控制器便承担该角色。CPU需要访问内存数据时,将内存地址交由DDR控制器,DDR控制器负责完成数据的读写。通常一个DDR控制器会同时控制多颗DDR芯片,下面分析一下多颗DDR芯片的协作方式。

Rank

以数据位宽64bit的DDR控制器为例,将4颗位宽16bit的DDR4芯片进行并联,类似Bank内Cell阵列的并联,共用地址线,64根数据线分为4组,每组16根分别连接4颗DDR4芯片,这4颗DDR4芯片便组成一个Rank。在DDR控制器对一个Rank进行数据读写的过程中,这4颗DDR4芯片同时工作,访问相同的地址,即相同的行和列。

DIMM

将一个或者多个(通常是1个、2个或4个)Rank的芯片装在一块PCB上,就得到一根内存条,准确说法是“双列直插式内存模块(DIMM)”。把DIMM插入内存插槽,插槽连接的式CPU内部的内存控制器,它们之间用内存通道连接。

Channel

一个DDR控制器对外连接的通道称为一个Channel,一颗CPU可内置多颗DDR控制器,即称为多通道技术。常见的PC用CPU通常为2通道,HPC领域的CPU通常会有4通道,甚至更高,比如Intel Core i9系列处理器和AMD EPYC系列处理器。

每个DDR控制器可独立工作,以4通道CPU为例,每通道数据位宽64bit,理论总位宽可达到4*64bit=256bit。

Cache缓存机制

Cache是基于SRAM技术的存储器,通常集成在CPU内部,其访问效率远高于DDR。CPU使用数据过程中,会将数据缓存在Cache中,在读写数据时,先检测Cache中是否有所需要的数据,如果有,就直接读写Cache,而无需访问DDR,大大提高了读写效率。

Cache存储数据最小单位是Cache Line,通常为64Byte,即512bit。也就是说,在CPU启用Cache机制时,对内存的访问是以512bit为单位,而非1字节或4字节,这对软件性能优化有较大影响,需要重点关注。

参考资料:

DRAM原理_哔哩哔哩_bilibili

[DDR]1 - Understanding the Basics_bank groups and banks.__山猫的博客-CSDN博客

这篇关于DDR4技术原理详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!