assertions专题

Junit入门到掌握-8-JUnit基础-Exception和Timeout和Assertions

本篇来学习两个参数项,异常和超时。这两个参数是结合@Test来使用的,作用范围当然是测试方法。 1.异常Exception 有时候我们执行这个方法,出现异常是期待的结果,单元测试中如果出现异常,会中断测试,为了不中断,我们需要使用异常注解 模拟异常测试 为了模拟异常,我们需要到被测项目中,某一个方法写一个抛异常的代码,然后这个自定义异常类需要我们写以下。 编辑被测项目的T

playwright: Assertions断言

response & page 断言 to_be_ok() 判断response的status code是否在200-299之间 expect(response).to_be_ok()to_have_title(str | pattern) 判断page的title是否和指定的title一致 expect(page).to_have_title("title string")to_have_ur

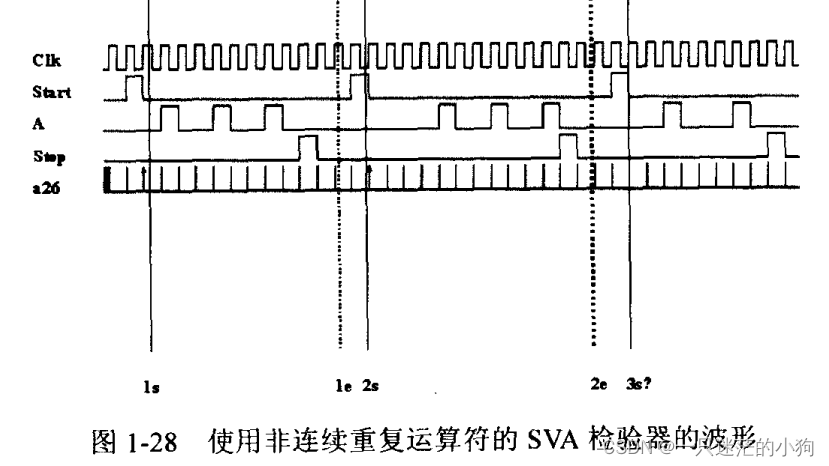

SystemVerilog Assertions应用指南 Chapter 1.21重复运算符

1.21重复运算符 如果信号“stat”在任何给定的时钟上升沿跳变为高,接着从下一个时钟周期起,信号“a”保持三个连续时钟周期为高,然后下一个时钟周期,信号“stop”为高,像上述描述的序列可以使用下面的SVA代码来检验。 sequence ss ;@(posedge clk) $rose(start) |-> ##1 a ##1 a ##1 a ##1 stop;endse

SystemVerilog Assertions应用指南 Chapter1.20“ $past”构造

1.20“ $past”构造 SVA提供了一个内嵌的系统任务“$past”,它可以得到信号在几个时钟周期之前的值。在默认情况下,它提供信号在前一个时钟周期的值。结构的基本语法如下 $past (signal_name ,number of clock cycles) 这个任务能够有效地验证设计到达当前时钟周期的状态所采用的通路是正确的。属性p19检验的是在给

SystemVerilog Assertions应用指南 Chapter 1.16“ended”结构

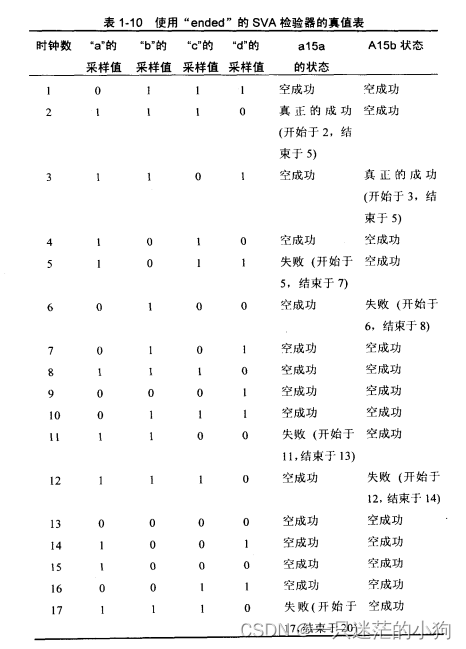

1.16“ended”结构 到目前为止,定义的序列都只是用了简单的连接( concatenation)的机制。换句话说,就是将多个序列以序列的起始点作为同步点,来组合成时间上连续的检查。SVA还提供了另种使用序列的结束点作为同步点的连接机制。这种机制通过给序列名字追加上关键词“ ended”来表示。例如,s. ended表示序列的结束点。关键词“ ended”保存了一个布尔值,

SystemVerilog Assertions应用指南 Chapter1.35“ matched”构造

任何时候如果一个序列定义了多个时钟,构造“ matched”可以用来监测第一个子序列的结束点。序列s_a查找信号“a”的上升沿。而信号“a”是根据时钟“ckl”来采样的。序列s_b查找信号“b”的上升沿。信号“b”则是根据时钟“ck2”来样的。属性 p_match验证在给定的时钟“clk2”的上升沿,如果序列s_a匹配,那么在一个周期后,序列s_b也必须为真。 sequence

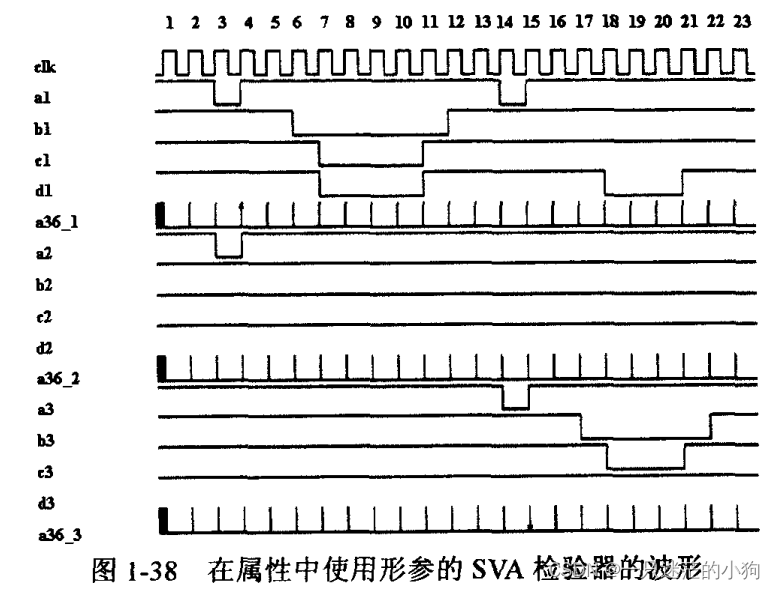

SystemVerilog Assertions应用指南 Chapter1.31 在属性中使用形参

可以用定义形参( formal arguments)的方式来重用一些常用的属性。属性“arb”使用了4个形参,并且根据这些形参进行检验。其中还定义了特定的时钟。SVA允许使用属性的形参来定义时钟。这样,属性可以应用在使用不同时钟的相似设计模块中。同样的,时序延迟也可以参数化,这使得属性的定义更具有普遍性。 属性首先检査有效开始。在给定的时钟上升沿,如果在信号"a”的

SystemVerilog Assertions应用指南 Chapter1.32 嵌套的蕴含

SVA允许使用嵌套的蕴含。当我们有多个门限条件指向一个最终的后续算子时,这种构造十分有用。 属性 p_nest检验如果信号“a”有一个下降沿,则是一个有效开始,接着在一个周期后,信号“b”,“c”和“d”应该为低电平有效信号以保持这个有效开始。如果第二个条件匹配,那么在6到10个周期内期望“free”为真。注意,当且仅当信号“b”,“c”和“d”都匹配时,在后续状况

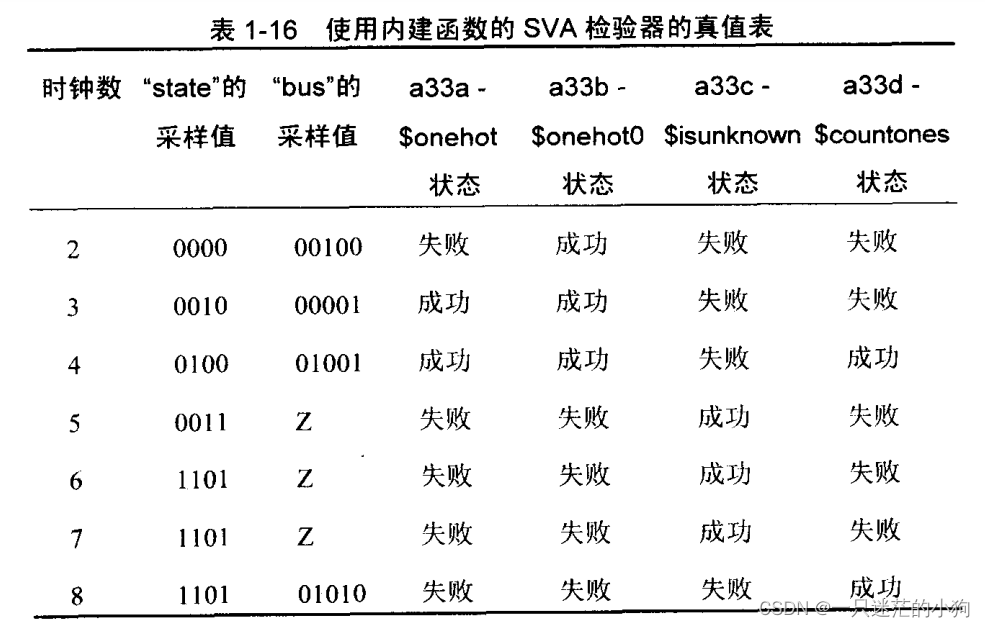

SystemVerilog Assertions应用指南 第一章(1.28章节 内建的系统函数)

SVA提供了几个内建的函数来检查一些最常用的设计条件。 $onehot(expression)—检验表达式满足“one-hot”,换句话说,就是在任意给定的时钟沿,表达式只有一位为高。 $onehot0( expression)—检验表达式满足“ zero one-hot”,换句话说,就是在任意给定的时钟沿,表达式只有一位为高或者没有任何位为高。

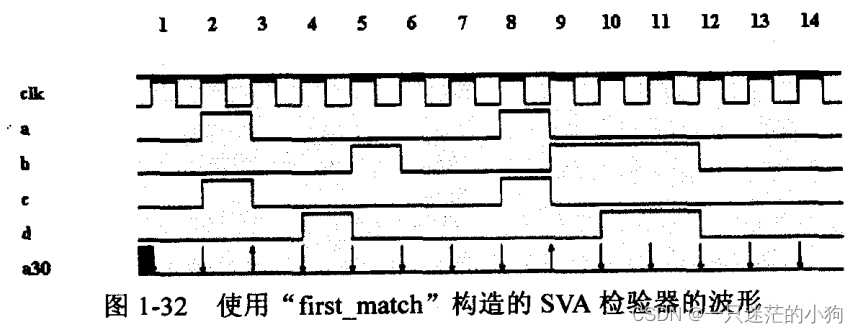

SystemVerilog Assertions应用指南 第一章(1.25章节 “first_match”运算符)

任何时候使用了逻辑运算符(如“and”和“or”)的序列中指定了时间窗,就有可能出现同一个检验具有多个匹配的情况。“ first match”构造可以确保只用第一次序列匹配,而丢弃其他的匹配。当多个序列被组合在一起,其中只需时间窗内的第一次匹配来检验属性剩余的部分时,“ first match”构造非常有用。 当检验属性p30时,第一次匹配保留下来,其他匹配都被丢弃

SystemVerilog Assertions应用指南 第一章(1.25章节 “first_match”运算符)

任何时候使用了逻辑运算符(如“and”和“or”)的序列中指定了时间窗,就有可能出现同一个检验具有多个匹配的情况。“ first match”构造可以确保只用第一次序列匹配,而丢弃其他的匹配。当多个序列被组合在一起,其中只需时间窗内的第一次匹配来检验属性剩余的部分时,“ first match”构造非常有用。 当检验属性p30时,第一次匹配保留下来,其他匹配都被丢弃

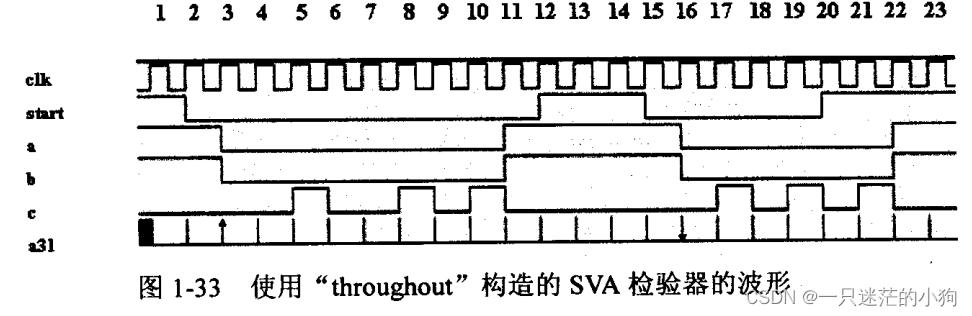

SystemVerilog Assertions应用指南 第一章(1.25章节 “throughout”运算符)

蕴含( (implication)是目前讨论到的允许定义前提条件的一项技术。例如,要对一个指定的序列进行检验,必须某个前提条件为真。也有这样的情况,要求在检验序列的整个过程中,某个条件必须一直为真。蕴含只在时钟边沿检验前提条件一次,然后就开始检验后续算子部分,因此它不检测先行算子是否一直保持为真。为了保证某些条件在整个序列的验证过程中一直为真,可以使用“ throughout”运算