本文主要是介绍SystemVerilog Assertions应用指南 第一章(1.25章节 “first_match”运算符),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

任何时候使用了逻辑运算符(如“and”和“or”)的序列中指定了时间窗,就有可能出现同一个检验具有多个匹配的情况。“ first match”构造可以确保只用第一次序列匹配,而丢弃其他的匹配。当多个序列被组合在一起,其中只需时间窗内的第一次匹配来检验属性剩余的部分时,“ first match”构造非常有用。

当检验属性p30时,第一次匹配保留下来,其他匹配都被丢弃了。

sequence s30a;@(posedge clk) a ##[1:3] b;

endsequencesequence s30b;@(posedge clk) c ##[2:3] d;

endsequenceproperty p30_fm;@(posedge clk) first_match(s30a or s30b);

endpropertyproperty p30;@(posedge clk) s30a or s30b;

endpropertya30: assert property(p30);

a30_fm: assert property(p30_fm);在上面的例子中,属性用运算符“or”将两个序列组合在起。这个属性的几个可能的匹配如下所示。

a ##1 b;

a ##2 b;

a ##3 b;

c ##2 d;

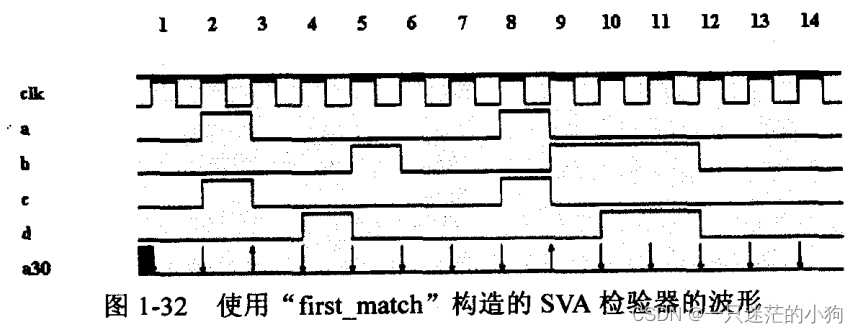

c ##3 d; 图1-32显示了属性p30在模拟中的响应。图中显示了两次成功,分别在时钟周期3和9在时钟周期3的成功基于序列(c##2d)的匹配。在时钟周期9的成功基于序列(a##1b)的匹配。在这两种情况中,第一次序列匹配就使得整个属性成功。

这篇关于SystemVerilog Assertions应用指南 第一章(1.25章节 “first_match”运算符)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!