本文主要是介绍SystemVerilog Assertions应用指南 第一章(1.28章节 内建的系统函数),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

SVA提供了几个内建的函数来检查一些最常用的设计条件。

$onehot(expression)—检验表达式满足“one-hot”,换句话说,就是在任意给定的时钟沿,表达式只有一位为高。

$onehot0( expression)—检验表达式满足“ zero one-hot”,换句话说,就是在任意给定的时钟沿,表达式只有一位为高或者没有任何位为高。

$isunknown( expression)—检验表达式的任何位是否是Ⅹ或者Z。

$countones( expression)—计算向量中为高的位的数量。

断言语句a33a检验向量“ state”是“one-hot”。断言语句a33b检验向量“ state”是“ zero one-hot”,断言语句a33c检验向量“bus”是否有任何位为X或Z。断言语句a33d检验向量“bus”中等于1的位的个数大于1。

module routines;logic clk;logic [3:0] state;

logic [4:0] bus;

integer i;initial $vcdpluson();initial

begin

clk = 1'b0; state = 4'd0;

@(posedge clk);for(i=0; i<3; i++)

beginstate = i*2;bus = $random();@(posedge clk);

endfor(i=0; i<3; i++)

beginstate = $random() % 16;bus = 8'dz;@(posedge clk);

endbus = 4'd10;

repeat(2) @(posedge clk);$finish();

end// builtin system functionsa33a: assert property(@(posedge clk) $onehot(state));

a33b: assert property(@(posedge clk) $onehot0(state));

a33c: assert property(@(posedge clk) $isunknown(bus));

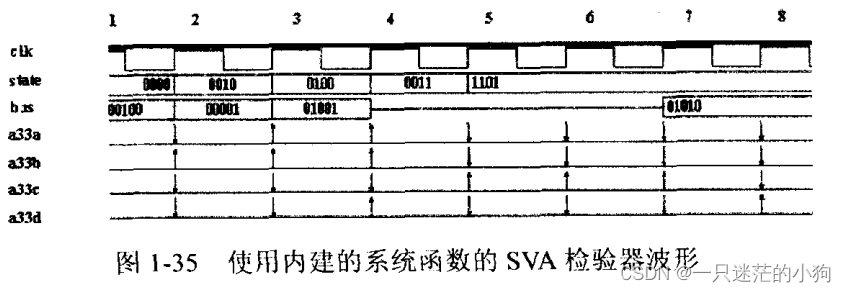

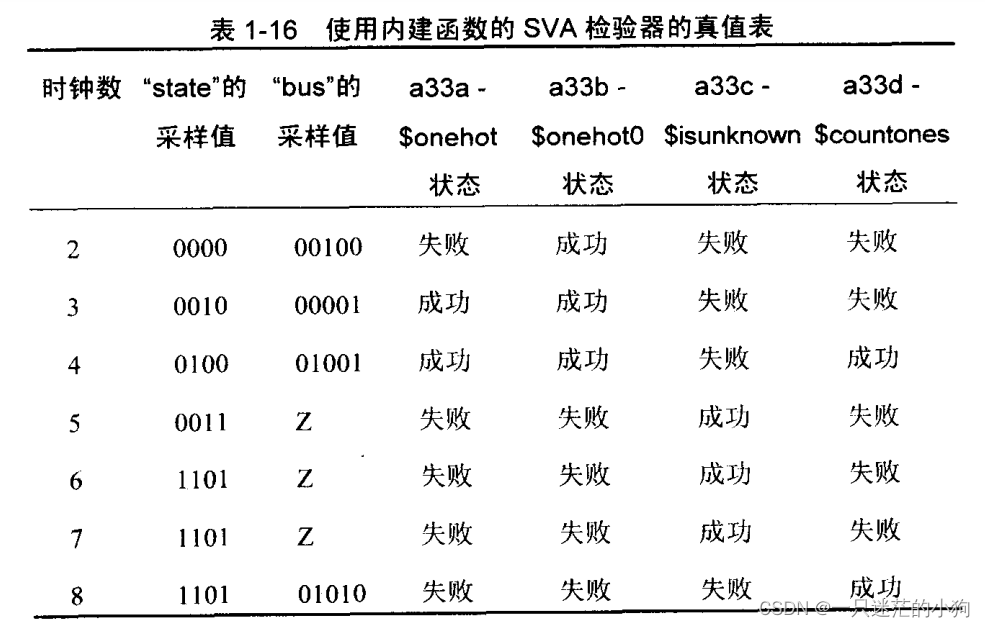

a33d: assert property(@(posedge clk) $countones(bus) > 1);initial forever clk = #25 ~ clk;endmodule 图1-35显示了上述断言在模拟中的响应。表1-16总结了每个断言的状态和向量“ state”和“bus”的采样值。注意,断言a33a在时钟周期2失败,因为所有位都为零。“one-hot”要求在任何时钟上升沿都只有一位为高。另一方面,断言a33b成功因为它检查“ zero one-hot”,而对于这种构造,所有位都为零是合法的a33a和a3b都在时钟周期5,6,7,8失败,因为有超过一位为高。断言a33c在任何时候向量“bus”的值不为X或Z时失败。它在时钟周期5,6,7成功,因为向量的值为Z。断言a33d在时钟周期2,3,5,6,7失败,因为值为高的位的个数没超过1。断言a33d在时钟周期4,8成功,因为向量“bus”在这两个时刻都有两位为高。

这篇关于SystemVerilog Assertions应用指南 第一章(1.28章节 内建的系统函数)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!