本文主要是介绍深入了解 PCIe 6.0 的演变和优化,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

PCI-Express是继ISA和PCI总线之后的第三代I/O总线,即3GIO。由Intel在2001年的IDF上提出,后来PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。它的主要优势就是数据传输速率高,另外还有抗干扰能力强,传输距离远,功耗低等优点。

注:第一代总线一般指ISA、EISA、VESA和Micro Platforms。

第二代总线一般指PCI、AGP和PCI-X。

——————————————————

PCIe protocol (Peripheral Component Interconnect Express) 于 2003 年推出第一代产品,在串行计算机扩展总线中允许每通道高达 2.5 GT/s,这是行业的一项巨大突破。此后,该协议经过多次发展,与上一代协议相比,其传输速率始终翻倍,并在需要时带来新功能和优化。

最新版本于 2022 年发布,其中引入了 PCIe 6.0,每信道速度高达 64.0 GT/s。另外,PCIe7.0也在路上,单信道速度达到了惊人的128GT/s.

2023 年在圣何塞举行的 PCI-SIG 开发者大会上宣布的那样,PCIe 6.0再次将速度提高了一倍。考虑到 20 年的行业使用和经验,这些变化考虑了对现有规则的许多必要优化。引入了新的概念和技术,如1b/1b编码、PAM4调制和Flit Mode操作。

一、了解 PCIe 6.0 优化

PCIe 6.0 规范中所有功能的更改都是考虑到它们需要优化以跟上更高的吞吐率。因此,遵循了以下准则:

减少损失: 通过避免不必要的编码;

做出假设:基于既定模式;

避免传输不必要的信息:这可以由另一方推断出来;

避免重新配置:如果之前已经配置过。

1b/1b 编码和减少丢失

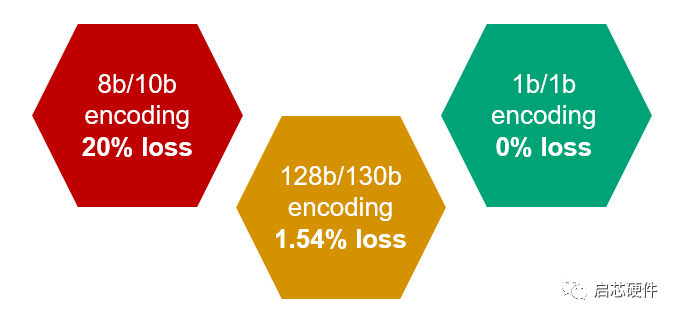

PCIe 6.0 中引入的新编码是通过避免不必要的编码来减少损耗的最佳例子。之前的协议中,PCIe 3代之后通过128b/130b传输,或更早之前1代2代的速度运行时使用 8b/10b 编码,存在更大的损耗具体也就是20%损耗。其中,128b/130b的编码,这意味着每 128 位数据需要 2 位额外的数据才能被另一端正确解码。这导致了串行链路的效率低下,其中仅由于编码而在位级中损失了 1.54% 的带宽。

最新的6.0中,1B/1B通过保证传输的每个比特都可以被另一方用作实际信息来解决这个问题。这是通过在预期的数据类型的每一端实现内部计数器来完成的。只要设计经过正确验证以遵守这些计数器,就可以保证它们能够进行通信,而无需在链接中发送任何额外的不必要的信息。

Flit 序列号和优化信息传输

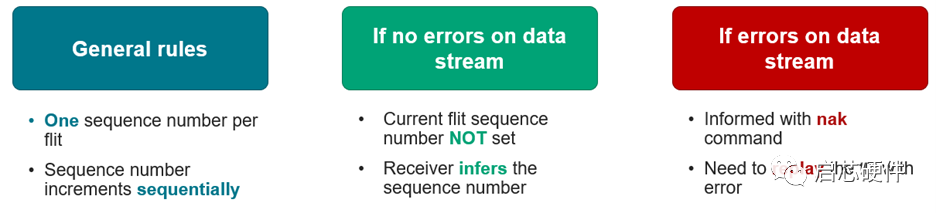

flit 序列号是 PCIe 6.0 中引入的一个新概念。它取代了事务层数据包 (TLP) 中存在的旧序列号及其确认或重放机制。

之前,序列号总是附加到每个传输的 TLP 上。尽管它增加了链路的鲁棒性,但考虑到 TLP 具有顺序序列号,这样其实存在某种程度的浪费资源。因此,知道一个 TLP 的序列号意味着知道它旁边的 TLP 的编号,依此类推。

flit 序列号协议通过实现隐式序列号来优化这一点,其中序列号由另一端推断。不仅如此,序列号也在 flit 级别,可以同时容纳多个 TLP。因此,以前用于始终传输序列号信息的空间可用于增加有用信息的带宽。

L0p 和优化不必要的重新配置

之前在链接后动态更改链路宽度的过程对设备来说成本很高,因为它需要经历链路训练和状态机 (LTSSM) 的所有配置状态。这意味着重新配置车道的所有细节,即使唯一需要更改的变量是正在使用的链路宽度。

这在 PCIe 6.0 中得到了增强,引入了 L0 部分 (L0p) 功能,仅在 Flit 模式下存在。执行 L0p 序列时,可以在活动数据传输期间更改链路宽度,而无需关闭链路。这意味着通过更改链路宽度来节省功耗要有效得多,而且设备可以轻松保持较小的宽度,以防出现热节流问题。

综上所述,PCIe 6.0带来了许多变化,这些变化都是为了保证PCIe协议的所有层都能跟上更高的传输速率而进行的优化。目前正在进行的 PCIe 7.0 在所有这些更改的基础上继续提供 PCIe 支持和优化。

这篇关于深入了解 PCIe 6.0 的演变和优化的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!