pcie专题

如何编写Linux PCIe设备驱动器 之二

如何编写Linux PCIe设备驱动器 之二 功能(capability)集功能(capability)APIs通过pci_bus_read_config完成功能存取功能APIs参数pos常量值PCI功能结构 PCI功能IDMSI功能电源功率管理功能 功能(capability)集 功能(capability)APIs int pcie_capability_read_wo

FPGA PCIE驱动,windriver驱动 wdf驱动 windows linux PCIE DMA驱动 支持win10 server2016

一:相关介绍 本人一直从事fpga pcie dma驱动开发,可以开发windwos Linux 原生驱动 wdf 或者基于第三方库的windriver。支持win10 win server。提供稳定的驱动库,或者源码,开发者可以不关心底层驱动直接使用封装的库。 二:PCIE 驱动开发的稳定性和高效性: 本驱动库均已经进行了实际交付使用,通过了严格的jun

《PCI Express体系结构导读》随记 —— 第II篇 第7章 PCIe总线的数据链路层与物理层(7)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第7章 PCIe总线的数据链路层与物理层(6) 7.1 数据链路层的组成结构 7.1.1 数据链路层的状态 3. DL_Active状态 当数据链路层处于DL_Active状态时,PCIe链路可以正常工作。此时数据链路层可以从事务层和物理层正常接收和发送TLP、并处理DLLP,此时数据链路

【精讲】PCIe基础篇——Non-Prefetchable Prefetchable MMIO

MMIO 有两种, Non-Prefetchable MMIO:非预取内存空间 Prefetchable MMIO :可预取内存空间 Prefetchable MMIO:将MMIO的一个区域设置为可预取的,允许CPU提前获取该区域中的数据,以预测请求者在不久的将来可能需要比实际请求更多的数据。对数据进行这种小规模缓存是安全的,因为读取数据不会改变目标设备上的任何状态信息。也就是说,

【精讲】PCIe基础篇——Memory IO 地址空间

在早期的PC中,IO设备中的内部寄存器/存储是通过IO地址空间(由Intel定义)来访问的。然而,由于与IO地址空间相关的一些限制和不良影响(我们在这里不讨论),IO地址空间很快就失去了软件和硬件供应商的青睐。这导致IO设备的内部寄存器/存储被映射到内存地址空间(通常称为Memory mapped IO,或MMIO)。然而,由于早期的软件是使用IC地址空间来访问IO设备上的内部寄存

【精讲】PCIe基础篇——BAR(Base Address Register)详解

一、为什么需要BAR 系统中的每个设备中,对地址空间的大小和访问方式可能有不同的需求,例如,一个设备可能有256字节的内部寄存器/存储,应该可以通过IO地址空间访问,而另一个设备可能有16KB的内部寄存器/存储,应该可以通过基于MMIO的设备访问。哪些地址应该使用哪种方式(IO或Memory)来访问它们的内部位置,这是系统软件(即BIOS和OS内核)的工作。因此设备必须为系统软件

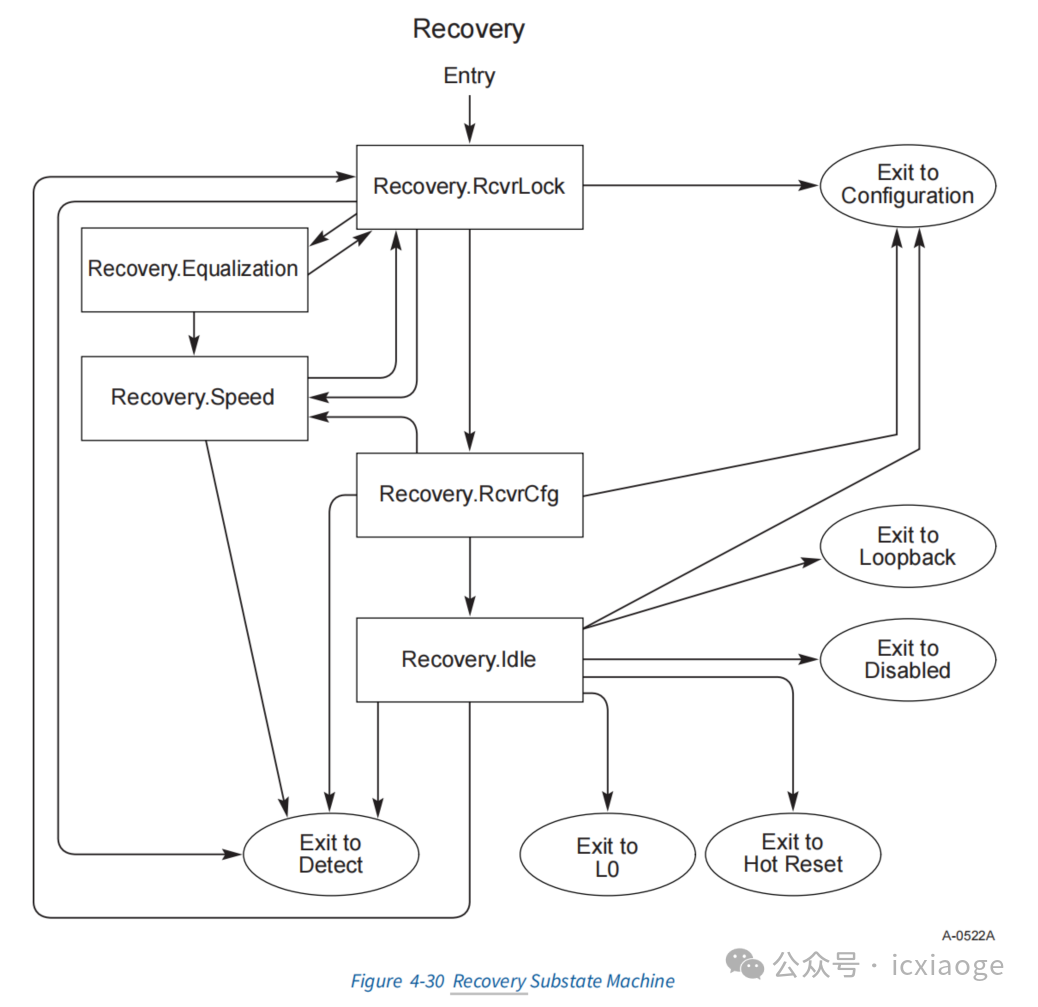

PCIe物理层LTSSM状态机解析

目录 1、Detect 2、Polling 3、Configuration 4、L0 5、Recovery 6、L0s/L1/L2 7、Hot Reset 8、Disabled 9、Loopback 在PCIe链路可以正常工作之前,需要对PCIe链路进行链路训练,在这个过程中,就会用LTSSM状态机。LTSSM全称是Link Training and Status St

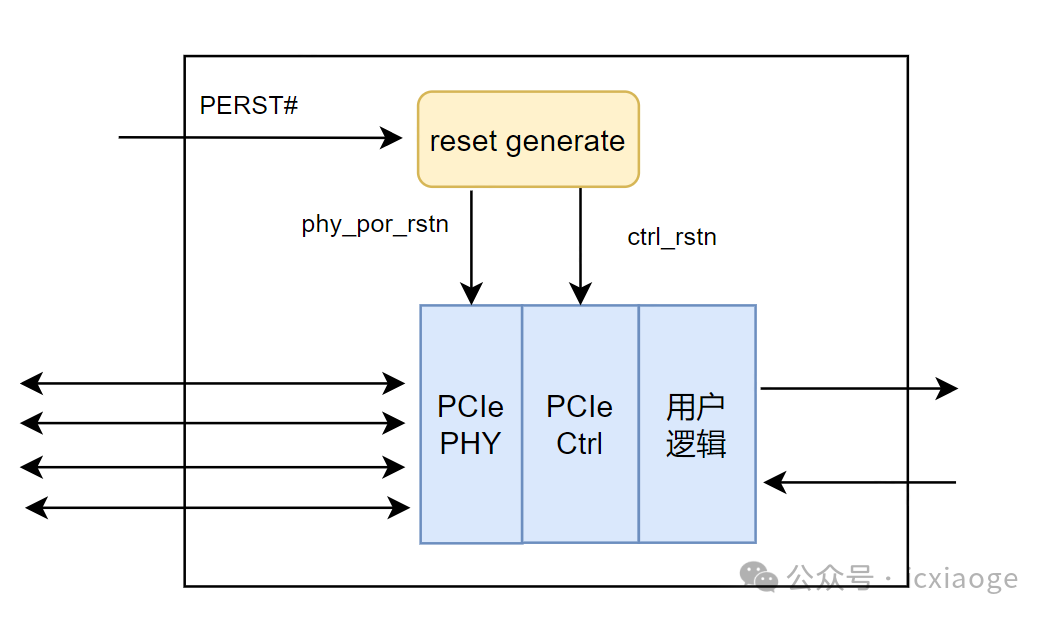

PCIe 复位:必须了解的PERST#

1.什么是PERST# PERST#作为 Fundamental Reset,是直接通过边带信号PERST#(PCI Express Reset)产生的。Fundamental Reset会复位整个PCIe设备,初始化所有与状态机相关的硬件逻辑,端口状态以及配置空间中的配置寄存器等(every state machine and all the hardware logic, port s

PCIe Gen4 ltssm协商过程

本章节我们以gen4 Endpoint为例介绍PCIe ltssm(链路状态机)协商过程。 正常PCIe设备链路状态跳变为 detect-->polling-->configuration-->L0(gen1)-->recovery-->L0(gen3)-->recovery-->L0(gen4)。 需要注意的是在进入configuration状态之前,因为物理层还未收到有效数据(例如在P

BIOS工程师标准作业书 之 PCIE 问题如何处理

bios 工程师作为最基层的岗位,做事情一定要按部就班,肯定不能随意发挥。PCI 作为服务器中最主要的总线,也是最容易出bug 的地方。所以我整理了这篇文章。 当前x86系统PCIe架构中面临的挑战以及问题 系统设计中使用了不同供应商的硬件模块,不同的硬件模块都有各自的错误处理和报错机制。 在这么复杂的系统中,如何快速定位故障的模块,并使系统重新健康的上线工作 如何在复杂的系统中,找到问题

PCIE-TLP路由

TLP路由存在三种形式,基于地址、基于ID、隐式路由。 (1)关于TLP路由方式的划分: cpl/cpld ; cfgwr/cfgrd -> ID routing Mwr/Mrd[lock]/atomicop ; Iowr/Iord -> address routing Msg/MsgD -> 三种均可 (2)关于posted/non-posted mwr

PCIe学习笔记(28)--- PL - Electrical -- (3)

Rx Specs Transmission Loss: TX Vdiff p-p min = 800 RX Vdiff p-p = 175 13.2dB ___________________________________ Signal compensation: TX equalization: de-emphasis (two-tap Tx equ

PCIe学习笔记(27)--- PL - Electrical -- (2)

Tx specs Measuring Tx Signals: "breakout channel" (?) SMA (SubMiniature version A) microwave-type coaxial connectors (?) low-jitter clock source to the device under test (?) "replica channe

PCIe学习笔记(26)--- PL - Electrical -- (1)

对应章节Chapter 13 physical layer electrical link training是以2.5G开始的 一个设备如果支持8G,必须支持2.5G,但非必须支持5G L0 full-on state 差分电路中,保持DC common mode voltage 如果进了electrical idle则会低于一个threshold value TX端

PCIe学习笔记(24)--- PL-Logical (Gen 1 and Gen 2) --- (1)

对应Chapter 11: Physical layer- logical (Gen 1 and Gen2) TX: D-DATA/K-CONTROL: Gen1/2是区分D/K symbol的,所以有D/K# bit Gen3没有K symbol, 128 bit (16 bytes) data block中, 有2 bit的SYNC HEADER, 其中包含的信息,让RECE

PCIe学习笔记(23)--- 中断(4)--- 同步问题

存在这样一种现象: 设备往系统MEMORY中写数据,“认为”该笔数据写完之后,触发中断 中断函数处理该笔数据,但事实上,系统MEMORY中的数据,可能是STALE的 导致该问题的原因, 第一,写数据是POST的 第二,写的过程可能会被DELAY 第三,一旦有DELAY,就可能导致中断先于数据写先到 方法一: dummy read 在ISR中加一个device read

PCIe学习笔记(22)--- 中断(3)---MSI-X

MSI-X MSI最多支持32 MSI-X最多支持2048 Message control: bit 15: MSI-X Enable (是否用MSI-X中断,或者用MSI, INTx来替代) bit 14: Function Mask (是否可以发中断) 10:0: Table size in N-1 cap structure: MSI-X Table Of

PCIe学习笔记(21)--- 中断(2)---MSI

MSI MSI cap registers(config space area, 256B): Target mem addr data value to write to target number of unique messages MSI寄存器 刚刚才了解的一点 Target message address register一般是address of Loca

PCIe学习笔记(20)--- 中断(1)--- Legacy

MSI 与 INTx Message是不同的东西 Command: Interrupt Acknowledge for INTR(PIC output) (INTx# inputs) PIC returns a 8-bit value called the Interrupt Vector 获得VECTOR SMP, from PIC to IO APIC APIC bus:

aspeed2600 openbmc对mctp over pcie的支持分析(支持mctp over pcie)

遍搜全网,竟然关于openbmc mctp over pcie的支持说明情况了无文章,这不是一个艰难的问题,服务器BMC也不是一个超级精尖的产品,想当年分享stm32资料,都是满天飞。可能服务器市场大家对于文章上的分享并无兴趣。 此篇文章只是一个最基本的简单的说明文章,弥补一下openbmc资源匮乏吧。另外,本片文章只是一个简单的开篇文章,有错漏,有知识不全面,请尽管评论。 注意: 本章涉及的

PCIE-Precode

Transmitter Precode Request: Precoding可以有效的降低Burst errors(突发连续)的影响,但是Bit Error Rate(BER)将上升为之前的两倍. [FPGA 实现及PCIe IP 核知识点] PCIe为什么要增加Precoding?-FPGA常见问题论坛-FPGA CPLD-ChipDebug 需要注意的点: (1)det

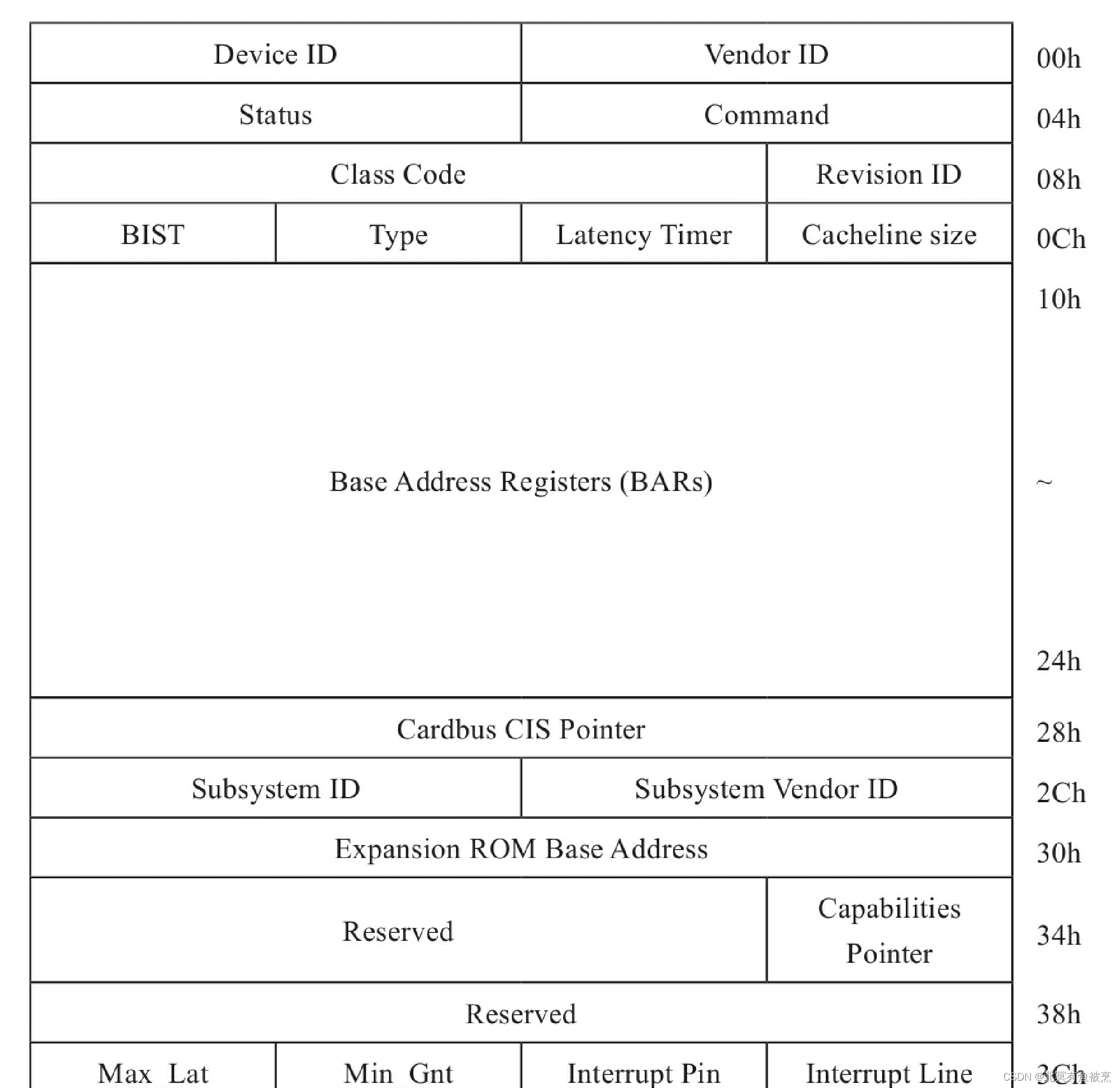

微知-PCIe配置空间中哪个字段表示设备类型?有哪三种类型?哪个字段表示厂商ID

pcie配置空间早期是246字节。由头部和设备相关部分两个region组成。其中头部64B,设备相关192B。 其中64B是header叫做预定义头部,存储设备基本信息和通用控制部分,比如说pcie的venderid就存在byte0和byte1。这个vendor id是PCI SIG组织统一管理的。每个厂商固定。如mellanox网卡vendor id是15b3。tplink是10ec 可以通过

【转】PCIE 通道x4/8/16的定义

PCI Express 版本 行代码 传输速率 吞吐量 ×1 ×4 ×8 ×16 1.0 8b/10b 2.5GT/s 250MB/s 1GB/s 2GB/s 4GB/s 2.0 8b/10b 5GT/s 500MB/s 2GB/s 4GB/s 8GB/s 3.0 128b/130b 8GT/s 984.6MB/s 3.938GB/s 7.8

PCIe学习笔记(25)

数据完整性 PCI Express的基本数据可靠性机制包含在数据链路层(data Link Layer)中,它使用32位的LCRC (CRC)码逐链路检测TLP中的错误,并采用逐链路重传机制进行错误恢复。TLP是一个数据和事务控制单元,由位于PCI Express域“边缘”的数据源(如Endpoint或Root Complex)创建,可能通过中间组件(即交换机)路由,并由最终的PCI Expre

PCIE-TS1/TS2,变量总结

1.标准TS1/TS2 2.EQ TS1/TS2 3.Modified TS1/TS2 Modified TS1/TS2 是什么?Modify了什么?为什么要Modify?非 PCIe 协议运行在 PCIe PHY 上或发送 TS Message 时,在 LTSSM 部分子状态采用 Modified TS1/TS2。允许发送 Modified TS1/TS2 的 LTSSM 子状态有 Cfg