本文主要是介绍PCIE-Precode,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Transmitter Precode Request:

Precoding可以有效的降低Burst errors(突发连续)的影响,但是Bit Error Rate(BER)将上升为之前的两倍.

[FPGA 实现及PCIe IP 核知识点] PCIe为什么要增加Precoding?-FPGA常见问题论坛-FPGA CPLD-ChipDebug

需要注意的点:

(1)detect状态下,Precoding会关闭(无论任何速率);

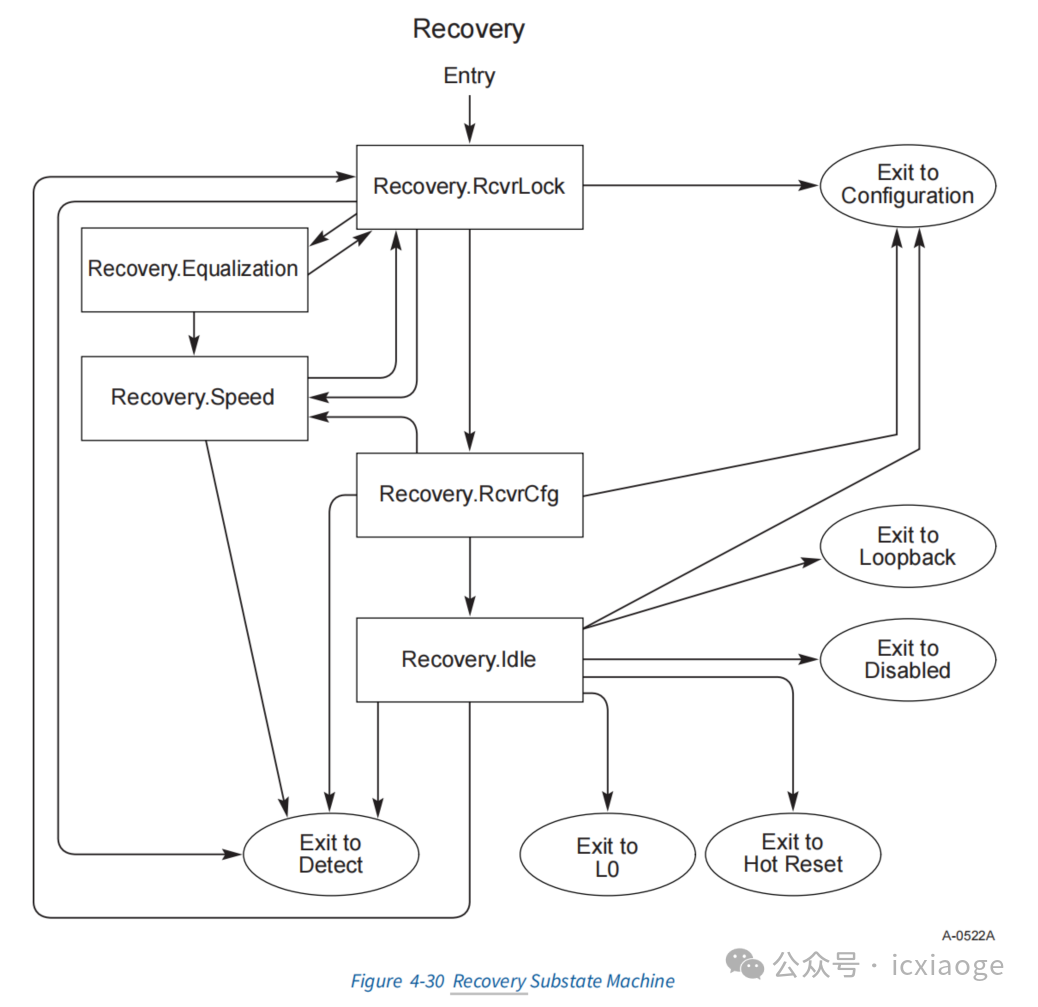

(2)Precoding的打开需要在进入当前速率之前打开,通过在进入到Recovery.Speed之前发送EQ TS2 或者128b/130b EQ TS2 Ordered Sets(其中Transmitter Precode Request位需要设为1)来开启(对于每个高于32GT/s速率的情况,需要独立进行precoding request)(开启前tx);

如果自己的rx在进入Recovery.Speed之前的Recovery.RcvrCfg状态下收到了8个连续的EQ TS2或者128b/130b EQ TS2,这个rx对应的tx的Transmitter Precode Request bit设为1,那么tx在退出Recovery.Speed到更高速率的情况下需要打开precoding功能;一旦打开就持续到下次recovery.rcvrcfg(为了进入Recovery.Speed)中收到收到了8个连续的EQ TS2或者128b/130b EQ TS2(Transmitter Precode Request为0,相同速率下)(开启前rx);

针对32GT/s或者大于其速率的情况,如果在当前速率下已经打开precoding,在recovery状态下发送的TS1中的Transmitter Precoding On比特需要置为1(开启过程中);

对于打开precoding的lane0(tx),需要把32.0 GT/s Status Register中的Transmitter Precoding On 比特置为1,rx收到相关打开precoding的指示之后,也需要把32.0 GT/s Status Register中的Transmitter Precoding On 比特置为1(64GT/S下类似)(开启后需要记录寄存器);

(3)仅仅32GT/s,64GT/s下使用,32GT/s以下无法使用;

(4) 如果在没有执行equalization或者no equalization机制下运行在32GT/s或者更高的速率下,那么会根据上一次eq中的信息来确定是否要执行precoding,如果再次之前从来没有执行过eq,那么precoding就不需要打开。

(5)仅scrambled的bit需要precoded ;

(6)针对64GT/s下的precoding:

TS0不需要precoding;

Only scrambled bits on a 2-bit aligned boundary are precoded, when both bits are scrambled and precoding is enabled.

这篇关于PCIE-Precode的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!