本文主要是介绍【氮化镓】三星200mm 硅基高阈值电压p-GaN器件,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

【High threshold voltage p-GaN gate power devices on 200 mm Si】——IPSD2013

摘要:

三星公司的研究人员介绍了一种高阈值电压、低导通电阻和高速的GaN-HEMT功率器件,该器件在栅极堆叠中使用了p-GaN层。文章提出了三个创新点:首先,首次在200毫米GaN on Si衬底上使用无Au且完全与CMOS兼容的工艺制造了p-GaN栅HEMT;其次,通过采用p-GaN和W栅堆叠,实现了良好的电气特性,包括阈值电压高于2.8V、低栅极漏电流、无迟滞和快速开关;最后,展示了可以承受高达20V栅偏压的TO-220封装的p-GaN栅HEMT器件。这些特性表明,这些p-GaN HEMT器件与传统的Si功率器件栅极驱动器兼容。

引言:

本文介绍了一种高阈值电压、低导通电阻和高速的GaN-HEMT功率器件,该器件在栅极堆叠中使用了p-GaN层。文章提出了三个创新点:首先,首次在200毫米GaN on Si衬底上使用无Au且完全与CMOS兼容的工艺制造了p-GaN栅HEMT;其次,通过采用p-GaN和W栅堆叠,实现了良好的电气特性,包括阈值电压高于2.8V、低栅极漏电流、无迟滞和快速开关;最后,展示了可以承受高达20V栅偏压的TO-220封装的p-GaN栅HEMT器件。这些特性表明,这些p-GaN HEMT器件与传统的Si功率器件栅极驱动器兼容。

外延生长和器件制造

-

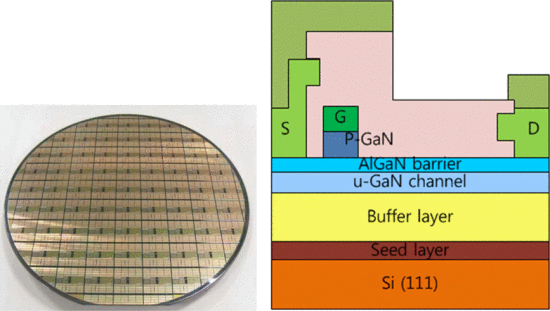

晶片准备:在200毫米的硅(111)晶片上,首先沉积了一个150纳米的AlN(氮化铝)成核层,随后是一个3微米的高阻缓冲层。这些层为后续的HEMT结构生长提供了基础。

-

HEMT结构生长:在缓冲层之上,通过金属有机化学气相沉积(MOCVD)技术生长了HEMT结构,包括一个200纳米的未掺杂GaN(氮化镓)通道层、一个15纳米的Al0.2Ga0.8N(铝镓氮)势垒层和一个70纳米的Mg(镁)掺杂的p型GaN层。通过SIMS(二次离子质谱)测量,Mg在p-GaN层中的掺杂浓度被确定为2×10^19 cm^-3。

-

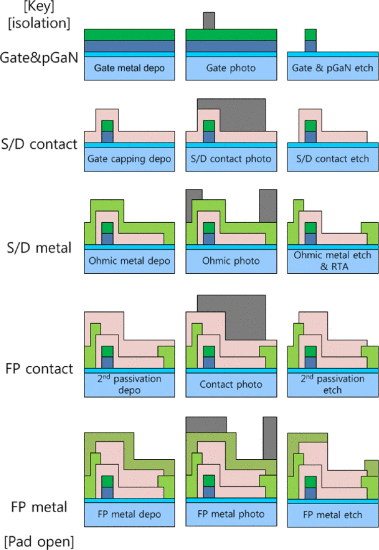

器件制造:在这些外延层之上,使用无金的CMOS兼容工艺制造了p-GaN栅极HEMT器件。制造流程的示意图如图2所示。为了减少后续处理过程中Mg的失活和p-GaN层的损伤,首先通过钨(W)的溅射和W及p-GaN层的刻蚀过程形成了自对准的p-GaN-W栅极堆叠。这个刻蚀过程非常关键,因为它控制了栅漏极漂移区域上方剩余的p-GaN层的厚度。过度刻蚀p-GaN层会导致下面的AlGaN层被刻蚀,而刻蚀不足则会在栅漏极漂移区域上方留下p-GaN层,这两种情况都会影响器件特性。

-

栅极钝化和欧姆接触:在栅极钝化过程中,使用PECVD(等离子体增强化学气相沉积)SiO2进行了钝化。随后,使用基于Ti/Al(钛/铝)的金属堆叠形成了欧姆接触,并通过在N2(氮气)中550°C的后退火过程进一步稳定了这些接触。

-

场板和封装:最后,进行了场板的图案化处理。文章还展示了TO-220封装的p-GaN栅极HEMT器件,并对其直流和交流特性进行了测量。封装的器件能够承受高达20V的栅偏压,并且VTH(阈值电压)约为3V,表明这些器件与硅功率器件的传统栅极驱动器兼容。

电学特性表征:

这部分内容展示了p-GaN栅极HEMT器件的一系列电气特性,包括低栅极漏电流、高速开关能力、良好的电流密度可扩展性和整个晶片的均匀性,以及封装器件的特性。这些特性表明,这些器件适用于高功率应用,并且与现有的硅功率器件栅极驱动器兼容。同时,也指出了在高漏极偏压下可能出现的动态导通电阻问题,需要进一步的研究和改进。

-

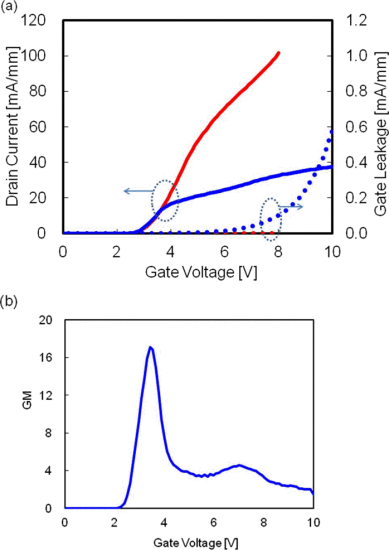

电气特性曲线:图3展示了制造的p-GaN栅极HEMT器件的漏极电流(ID)、栅极电流(IG)和跨导(gm)随栅极电压(VGS)变化的特性。值得注意的是,IG比ID小大约两个数量级,表明器件具有较低的栅极漏电流。此外,gm曲线出现了第二个峰值,这可能是由于随着VGS增加,从栅极注入到漂移区的空穴增加了2DEG(二维电子气)的密度,从而导致了gm的额外峰值。

-

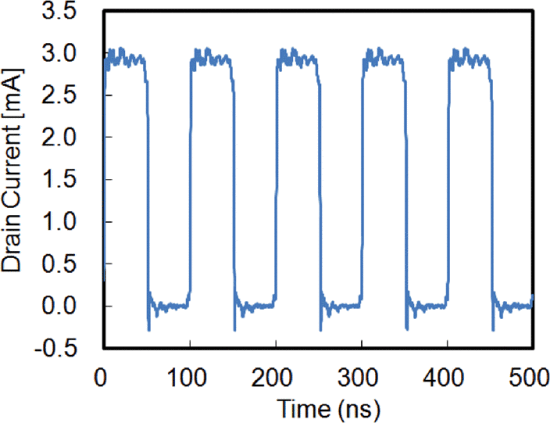

高速开关特性:图4展示了使用Agilent 81110A脉冲发生器进行的ID瞬态测量结果。实验中,在漏极节点施加了1V的直流偏压,并在栅极节点施加了脉冲。脉冲的开关电压为8V/0V,频率为10MHz,占空比为50%。通过直接测量源节点的电流,确认了器件可以实现小于2纳秒的快速开关。

-

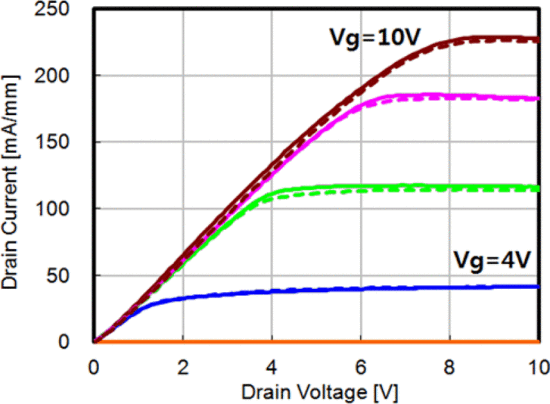

ID的分散性:为了测量ID的分散性,比较了直流和脉冲VGS下的ID-VDS特性。脉冲测量中,VGS从0V开始,脉冲宽度为500微秒。如图5所示,没有观察到显著的分散性。

-

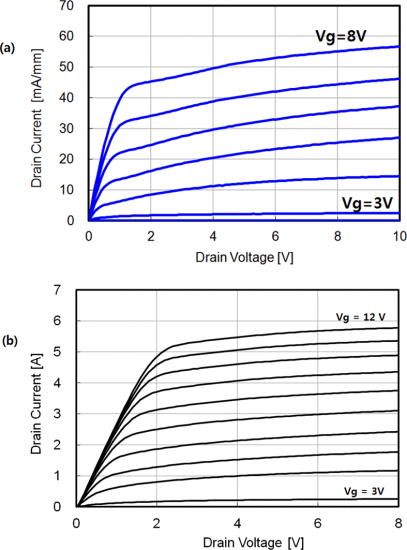

电流密度的可扩展性:图6比较了100微米宽的小尺寸器件和100毫米宽的大功率晶体管的电流密度,以验证器件的可扩展性。大功率晶体管的电流密度较低,但仍然显示出良好的性能,其在VDS = 1V和VGS = 12V时的ID为2.7A,RON为370毫欧姆。

-

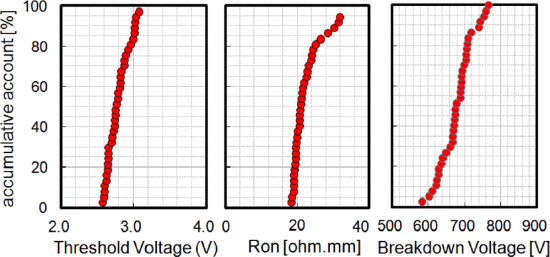

整个晶片的均匀性:图7展示了整个200毫米晶片上制造的p-GaN栅极HEMT器件的VTH、RON和击穿电压(BV)的均匀性。BV是器件在关断状态下可以在漏极和源极之间承受的电压。在这项工作中,BV定义为在VGS = 0V时ID = 1微安/毫米的VDS。器件在整个晶片上表现出了合理的均匀性,中位数值分别为VTH = 2.8V,RON = 20欧姆·毫米和BV = 670V。

-

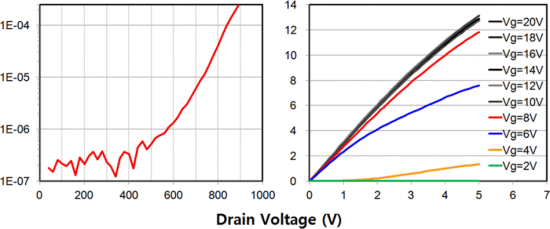

封装器件的特性:图9展示了封装的p-GaN栅极HEMT器件的击穿和ID-VDS特性曲线。封装器件的BV为900V,器件宽度为100毫米。

-

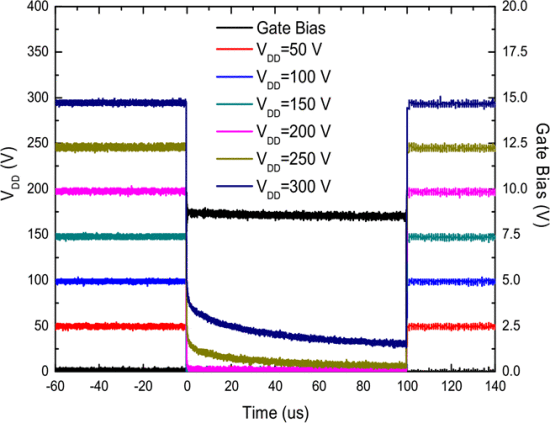

动态导通电阻问题:图10展示了TO-220封装的p-GaN HEMT器件的开关波形。器件在不同漏极偏压条件下,在0V和9V的VGS之间切换。当VDD(漏极电源电压)大于250V时,器件显示出动态RON问题,即初始导通电阻在开关后增加,然后逐渐降低到直流导通电阻值。为了避免这个问题,这些器件的允许最大VDD约为200V。

这篇关于【氮化镓】三星200mm 硅基高阈值电压p-GaN器件的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!