本文主要是介绍Vivado使用(5)——使用块综合策略(Block Synthesis),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一、概述

1.1 使用块级综合的优势

1.2 注意事项

二、设置一个块级综合流程

三、块级综合选项

一、概述

在 AMD Vivado™ 综合中,有许多策略和全局设置可供你自定义设计的综合方式。下图展示了综合设置中可用的预定义策略。而“Vivado 预配置策略表”给出了各种预设策略的横向比较。

你可以使用 RTL 或 XDC 文件中的属性或 XDC 文件覆盖某些设置,例如 -retiming,用于特定的层次结构或信号。然而,一般来说,选项会影响整个设计。

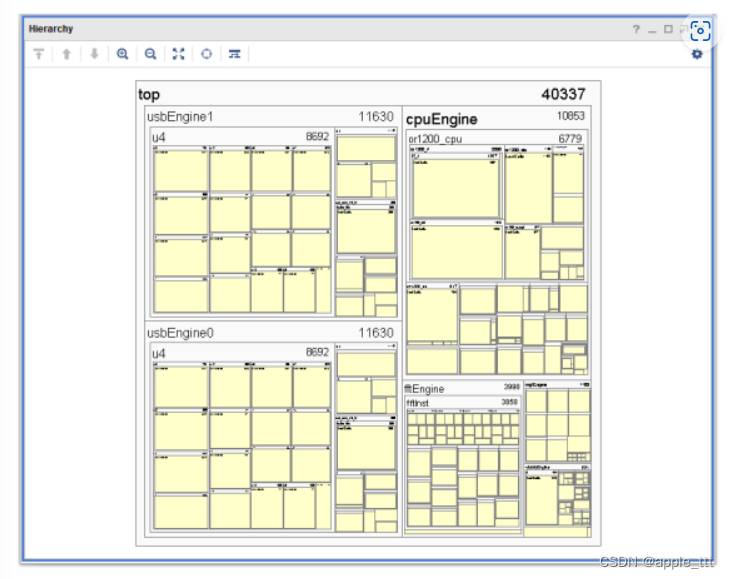

随着设计变得越来越复杂,这样的设置的应用可能会限制你的设计达到其全部潜力。设计中的某些层次结构可能适用于不同的选项,而其他层次结构则不然。下图显示了一个具有许多不同类型层次结构的中等大小的设计。

在 Vivado 设计中,一个解决复杂层次结构的方法是将这些层次结构以脱离上下文(Out of Context,OOC)模式进行综合。OOC 模式是有效的,但会使设计流程变得更加复杂。OOC 流程将被指定为以 OOC 模式综合的层次结构分离出来,并将它们与设计的其他部分分开运行。这意味着每个设计的综合运行次数不止一次。此外,OOC 约束必须与设计其余部分的约束分开,这增加了更多的复杂性。

块级综合流程(BLOCK_SYNTH)使用了一种属性,让你可以在全设计的顶层之外的特定层次结构级别上使用某些全局设置和策略,这与自顶向下流程不同。这样,你可以在不影响整个设计的情况下,针对特定的模块或子系统应用优化策略,以达到更好的综合结果。

1.1 使用块级综合的优势

- 针对性优化:可以针对特定的设计块应用最适合它们的综合策略和设置。

- 减少复杂性:通过单独处理每个设计块,可以简化设计的管理和维护。

- 提高灵活性:允许在不同的设计阶段和不同的层次结构级别上应用不同的综合设置。

1.2 注意事项

- 接口一致性:需要确保设计块之间的接口一致,以便正确集成。

- 约束管理:块级综合可能需要单独管理每个设计块的约束。

总之,块级综合流程(BLOCK_SYNTH)为处理复杂的 FPGA 设计提供了一种有效的方法,使设计者能够在保持设计流程可管理性的同时,针对特定的设计块进行优化。

二、设置一个块级综合流程

要设置块级综合流程(使用 BLOCK_SYNTH 属性),你需要在 XDC 文件中输入一个 Tcl 属性。命令语法如下:

set_property BLOCK_SYNTH.<option_name> <value> [get_cells <instance_name>]其中:

<option_name>是你想要设置的选项。<value>是你分配给该选项的值。<instance_name>是要设置该选项的层次化实例。

例如:

set_property BLOCK_SYNTH.MAX_LUT_INPUT 4 [get_cells fftEngine] 这个例子中,将 fftEngine 实例的 MAX_LUT_INPUT 选项设置为 4,这意味着在 fftEngine 实例中不会有 LUT5 或 LUT6 原语。

注意事项:

- 在实例上设置

BLOCK_SYNTH会影响该实例及其下层的所有内容。例如,如果fftEngine内部实例化了其他模块,这些模块也不会有 LUT5 或 LUT6 原语。- 除了影响这个实例外,

BLOCK_SYNTH属性还会使这个实例的层次结构固化。如果这个层次结构包含 I/O 缓冲器或推断输入/输出缓冲器,请特别注意这一点。- 当你在一个实例上设置

BLOCK_SYNTH属性时,该实例会针对特定选项获得该值;所有其他选项使用默认值。

使用 BLOCK_SYNTH 属性可以为特定的设计块应用特定的综合设置,这有助于优化设计的特定部分,提高整体设计的性能和效率。

你可以在同一个实例上设置多个 BLOCK_SYNTH 属性,以尝试不同的组合。例如,以下命令保持等价寄存器,禁用有限状态机(FSM)推断,并使用 AlternateRoutability 策略:

set_property BLOCK_SYNTH.STRATEGY {ALTERNATE_ROUTABILITY} [get_cells mod_inst]

set_property BLOCK_SYNTH.KEEP_EQUIVALENT_REGISTER 1 [get_cells mod_inst]

set_property BLOCK_SYNTH.FSM_EXTRACTION {OFF} [get_cells mod_inst] 为了防止影响需要不同属性设置的下层实例,你可以在多个层次上嵌套 BLOCK_SYNTH 属性。如果你只想在一个特定层次上设置它,你可以在那个层次上设置它,并在后续层次上使用以下命令将默认值设置回来:

set_property BLOCK_SYNTH.MAX_LUT_INPUT 6 [get_cells fftEngine/newlevel] 如果新层次是 fftEngine 下的唯一层次结构,这个命令确保只有 fftEngine 获得 MAX_LUT_INPUT = 4 属性。你也可以在这个层次上放置一组完全不同的选项,而不是回到默认值。

注意:在执行块级流程时,工具保持设计处于自顶向下模式,意味着整个设计都会经过综合。对于有问题的实例,Vivado 综合保留层次结构,以确保该层次的逻辑不会模糊并且保持在该层次内。这可能会对质量结果(QoR)产生潜在影响。因此,在设置 BLOCK_SYNTH 属性时要小心。只在你知道需要它们的实例上设置它们。

三、块级综合选项

块级流程(Block-Level Flow)支持工具中的一些预定义策略。允许使用的策略包括:DEFAULT、AREA_OPTIMIZED、ALTERNATE_ROUTABILITY 和 PERFORMANCE_OPTIMIZED。XDC 约束语法如下:

set_property BLOCK_SYNTH.STRATEGY {<value>} [get_cells <inst_name>]以下是支持的 Vivado 块级综合设置的列表(假设的示例,具体设置可能会有所不同):

| 选项(Option) | 类型(Type) | 取值(Values) | 描述(Description) |

| RETIMING | 整数 | 0/1 | 0 – Disable Retiming 1 – EnableRetiming |

| ADDER_THRESHOLD | 整数 | 4-128 | 在 Vivado 设计套件中,你可以通过设置特定的属性来改变综合时推断进位链(CARRY chain)中加法器的大小阈值。这个阈值是通过加法器操作数的大小来计算的。指定的值应该大于等于输入宽度的总和。 较高的数字意味着使用更多的查找表(LUTs)来实现加法器。较低的数字意味着使用更多的进位链(CARRY chains)来实现加法器。 调整这个阈值可以帮助你在逻辑资源使用和性能之间找到平衡。使用更多的 LUTs 可能会增加设计的面积,但可能会提高性能。相反,使用更多的进位链可能会减少面积,但可能会降低性能。 |

| COMPARATOR_THRESHOLD | 整数 | 4-128 | 在 Vivado 设计套件中,你也可以通过设置特定的属性来改变综合时推断进位链(CARRY chain)中比较器(comparator)的大小阈值。这个阈值的设置方式与加法器的类似: 较高的数字意味着使用更多的查找表(LUTs)来实现比较器。较低的数字意味着使用更多的进位链(CARRY chains)来实现比较器。 调整这个阈值可以帮助你在逻辑资源使用和性能之间找到平衡。使用更多的 LUTs 可能会增加设计的面积,但可能会提高性能。相反,使用更多的进位链可能会减少面积,但可能会降低性能。 |

| SHREG_MIN_SIZE | 整数 | 3-32 | 在 Vivado 设计套件中,你可以通过设置特定的属性来改变综合时推断移位寄存器链(SRL primitives)之前的寄存器链的大小阈值。这个阈值的设置会影响综合工具是倾向于使用寄存器(registers)还是移位寄存器(SRLs)来实现设计中的寄存器链: 较高的数字意味着在推断 SRL 之前会使用更多的寄存器。较低的数字意味着更倾向于使用 SRLs 来代替寄存器。 调整这个阈值可以帮助你在资源使用和性能之间找到平衡。使用更多的寄存器可能会增加设计的面积,但可能会提高性能。相反,使用更多的 SRLs 可能会减少面积,但可能会降低性能。 |

| FSM_EXTRACTION | 字符 | OFF ONE_HOT SEQUENTIAL GRAY JOHNSON AUTO | 设置合成工具所推断的状态机的编码。 |

| LUT_COMBINING | 整数 | 0/1 | 0 – Disable LUT combining 1 – Enable LUT combining |

| CONTROL_SET_THRESHOLD | 整数 | 0-128 | 在 Vivado 设计套件中,可以通过设置特定的属性来控制在综合推断带有控制信号的寄存器之前,控制信号所需的扇出(fanout)。这个属性的设置会影响控制信号和触发器(flop)的 D 输入之间逻辑分配的方式: 较高的数字意味着控制信号上的逻辑更少,而触发器的 D 输入上的逻辑更多较低的数字意味着更多的控制信号和较少的逻辑在触发器的 D 输入上。 调整这个属性可以帮助优化设计中的控制逻辑,以达到更好的性能或资源利用率。例如,如果设计中有大量控制信号驱动多个触发器,通过增加扇出阈值,可以减少控制信号上的逻辑门数量,从而简化设计并可能降低功耗。 |

| MAX_LUT_INPUT | 整数 | 4-6 | 4 – No LUT5 or LUT6 primitives are inferred 5 – No LUT6 primitives are inferred 6 – All LUTs can be inferred. |

| MUXF_MAPPING | 整数 | 0/1 | 0 – Disable MUXF7/F8/F9 inference 1 – Enable MUXF7/F8/F9 inference |

| KEEP_EQUIVALENT_REGISTER | 整数 | 0/1 | 0 – Merges equivalent registers 1 – Retains equivalent registers |

| PRESERVE_BOUNDARY | 整数 | Any number | 这个选项可以与增量综合(Incremental Synthesis)一起使用,用于标记已知会发生变化的层次结构。使用这个选项可以使层次结构变得静态,并允许增量流程正常工作。设置这个选项的值并不重要,因为仅仅设置这个选项就足够了。 |

| LOGIC_COMPACTION | 整数 | 1 | 在 Vivado 设计套件中,可以通过设置特定的综合选项或属性来调整进位链(CARRY chains)和查找表(LUTs)的排列方式,使得逻辑更加紧凑,使用更少的切片(SLICES)。这种优化可以减少所需的硬件资源,从而降低设计的面积并可能提高性能。 |

| SRL_STYLE | 字符 | REGISTER SRL SRL_REG REG_SRL REG_SRL_REG | 设置推断的SRL的默认实现。 |

注意:这些设置中的每一个都可以用来优化特定的设计块以满足不同的设计目标,如面积优化、路由灵活性或性能优化。在应用这些设置时,建议仔细考虑设计的具体需求,并在必要时进行实验以找到最佳的配置。

这篇关于Vivado使用(5)——使用块综合策略(Block Synthesis)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!