本文主要是介绍ARMv8 Cortex-a 编程向导手册学习_4. A64指令集,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

/* TODO 本系列文章是对 ARMv8 Cortex-a 系列编程向导手册拙劣的翻译和注解,若有出入,以官方文档为准 */

Chapter 6 A64指令集

大多数程序员并不需要使用汇编语言编写应用程序,但是汇编代码可以有效的优化代码性能。而且当编写编译器,或者使用 CPU 底层功能,或者编写启动代码、设备驱动以及操作系统中断相关的任务切换时,此时不能直接使用 C 语言,而需要使用汇编;当调试代码时,我们需要有效的理解汇编指令与 C 程序流的映射关系。

6.1 指令助记符

A64 的指令可以操作32位以及64位值,这两种情况下采用不同的编码方式,编译器根据寄存器名字,来区分当前操作的是 32 位值还是 64 位值。示例如下:

ADD W0, W1, W2 // 32 位寄存器的加法

ADD X0, X1, X2 // 64位寄存器的加法

ADD X0, X1, W2, SXTW // add sign extended 32-bit register to 64-bit extended register

ADD X0, X1, #42 // 64 位寄存器与立即数的加法

ADD V0.8H, V1.8H, V2.8H // NEON 16-bit add, in each of 8 lanes

6.2 数据处理指令

A64 提供一些重要的算数与逻辑操作指令,应用于寄存器与寄存器之间,或者寄存器与立即数之间,乘法与除法指令被当作特殊的数据处理指令。

绝大多数数据处理指令使用一个目的寄存器和两个源操作数,这些指令的通用格式如下:

Instruction Rd, Rn, Operand2

数据处理指令包括:

- 算数与逻辑操作指令

- 赋值与移位指令

- 符号与0扩展指令

- 位域操作指令

- 条件比较与数据处理指令

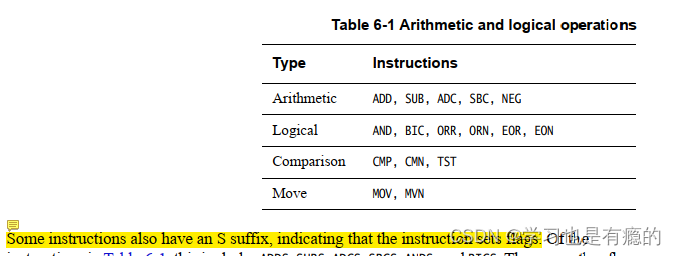

6.3.1 算数与逻辑操作

上图中列出了:

- 算数指令

- 逻辑指令

- 比较指令

- 赋值指令

一些指令拥有 s 后缀,表示该指令会根据指令执行的结果设置 PSTATE 的 NZCV 标志位。

指令使用示例如下:

ADD W0, W1, W2, LSL #3 // W0 = W1 + (W2 << 3)

SUBS X0, X4, X3, ASR #2 // X0 = X4 - (X3 >> 2), set flags

MOV X0, X1 // Copy X1 to X0

CMP W3, W4 // Set flags based on W3 - W4

ADD W0, W5, #27 // W0 = W5 + 27

MOV X1, #0x800 // x1 = 0x8000

BIC X0, X0, X1 // x0 &= ~x1

比较指令只设置标志位,不会保存结果 ,在上述算符与逻辑指令中,能处理的立即数的范围是 12 位,这个12位可以是 64 位值中任意的连续的 12 位。

6.2.2 乘法与除法指令

MUL X0, X1, X2 // X0 = X1 * X2

UDIV W0, W1, W2 // W0 = W1 / W2 (unsigned, 32-bit divide)

SDIV X0, X1, X2 // X0 = X1 / X2 (signed, 64-bit divide)

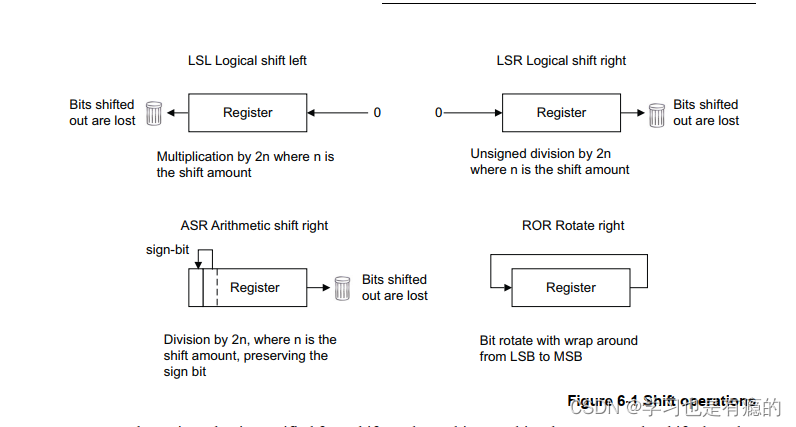

6.2.3 移位操作指令

移位操作指令存在如下类型:

- 逻辑左移:LSL,该指令等于乘以2的幂次

- 逻辑右移:RSL, 该指令等于除以2的幂次

- 算法右移:ASR,该指令等于除以2的幂次,但会保留符号位

- 循环右移:ROR, 该指令的 LSB 位会填充到 MSB 位

4种移位操作的示例图如下:

移位操作可以使用32位或64位的寄存器,移动的位数量可以是通过一个立即数指定,或者寄存器指定,如果通过寄存器指定,那么针对32位值的移位操作,寄存器的低5位指定位移动数量,如果针对64位值的移位操作,寄存器的低6位指定位移动数量。

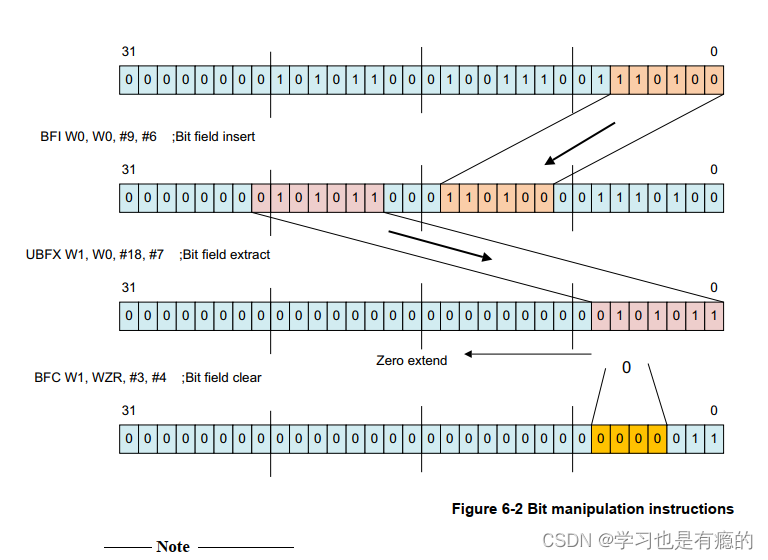

6.2.4 位域与字节操作指令

与 ARMv7 类似, ARMv8 也提供了位域插入指令 BFI(Bit Fieled Insert) 以及位域提取指令S/UBFX(Bit Fieled Extract)。,用法与示例如下图:

6.2.5 条件指令

AArch64 的程序状态位域 PSTATE 提供了4个条件标志位:NZCV(与 ARMv7 类似),标志位描述如下表:

| 标志位 | 描述 |

|---|---|

| N | Negative, 负值标志位 ,表示指令结果为一个负值 |

| Z | Zero, 0 标志位,如果指令结果是0,则置位该标志位,表示两个操作数拥有相同的值 |

| C | Carry, 进位标志位 |

| V | Overflow, 溢出标志位,上溢或下溢 |

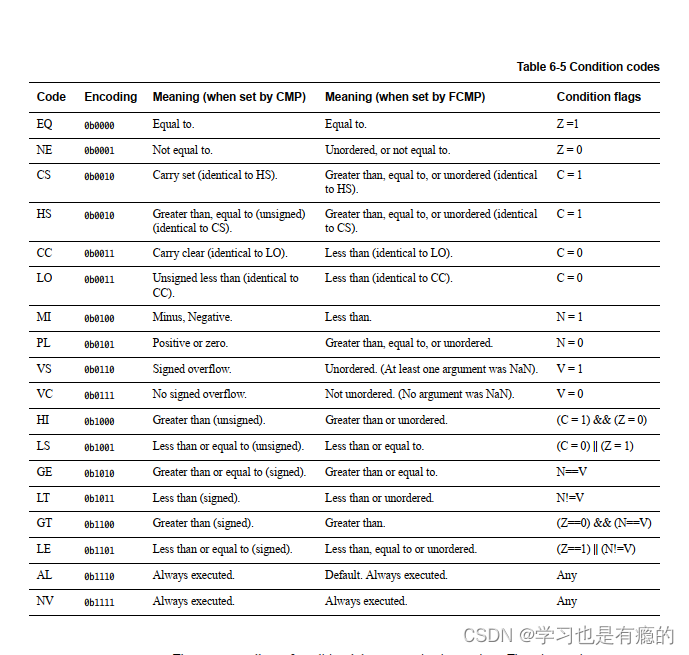

存在如下条件码:

上图这些条件码,在 PSTATE 的对应 Condition Flag 为对应的值时为真。

比如,如下:

b.eq __main /* 如果此时 Z 置位,那么跳转到 __main() */

b.ne __secondary_init /* 如果此时 Z 没有置位,那么跳转到 __secondary_init()*/

着重注意的指令:

条件比较指令:cmp 和 cmn,如果比较的结果为真,cpu 会设置条件标志位。

条件选择指令:csel,会根据指令跟随的条件码,选择相对应赋值操作。示例如下:

CMP w0, #0 // if (i == 0)

SUB w2, w1, #1 // r = r - 1

ADD w1, w1, #2 // r = r + 2

CSEL w1, w1, w2, EQ // select between the two results

上述汇编对应如下的 C 语句

if (i == 0) r = r + 2; else r = r - 1;

6.3 内存访问指令

跟 ARMv7 类似,ARMv8 架构也是一个 Load/Store 架构,即,不提供直接访问内存地址的数据处理指令(6.2章节提供的指令都时不能直接访问内存地址)。

数据首先被加载到通用目的寄存器中,然后才能使用数据处理指令进行修改,最后再存储到指定的地址中。

内存地址的访问流程即是:加载-数据处理-存储。

6.3.1 内存加载指令格式

通用的内存加载指令格式如下:

LDR Rt, <addr> //将 addr 地址的值加载到 Rt 寄存器中

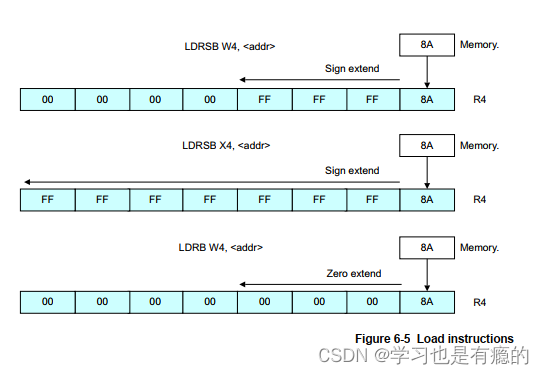

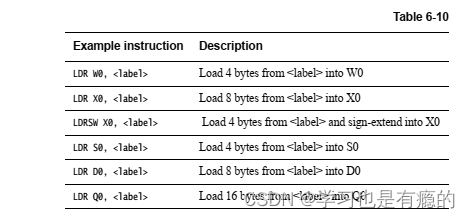

我们可以在 LDR 指令后加后缀的形式,选择加载的数据宽度:

| LSRB | 加载字节数据,目的寄存器的高位填充0 |

|---|---|

| LSRSB | 加载字节数据,目的寄存器的剩余高位填充符号位 |

| LSRH | 加载半字数据,目的寄存器的剩余高位填充0 |

| LSRSH | 加载半字数据,目的寄存器的剩余高位填充符号位 |

| LSRWS | 加载字数据,目的寄存器的剩余高位填充符号位 |

上述内存加载指令的用法示例图如下:

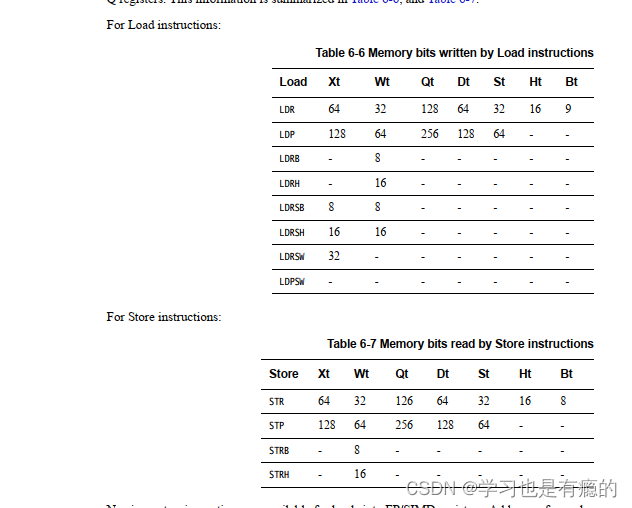

6.3.2 内存存储指令

Store 指令常用格式如下:

STR Rn, <addr> //将 Rn 的值保存到 addr 地址处

如果要存储的数据小于寄存器的宽度,那么我们可以使用‘B’或‘H’后缀,此时会将寄存器的低位存储到指定的地址。

6.3.3 浮点与 NEON 精度加载与存储

内存加载与存储指令也可以访问浮点寄存器。

6.3.4 加载指定地址处的值

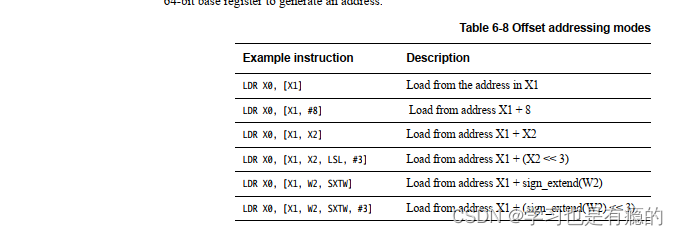

offset mode:偏移模式

偏移寻址模式将一个立即数值或一个可修改的寄存器值添加到目的寄存器中用于生成地址:

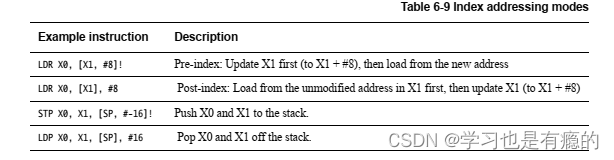

index mode :索引模式

索引模式与偏移寻址模式相似,但索引模式会更新基寄存器的值:

PC-relative mode:PC相关模式

A64 增加了其他的寻址模式,比如可以从一个标号地址加载数据,如下:

6.3.5 访问多个内存位置

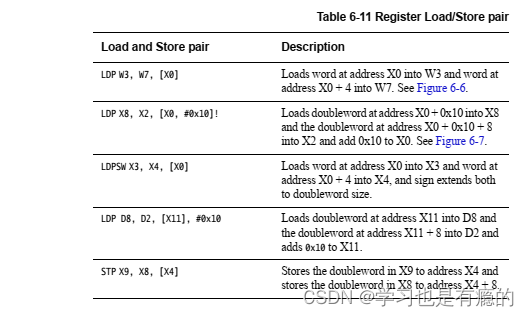

A64 不支持 LDM 与 STM 指令,只支持 LDP 与 STP 指令。

LDP 与 STP 指令一次可以访问两个通用目的寄存器来读或写。

指令使用示例如下:

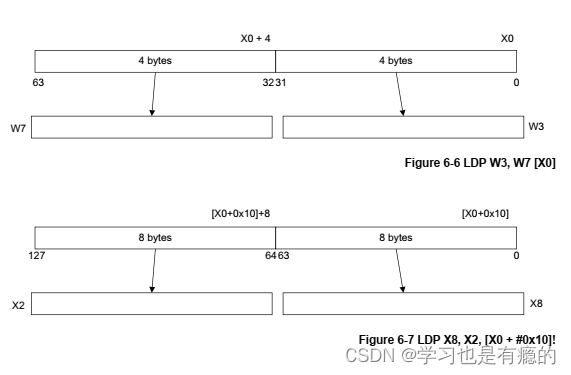

图解如下:

6.3.6 非特权访问

略

6.3.7 内存提取指令

略

6.3.8 非临时加载与存储对

略

6.3.9 内存访问原子性

当使用 LDR 与 STR 指令,通过通用目的寄存器访问地址对齐的内存时,硬件保证这个访问是原子性的。

当使用 LDP 与 STP 指令,通过通用目的寄存器对访问地址对齐的内存时,硬件保证这两个寄存器的访问是两个单独的原子操作。

浮点内存访问时,硬件不保证原子性。

6.3.10 内存屏障与栅栏指令

- DMB, 数据内存屏障

- DSB, 数据同步屏障

- ISB, 指令同步屏障

6.3.11 同步?

略

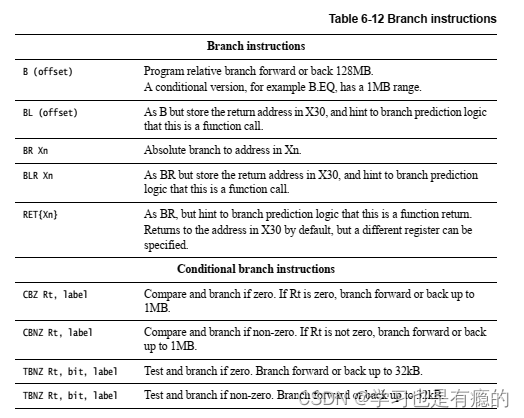

6.4 程序流控指令

A64 提供大量的不同种类的程序跳转指令。

当使用 BL 或 BLR 调用函数时,会使用 X30 保存函数返回地址。

6.5 系统控制与其他指令

6.5.1 异常处理指令

存在3种异常生成指令:

| 异常生成指令 | 描述 |

|---|---|

SVC #imm16 | 生成 EL1 异常 |

HVC #imm16 | 生成 EL2 异常 |

SMC #imm16 | 生成 EL3 异常 |

上表中,立即数的值保存在 ESR_ELn 寄存器中,可供异常服务函数处理。

当从异常退出时,我们使用ERET 指令,这个指令会使用 SPSR_ELn 寄存器的值设置 PSTATE,并会跳转到 ELR_ELn 保存的地址处开始执行代码。

6.5.3 系统寄存器访问指令

系统寄存器的访问使用 MSR 与 MRS 指令

这篇关于ARMv8 Cortex-a 编程向导手册学习_4. A64指令集的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!