本文主要是介绍Chiplet技术与汽车芯片(二),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

1.回顾

2.Chiplet的优势

2.1 提升芯片良率、降本增效

2.2 设计灵活,降低设计成本

2.3 标准实行,构建生态

3.Chiplet如何上车

1.回顾

上一篇,我们将来芯粒到底是什么东西,本篇我们来看芯粒技术的优势,以及它是如何上车的?

2.Chiplet的优势

2.1 提升芯片良率、降本增效

随着汽车电子电气架构的演进,对于单颗芯片的算力需求也越来越大,同时芯片的die面积也越来越大。而面积的增加无疑会导致芯片良率降低。

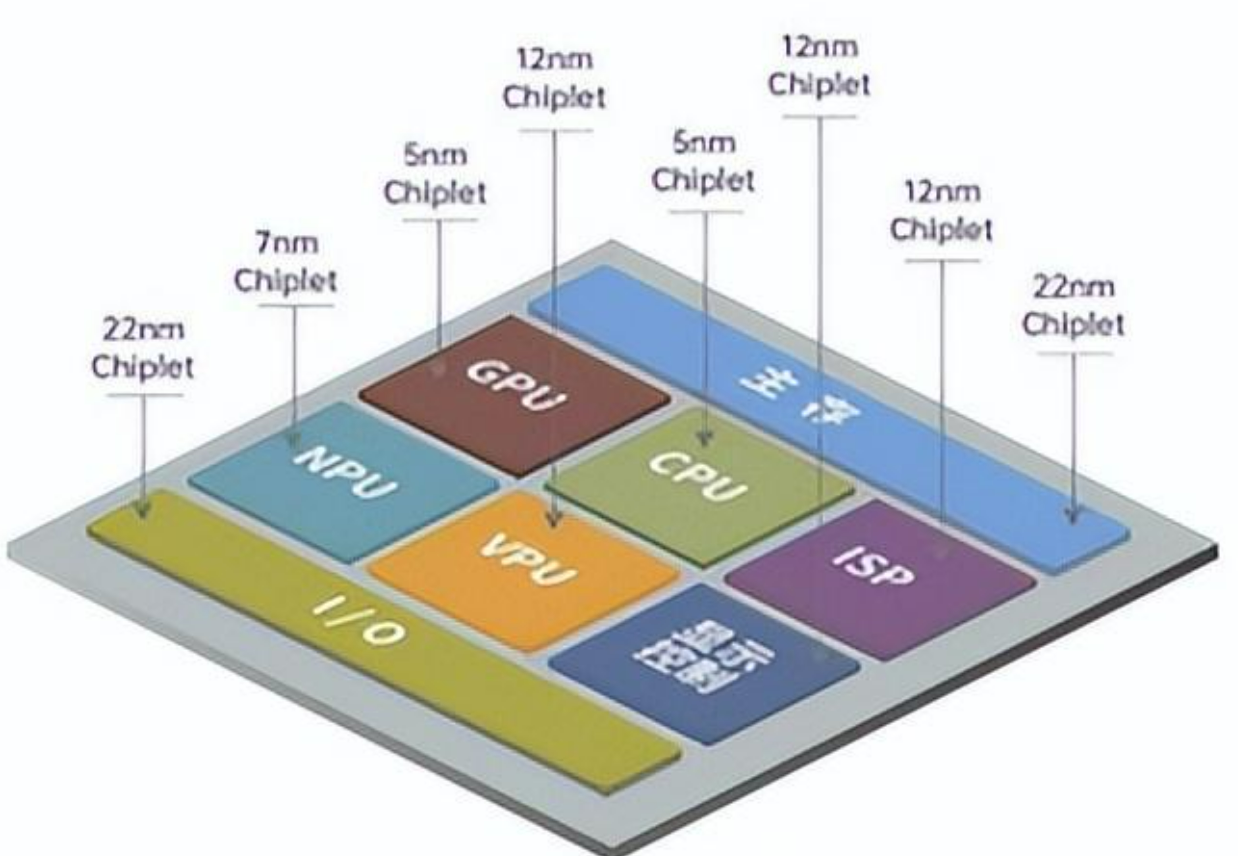

Chiplet封装技术将SOC不同功能分解成独立的小芯粒,以此减小单颗Die的面积,从而达到提升芯片良率;并由于把功能分发到不同芯粒中,可以根据芯粒的实际需要来选择工艺制程,分开制造,最后再通过先进封装技术集成组装,形成系统芯片。

2.2 设计灵活,降低设计成本

由于芯粒可以独立设计和组装,因此芯片设计厂商可以根据实际需要来选择不同规格甚至不同供应商的芯粒进行组合,提高了芯片设计的灵活性;并且制造商可以依赖于预定好的芯片工具箱来设计新产品,缩短芯片的上市时间。

2.3 标准实行,构建生态

2022 年 3 月 3 日,AMD、ARM、Intel、台积电等半导体巨头宣布共同成立 Chiplet 行业联盟,目标共同打造Die2Die的Chiplet互联标准,并在制定推行了UCIe(通用 Chiplet Interconnect Express),在芯片封装层面确立互联互通的高速接口标准。

正如AUTOSAR对于汽车基础软件,UCIe对于Chiplet同样意义重大,可以帮助设计人员加深理解,加快开发设计进度。

3.Chiplet如何上车

很明显,Chiplet技术会在整车电子电气架构演进到中央计算平台后大放异彩。

当前基于域内集成的架构仍由多颗SoC和MCU共同组成,一旦演进到中央计算平台,汽车主控芯片势必由MCU向SOC异构芯片演进。

我有这样一个猜想:以蔚来最新的中央计算平台ADAM为例,该控制器集成了1颗高通骁龙8295、4个英伟达Orix X智驾芯片;而这几颗芯片基本都会采用PCIe进行通信,因此如果能使用Chiplet技术,将上述CPU、GPU等集成到一颗芯片,使用UCIe进行通信,那么通信延迟是否能得到极大缓解;进一步,如果再将整车功能按不同功能安全和信息安全等级要求,分别设计到不同的Die里,从而就可以实现功能域的有效物理隔离。

这篇关于Chiplet技术与汽车芯片(二)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!