本文主要是介绍用DUV光刻机制造3纳米芯片!,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材华为海思麒麟9000S的面市,预示着中国已经可以使用 DUV 光刻技术实现了 7 纳米级节点的芯片制造,这提出了一个问题:通过多重曝光方法,DUV 光刻技术能走多远?

据国外科技媒体semiwiki报道,CSTIC 2023的最新发表指出,中国研究小组目前正在考虑将基于 DUV 的多重图案化扩展到 5 纳米,甚至考虑在一层使用 6 个掩模。比较基于DUV和EUV的方法在前进到3纳米时,可以得出一个有趣的结论。

LELE光刻

最基本的多重图案化形式是所谓的 "光刻-蚀刻-光刻-蚀刻"(LELE)方法,其本质是在进行基本光刻后再进行两次蚀刻。

当第二个特征插入到两个印刷的第一个特征之间时,这使得节距减半。推而广之,LE3(3xLE)和 LE4(4xLE)可能会随之出现。不过,随着自对准间隔光刻技术的出现,使用这些方法将间距减小到原始间距的一半以下已不再受到青睐。

自对准间隔光刻技术(SADP)

与 LELE 相比,自对准间隔层图案化的优势在于不需要额外的光刻步骤,从而节省了额外的成本。间距沉积和随后的蚀刻,以及间隙填充和随后的蚀刻,取代了涂层、烘烤、曝光、烘烤、显影的光刻顺序。虽然成本大大降低,但仍需要精确的工艺控制,如间隔层厚度和蚀刻速率选择性。一次性间隔层的应用可在给定间距内实现特征加倍。因此,这通常被称为自对准双图案化(SADP)。再次应用则会产生自对准四倍图案化 (SAQP),这也是意料之中的。

减法光刻(Subtractive Patterning)

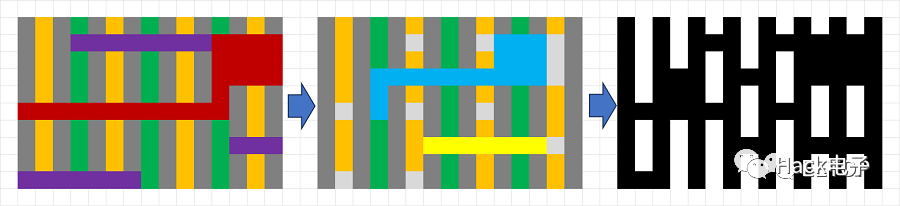

虽然 LELE 和 SADP 都会自然地在图案中添加特征,但有时也有必要去除这些特征的一部分,以便进行最终布局。切割掩模表示需要去除线段的区域。在阻挡线形成蚀刻时,这些区域也称为阻挡位置。反向掩模称为保留掩模。如果相邻的线也可以蚀刻,则将断线限制在单线宽度会产生放置问题。如果可以安排用不同的蚀刻材料制作交替线,就能以更好的公差制作断线(图 1)。

图 1. 自对齐块/切割仅删除交替线的部分

图 1. 自对齐块/切割仅删除交替线的部分 对于给定的互连线,中断之间的距离预计至少为两个金属节距。因此,当金属间距为分辨率极限的 1/4 到 1/2 时,每行需要两个掩模。

图 2. 两组蚀刻需要两组块/切割掩模

图 2. 两组蚀刻需要两组块/切割掩模 交替线排列

通过 LELE、SADP、SAQP 或 LELE 和 SADP 的混合体 SALELE(自对齐 LELE),可以自然地排列交替线。SALELE 已被认为是最窄金属间距 EUV 的默认使用方法。

DUV 与 EUV 成本评估

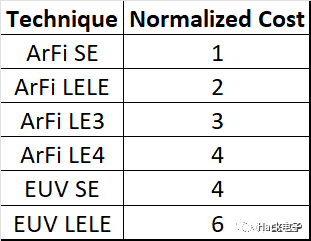

与EUV相比,DUV多模化的成本一直在不断上升。现在是时候进行更新的重新评估了。首先,我们使用最新的成本估算(2021)规范化模式 (图3)。

图3 图案化的标准化成本

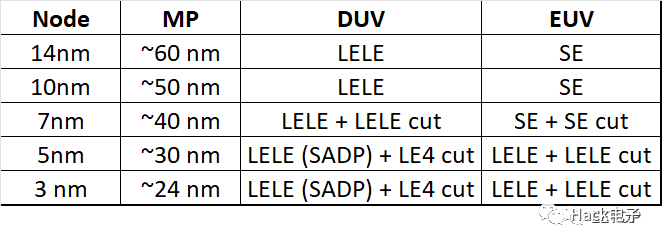

图3 图案化的标准化成本 接下来,我们为各个节点使用DUV和EUV的代表性模式样式(图4)。

图4 DUV与EUV模式成本与节点

图4 DUV与EUV模式成本与节点 有几处需要说明:

对于 7 纳米的 DUV,40 纳米的间距是唯一能分辨出线条特征的点,因此这些线条必须在单独的曝光中切割。

对于 7nm EUV,使用单独的线切割,因为在 40 nm 间距下,所需的分辨率(~20 nm)小于 EUV 系统的点扩散函数(~25 nm)。由于焦深和光瞳填充的限制,高数值孔径 EUV 系统对于这种间距也没有优势。

对于 3/5nm DUV,LELE SADP 在 40nm 以下间距时比 SAQP 更灵活。

对于 3/5nm EUV,使用 LELE 的驱动力在于 <17 nm 半间距和 <20 nm 隔离线宽时的随机行为。当我们接近 10 纳米尺寸时,电子散射剂量依赖性模糊也将变得令人望而却步。系统的光学分辨率(即 NA)不再重要。

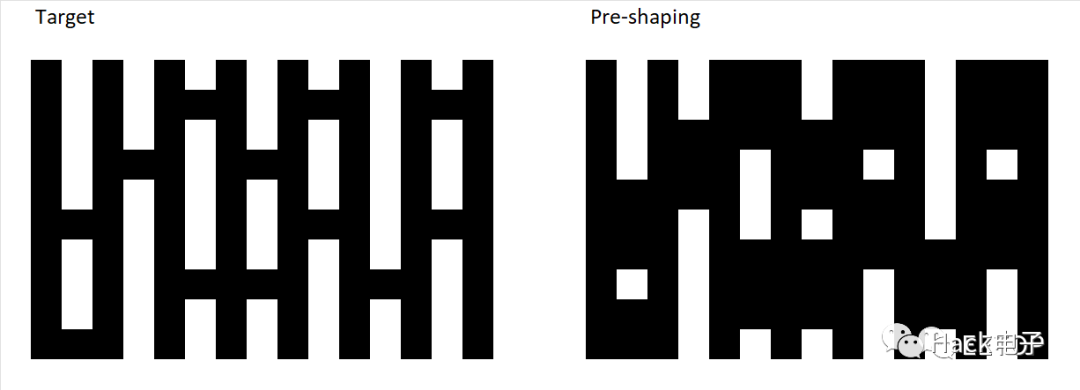

图案塑形不被认为是消除切割的一种方法,因为这将使预形状光刻变得更加困难(图5)。此外,倾斜的离子束刻蚀通常用于平坦预先存在的地方,减小刻蚀掩模的高度。

图 5. 对于图案成形,成形前的图案非常不适合光刻。

图 5. 对于图案成形,成形前的图案非常不适合光刻。 大多数情况下,我们可以直接判断DUV LELE比EUV单次曝光(SE)便宜得多。此外,DUV LE4 比 EUV 双图案化更便宜。虽然LELE比SE需要额外的步骤,但还需要考虑EUV系统维护与DUV系统维护以及能耗。DUV LELE 使用的能量是 EUV SE 的一半,DUV SADP 约为 2/3,甚至 DUV LE4 使用的能量也只有 EUV SE 的 85%。

所有这些都凸显出,无论选择 DUV 还是 EUV,转向先进节点都需要面临不断增长的成本。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

这篇关于用DUV光刻机制造3纳米芯片!的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!