本文主要是介绍FPGA Verilog 曼彻斯特编码译码 同步 DPLL(一),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

FPGA Verilog 曼彻斯特编码译码 同步 DPLL(一)

第一章:曼彻斯特编码实现

文章目录

- FPGA Verilog 曼彻斯特编码译码 同步 DPLL(一)

- 前言

- 曼彻斯特编码定义

- 曼彻斯特编码规则以及频率确定

- 编码规则

- 频率确定

- 一、实验代码

- 二、上板测试

- 平台

- 总结

前言

曼彻斯特编码定义

曼彻斯特码,即曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技 [1] 术,被物理层使用来编码一个同步位流的时钟和数据。曼彻斯特编码被用在以太网媒介系统中。曼彻斯特编码提供一个简单的方式给编码简单的二进制序列而没有长的周期没有转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。在这个技术下,实际上的二进制数据被传输通过这个电缆,不是作为一个序列的逻辑1或0来发送的(技术上叫做反向不归零制(NRZ))。相反地,这些位被转换为一个稍微不同的格式,它通过使用直接的二进制编码有很多的优点。

曼彻斯特编码规则以及频率确定

编码规则

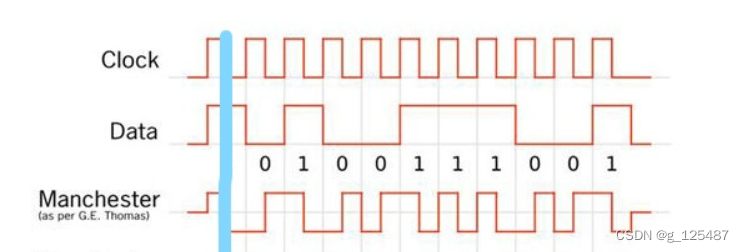

在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从低到高跳变表示“1”,从高到低跳变表示“0”。还有一种是差分曼彻斯特编码,每位中间的跳变仅提供时钟定时,而用每位开始时有无跳变表示“0”或“1”,有跳变为“0”,无跳变为“1”。

反正就两种,一种是数据是“1”,编成“10”,或者是数据是“1”,编成“01”。

频率确定

从图上可以明显看出,原始数据与时钟之间的频率关系为:fclk=2*fdata,例如原始数据是1Mhz,则编码时钟的频率是2Mhz。最终得出的曼彻斯特编码本身的单个数据周期=时钟的单个周期。

一、实验代码

quatus软件平台

Verilog语言

module bianma(

input clk,

input rst_n,

input data_in,

output data_code

);

reg [1:0] temp; //存储1-01 0-10

reg flag =1 ;//编码always @ (posedge clk)

beginif(flag == 1)beginif(data_in==1'b1)begintemp <= 2'b10;endelse begintemp <= 2'b01;endend

end

always @ (posedge clk)

beginflag <= ~flag;

end

assign data_code = (flag == 0)?temp[1]:temp[0];endmodule

代码参考

- 注意clk要结合自己需求进行分频!

二、上板测试

平台

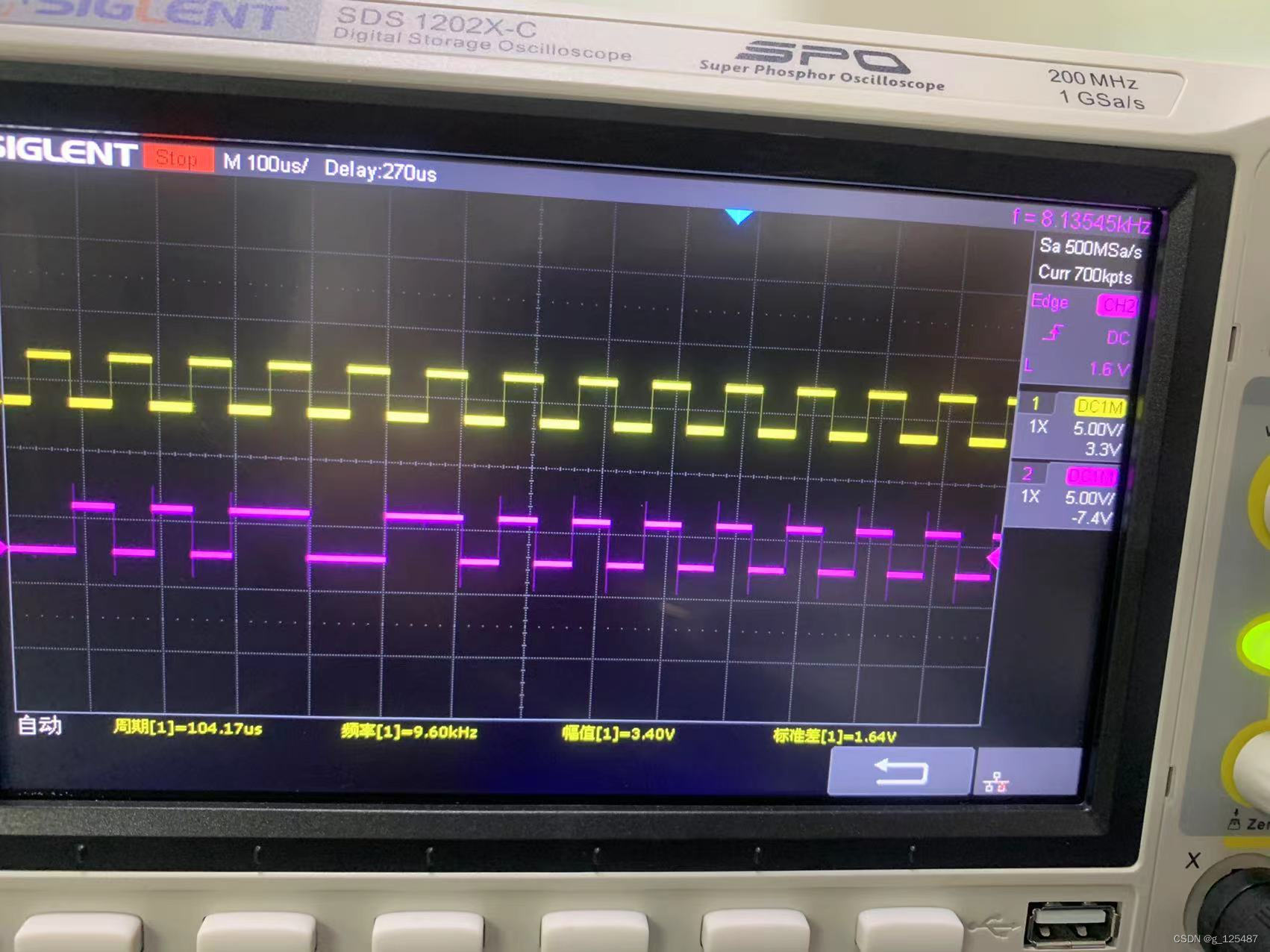

板子为maxII系列 上板后示波器观察如图所示,编码正确,未出现错误

通道1(黄色线)是编码的时钟

通道2(紫色线)是译码的时钟

—

—

总结

本章主要讲解曼彻斯特编码的过程,编码相对简单,大致原理相信看前言的图也能很快的理解,具体注意的点就是找到自己需要的编码时钟。下一章将讲解曼彻斯特译码中提取时钟的相关问题,其中涉及到数字锁相环dpll,以及高速数据并行串行处理等等问题。

喜欢的点赞加收藏哦~ 码字不易 其中大部分知识是参考其他博主的~

这篇关于FPGA Verilog 曼彻斯特编码译码 同步 DPLL(一)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!