本文主要是介绍FPGA基础架构【参考ug998】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

-

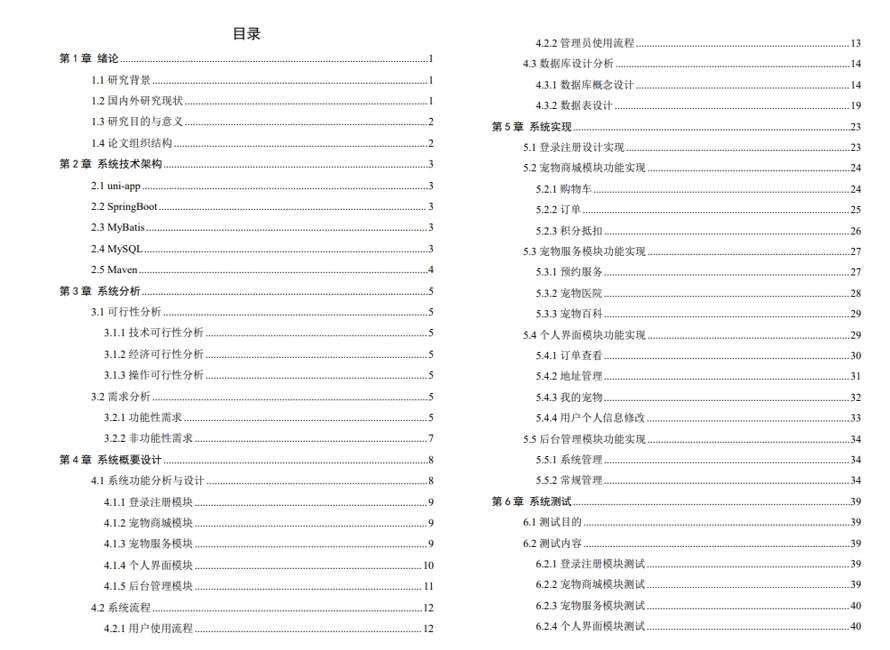

基础元件结构组成

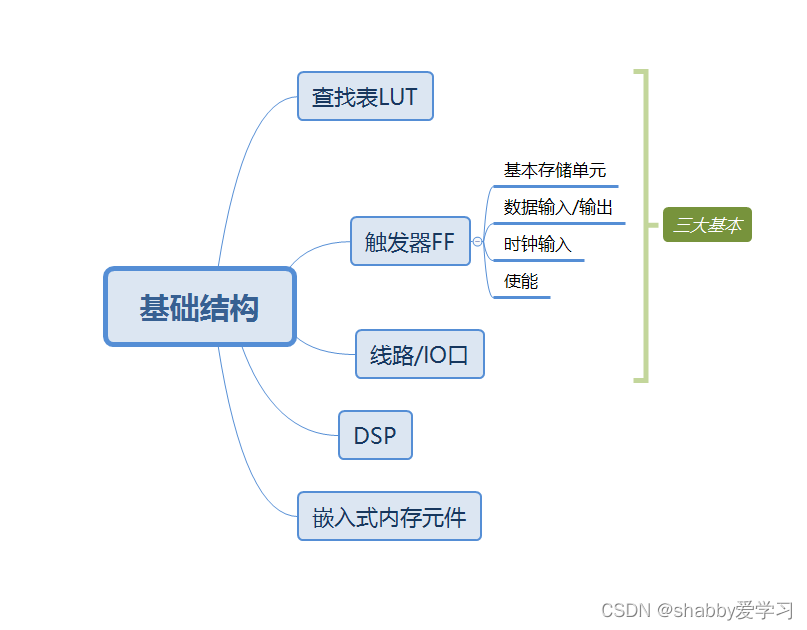

CLB是指可编程逻辑功能块(Configurable Logic Blocks),CLB是FPGA内的三个基本逻辑单元。 -

FPGA并行性

-

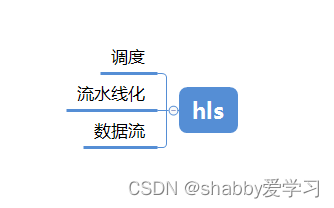

调度:确定不同运算之间的数据和控制依赖关系的过程,用于判定执行每项运算的时间。

-

流水线化:流水线化是一种数字设计技巧,支持设计人员避免数据依赖关系,提升算法硬件实现中的并行性。原始软件实现中的数据依赖关系将保留用于实现功能等效性,但所需电路将拆分为连续的独立阶段。

-

数据流:数据流是另一种数字设计技巧,其概念与流水线化相似。数据流的目标是在粗颗粒度层面上表述并行化。就软件执行而言,这种变换适用于在单一程序内并行执行函数。

-

这篇关于FPGA基础架构【参考ug998】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!