本文主要是介绍Marin说PCB之如何只保留特殊信号过孔焊盘的设计总结,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

小编午休的时候正在梦中买了彩票,等就要开奖的时候被旁边的仿真老家伙把我喊醒了,500W啊,我的天啊。我起来想给这个男人一个重拳出击,虽然说是梦吧,想想还是不错的,毕竟是500W啊。需要小编我做多少快板子才能够啊?想想都是眼泪啊。。。。。。

好了我们言归正传啊,仿真同事问我是否我们板子上主芯片有PDN要求的电源网路的过孔是不是都把非功能焊盘去掉了?我当时很吃惊的看着他说“大哥啊,不是你要求我这样做的吗”?你说的板子上有高速线的尽量把信号VIA的非功能焊盘去掉,而且我们的之前Allegro出图的时候的设置都是把所有网络的VIA的非功能焊盘去掉了。

他也吃惊的看着我说,你肯定没有把我之前给你说的要求全部听完,我说的是正常的网络你是可以这样设置去做的,但是对于那些有电源完整性要求的网络的VIA你就不能这样做了啊。

我说你除非拿出来证据,否则空口无凭,谁相信你啊。好了,仿真的同事成功的被我给被激怒了,说我马上给你做一个仿真结果比对,你就知道了为啥有的电源网络上的VIA是不能去掉非功能焊盘的。

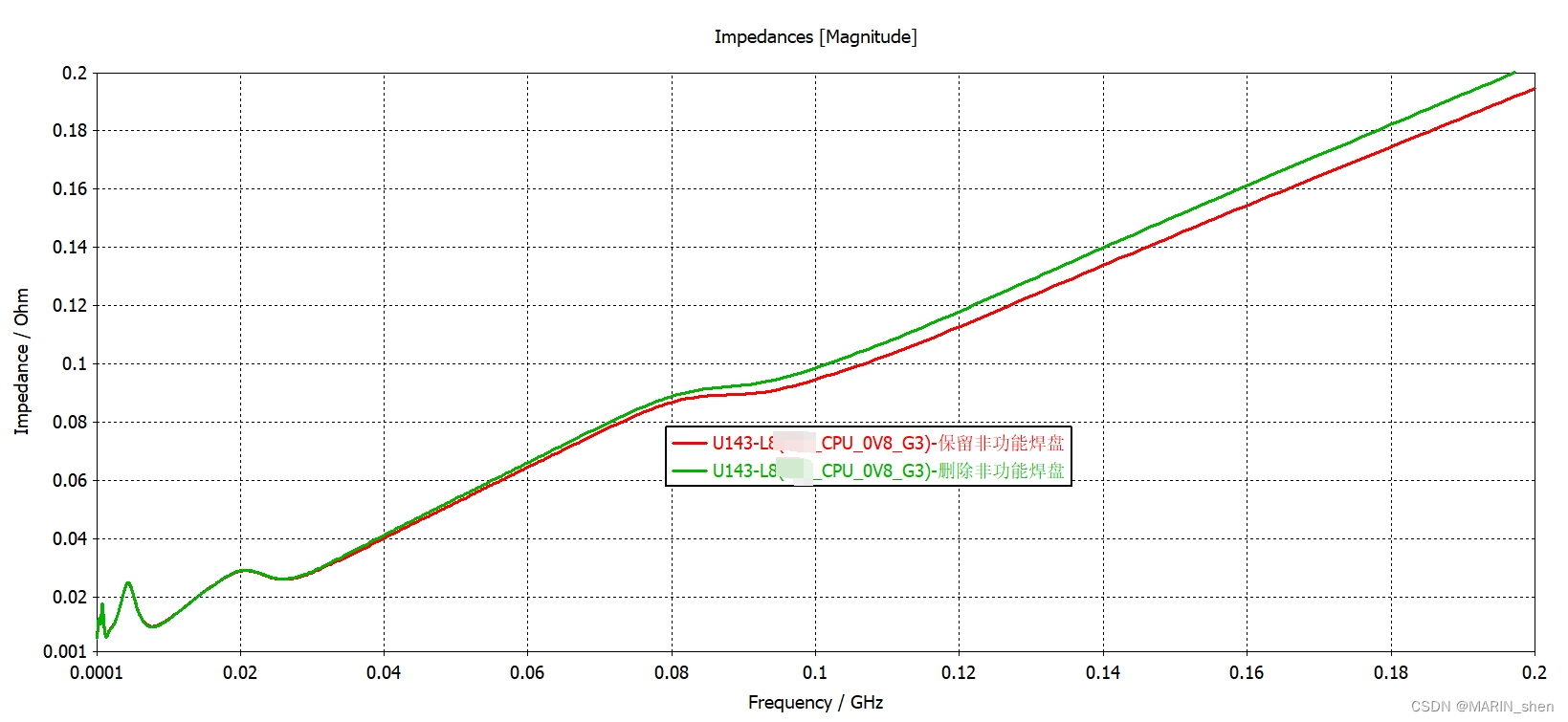

下图所示的就是仿真的同事做了一个结果比对:

我看了上图的结果高兴的说到你看这个影响很小嘛,从图片上从电源网络从60M-100M阻抗才有变化,而且差值不是很大,最多是差0.01ohm,这个设置对这个电源网络看起来影响不多啊。但是我还是高兴的太早了,他过了一分钟后又给我发了一份仿真比对图:

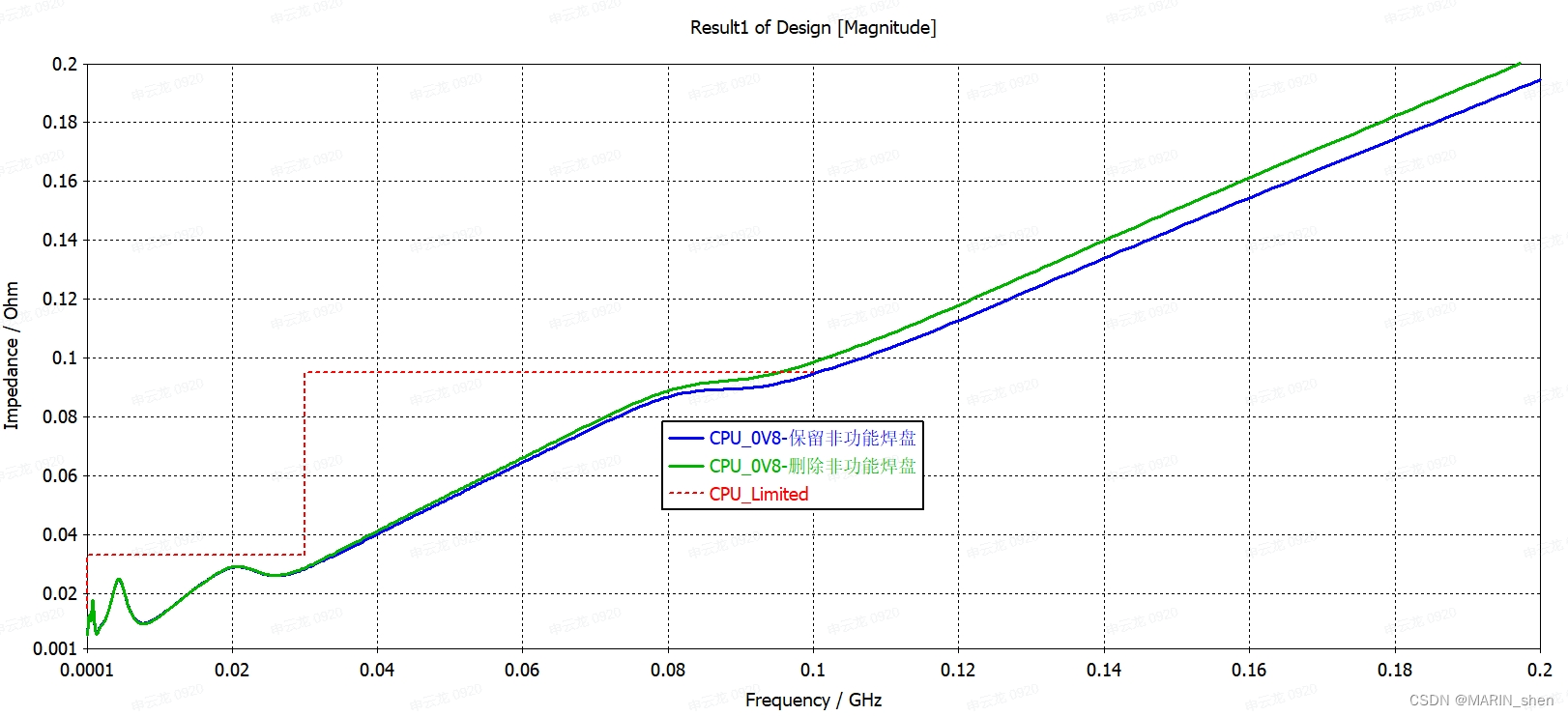

看到这个图我才明白加上手册上的电源网络的限值后,去掉非功能焊盘的就已经超过我们的目标限值曲线了,这样电源网络的PDN阻抗就有问题了,而保留非功能焊盘的则是在限值的下面,没有超过的。最终还是我太年轻了啊,看来以后还是需要多听同事的意见比较好的,自己一个难免会出现一些问题的。

这里我给大家分享一个小妙招:如何在allegro中保留我们需要的网络VIA的焊盘,其他的都去掉:

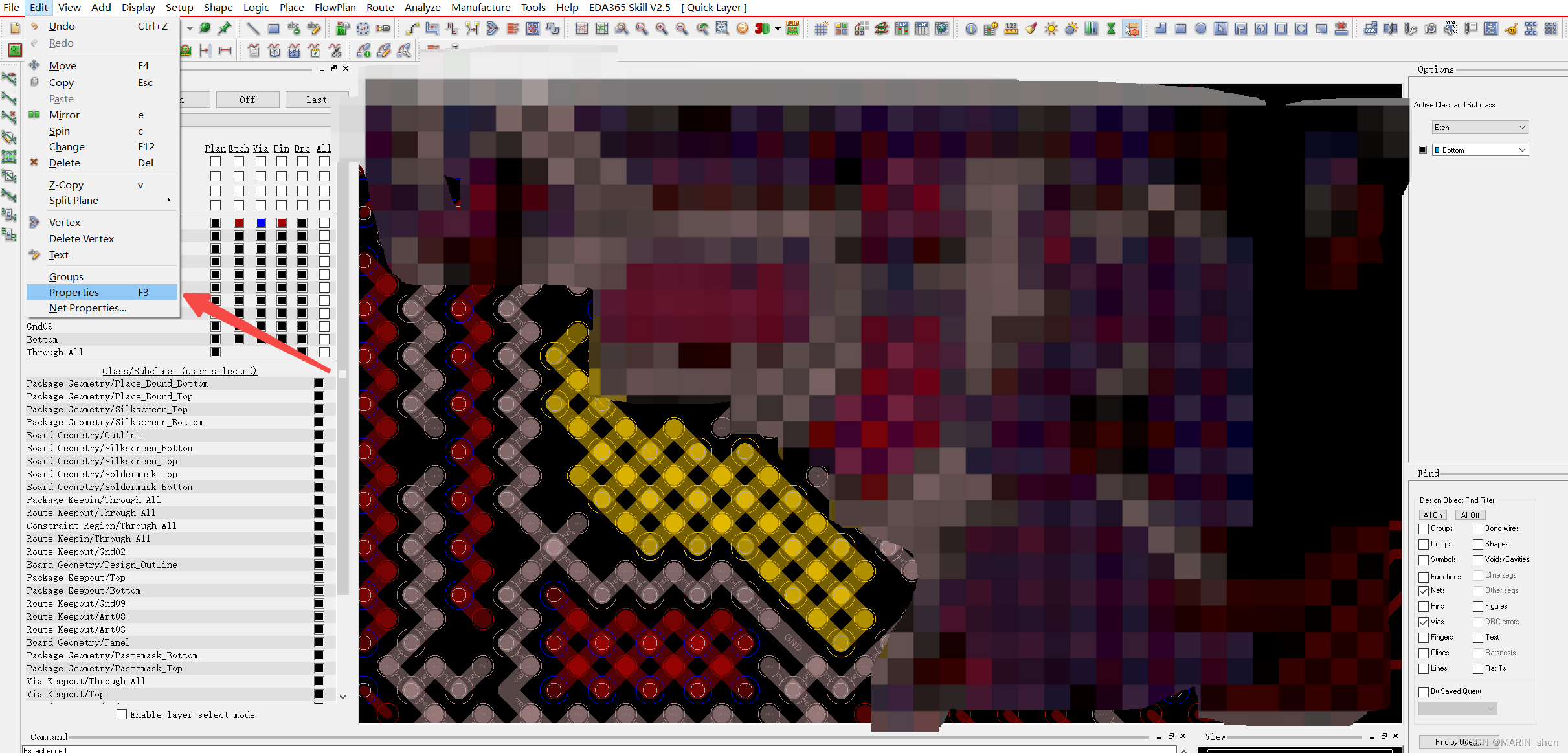

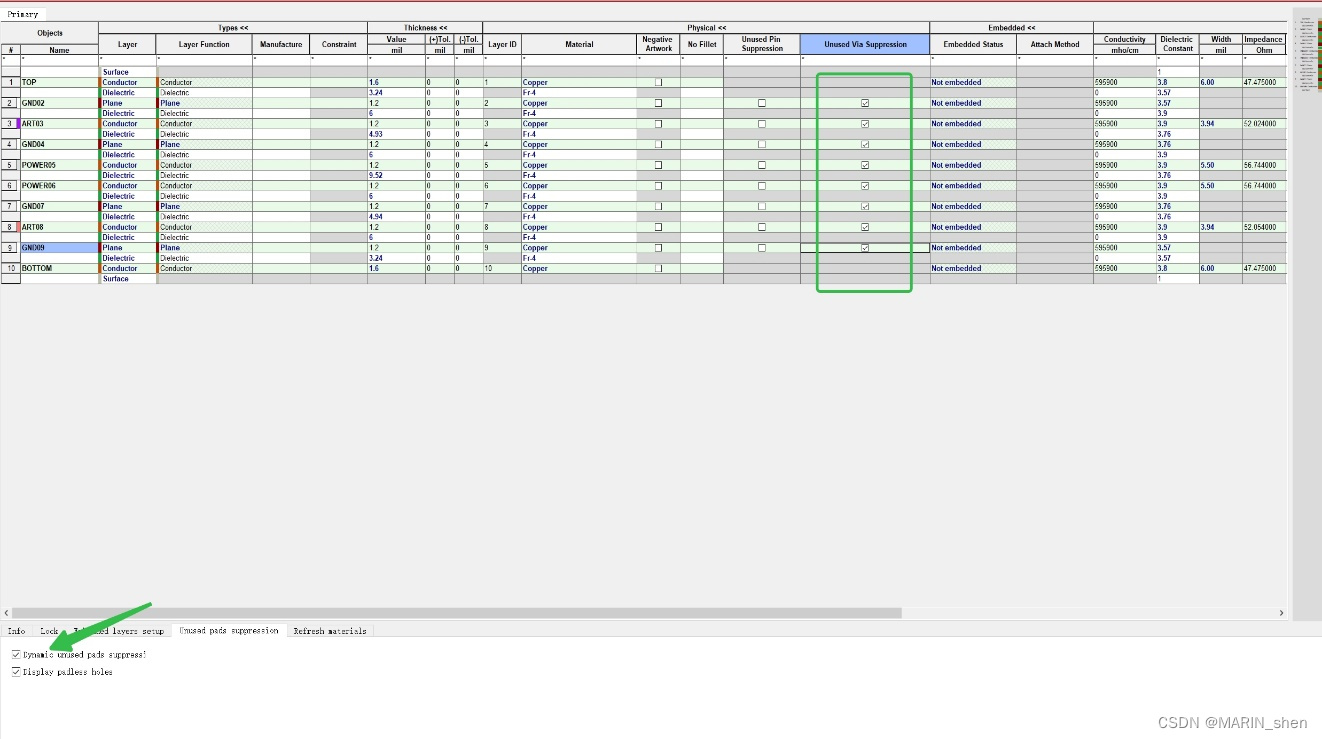

首先把你需要保留的网络设置一下属性:

EDIT----proteries,在右边的FIND栏选中NET即可。

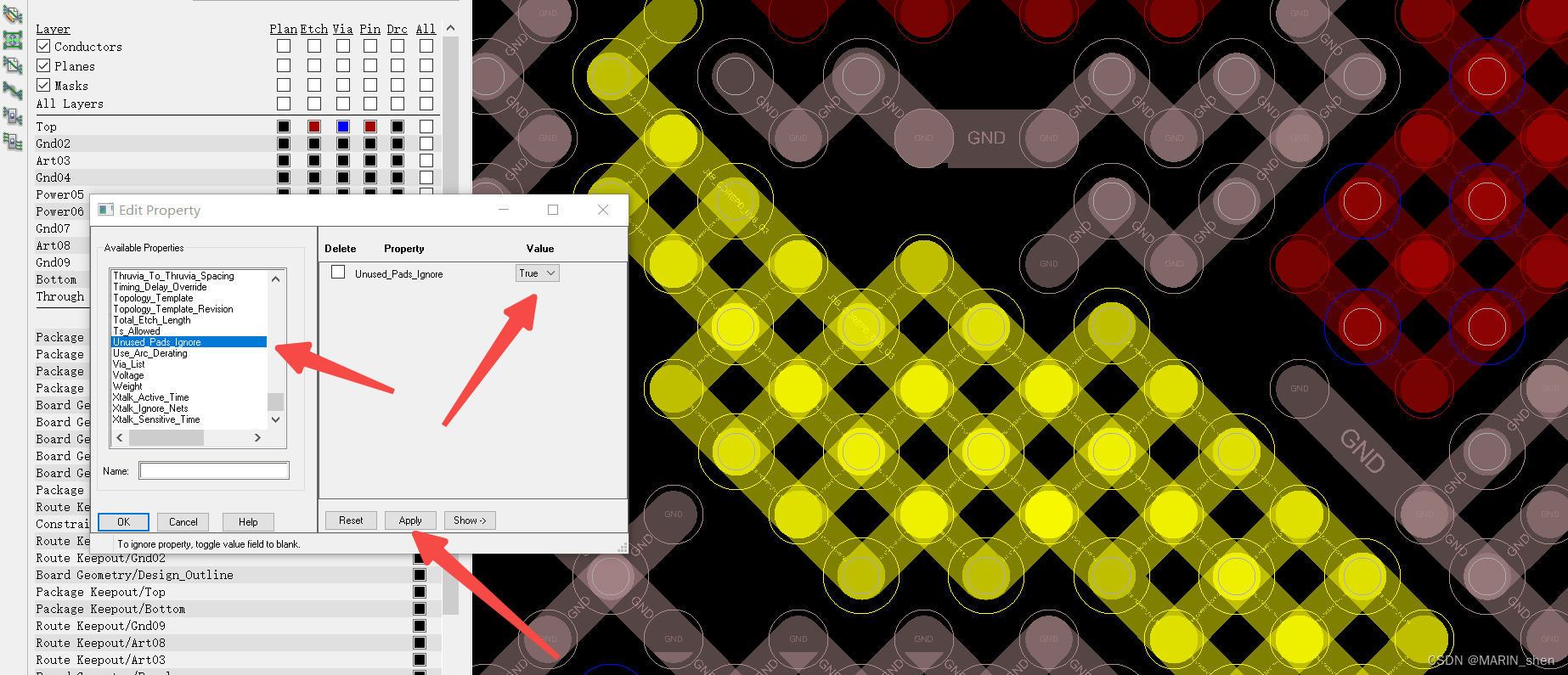

在弹出的编辑对话框中选中unused pads ignore,在value值中选中TRUE即可,然后点击apply应用,这个电源网络就被加上了忽略去掉去掉非功能焊盘,简单点说就是这个网络的VIA的所有层的焊盘还是保留的。这样对它自身的电源PDN影响就不会那么多了。

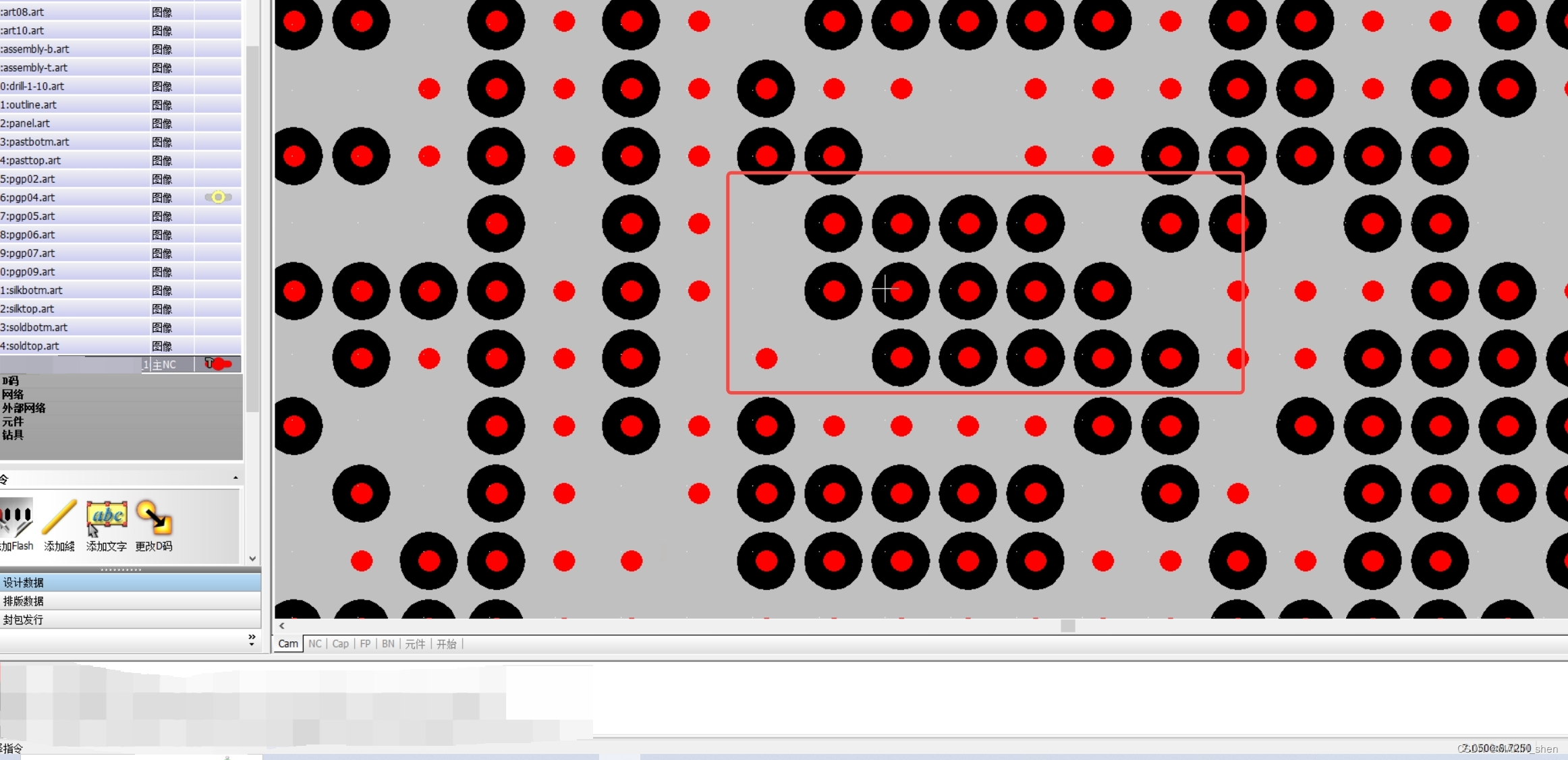

这个设置完成后,还是需要在层叠栏中设置一下去掉非功能焊盘这个选项的,小编我也做了几个对比实验验证了。首先是设置好这个网络属性后,直接在出图的时候把光绘层ARTWORK里面直接设置了掉非功能焊盘这个操作我之前的文章中有详细的描述我这里就不再赘述了然后把gerber文件导入到cam 350中发现这个电源网络的过孔在其他层的焊盘还是没有被保留。

然后小编就把层叠中的那个去掉非功能焊盘这个选项勾选上了,如下图所示:

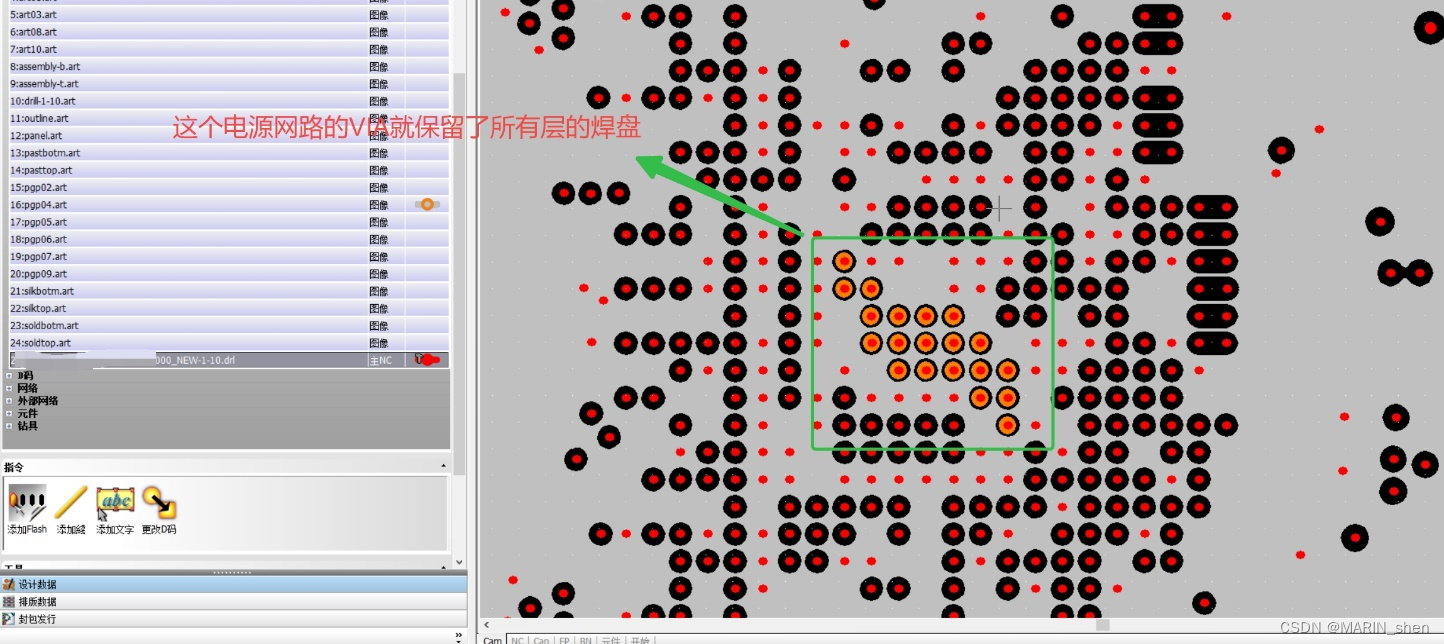

设置完成后在allegro中就会如下图所示:

就是这个网络的VIA的所有层的焊盘还是保留的。然后把gerber文件导入到cam 350中发现和allegro中显示是一样的。

然后小编我也去试了生成ODB++文件是否和这个一样,生成ODB++文件的具体操作小编也不再去一一赘述了。结果如下图所示:

生成的ODB++文件和Gerber文件是一样的。还有就是有的朋友应该会说这个电源网络的via去掉了去掉非功能焊盘为啥对PDN结果有影响啊?其实VIA的非功能焊盘其实主要影响的是其寄生电容的大小,看过小编上一遍文章的应该对这个具体的原因应该是很清楚了。

Marin说PCB之过孔去掉非功能焊盘的优点设计总结

去掉via的非功能焊盘,其实就是减少了via的寄生电容,那么它的阻抗就会相应的被拉高了,上图仿真的图例就能说明这个问题了,若是你的电源网络PDN的裕量很多,这个VIA的非功能焊盘设置的影响或许没有那么明显,但是若是你的电源网络的PDN本身就是裕量很小的,几乎是压着目标阻抗曲线的,这样的话你再去把VIA的非功能焊盘去掉的话就对你的电源网络的PDN有影响了。其实这个就是优化电源完整行性能的设计了,有的人说我裕量大我就不改,小编也不能说你的就不对了,不过能够优化建议还是做一下吧。谁不喜欢完美的男人呢?对吧。以上就是小编对VIA的非功能焊盘设置的总结的一个补充吧。好了,我们下期文章不见不散。

这篇关于Marin说PCB之如何只保留特殊信号过孔焊盘的设计总结的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!