本文主要是介绍行泊一体的“进阶战”打响,单芯片方案成主流趋势,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

行泊一体已经进入了大规模量产的前夜,并且正在逐步成为我国市场上新车型的标配。

根据高工智能汽车研究院预测,2023年开始新车行泊一体前装标配搭载率将进入快速上升通道,预计到2025年将超过40%。未来三年,行泊一体市场空间将高达1000万辆。

现阶段,市场上的行泊一体方案主要分为轻量级行泊一体方案和大算力行泊一体方案,两种方案均有单芯片和多芯片的配置之分,但目前大多数供应商推出的行泊一体方案采用的都是多SoC芯片的配置。

多位业内人士表示,“真正的行泊一体方案应该共用一个SoC芯片及传感器硬件。”未来几年内,单SoC芯片方案将是轻量级行泊一体域控方案的主流趋势。

不过,尽管单SoC芯片方案是未来轻量级“行泊一体”的主流方案,但受制于芯片算力等因素影响,单SoC芯片行泊一体方案的大规模量产落地依然面临着诸多考验。

单SOC芯片方案面临的挑战与机会

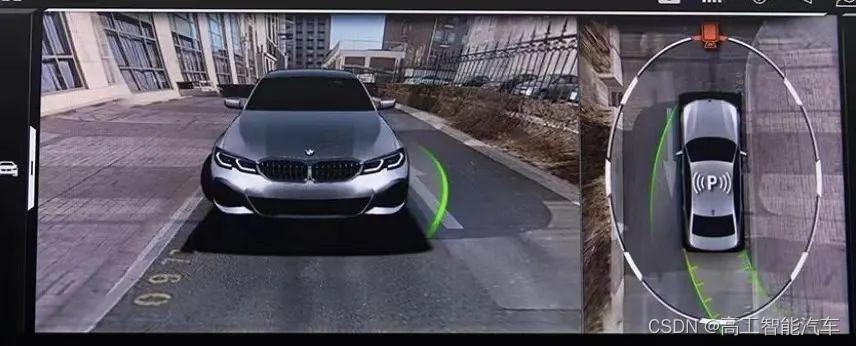

过去,实现行车ADAS和泊车功能需要两套系统,但如今只需要一套硬件设备就可以实现两套功能系统的集成,由此也带来了成本降低、重量减轻、功能迭代开发效率高等的优势。

过去一年多以来,无论是上游芯片供应商、传感器厂商还是智能驾驶系统方案商,都在大力布局行泊一体市场。其中,包括德赛西威、知行科技、东软睿驰、纵目科技等超过20家供应商已经对外发布了行泊一体方案,并且部分企业已经开始进入了前装量产阶段。

然而,受制于技术复杂度、芯片算力等因素影响,市场上已经推出的大部分行泊一体产品主要基于1.0架构来进行设计和整合,即简单地将行车子系统(行车SoC)和泊车子系统(泊车SoC)并到一个盒子里面,行车和泊车两套系统本质上仍然是相互独立的系统,不仅软件算法没有打通,硬件资源也没有实现高效复用。

一方面,此前市场上少有合适的SoC芯片可以实现泊车和行车系统的融合集成,加上域控制器的技术成熟度还不能得到充分的支持。

另一方面,单SoC芯片行泊一体方案对算力资源分配和调度的嵌入式软件也提出了更大的挑战。有业内人士表示,“软件的调度和算法模型要同时满足行车和泊车场景的需求,复杂度大幅提升,而域控制器从原型到量产的测试要求和复杂度也呈现了指数级上升。”

业内人士表示,真正融合的行泊一体方案是一个软硬件深度融合的系统,将所有传感器的信号接入到一块SoC芯片为主的域控制器上,在软件算法的作用下,实现传感器和计算资源的深度复用与共享。

“真正融合的行泊一体方案,其技术复杂度远比单纯的泊车或者行车产品要难得多。”黑芝麻智能产品总监王治中表示,这不仅要求ADAS厂商要打通感知、融合、定位、规划、决策、控制等全栈式技术环节,还需要兼顾性能、功能、可靠性、成本等多方面的考量。

总体来看,伴随着软件算法成熟度的提高、高性能芯片的出现等影响,轻量级行泊一体方案从双芯片向单芯片发展已经成为了必然趋势。

《高工智能汽车》了解到,今年下半年以来,包括智驾科技MAXIEYE在内的多家厂商都推出了基于单芯片方案的行泊一体产品。

而王治中也表示,轻量级行泊一体方案发展至今,功能需求、传感器配置、算法模型等已经比较确定,比如传感器组合基本上采用的都是5R5V的配置。

因此,单SoC芯片方案将会率先在轻量级行泊一体规模化量产落地,但大算力行泊一体方案短期内还难以采用单SoC芯片方案来实现。

根据高工智能汽车研究院的预测,20万元及以下区间将主打高性价比单芯片方案,20-30万元区间将是单芯片和多芯片方案的交叉地带。

哪种单SoC芯片可以高效适配行泊一体?

王治中强调,如何通过相对合理的算力以及更具性价比的融合感知方案,开发出真正符合用户需求的智能驾驶产品,已经成为了智能驾驶竞争的制胜关键。在这其中,SoC芯片与其承载的软件部分是实现高效适配行泊一体方案至关重要的一环。

具体来看,能够高效适配行泊一体方案的单SoC芯片需要具备以下的特征:

一是,轻量级行泊一体域控方案的SoC芯片算力需要达到12TOPS以上,高阶行泊一体方案的AI算力目前尚不固定。

根据黑芝麻智能预估,在传感器配置为5V5R的轻量级行泊一体方案当中,想要真正发挥出800万像素前向摄像头的优势至少需要用到8TOPS的AI算力,4颗200万像素环视摄像头通常需要用到4TOPS的AI算力。

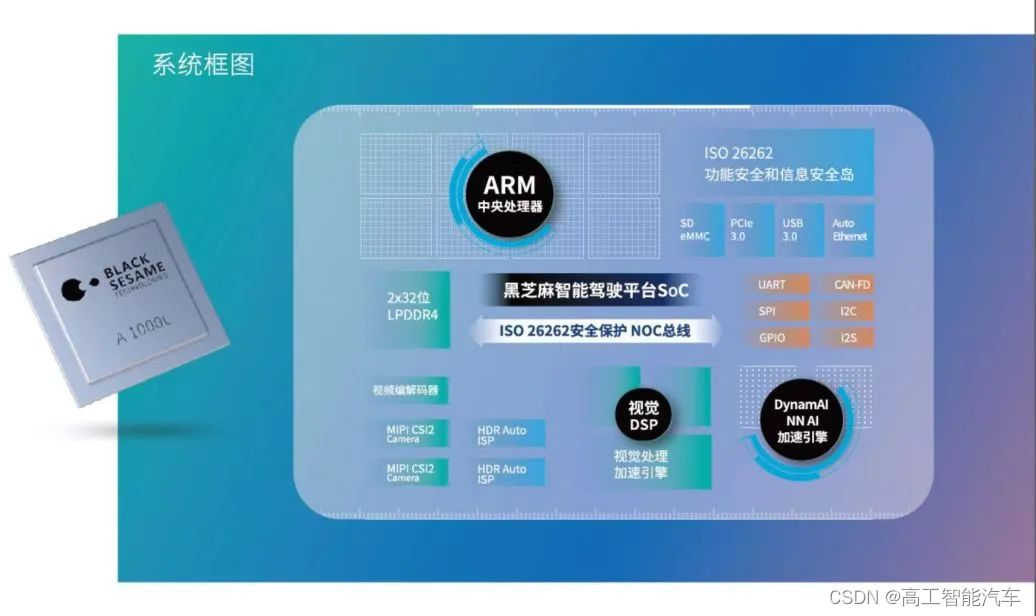

二是,SoC芯片的架构和设计需要有很清晰的定义,不仅需要同时集成ISP、GPU、MCU、CPU、DSP等处理器单元,还需要预留足够的传感器接口,支持足够多的传感器接入。

王治中表示,“行泊一体方案需要强大的CPU资源去做多任务的调度以及多传感器融合等工作,还需要ISP对于多路摄像头输出的raw图像信号进行调校,而DSP配合AI加速器则可以释放一大部分ARM的资源。”

三是,量产成本和开发周期需要具备竞争力,这其中涉及到芯片的成本以及配套的工具链、开发工具等。

比如黑芝麻智能在提供芯片的同时,也会向客户提供底层BSP、工具链、中间件、参考应用设计平台等,可以助力客户快速且高效地开发行泊一体方案。

《高工智能汽车研究院》调研显示,现阶段,行泊一体方案采用的芯片平台主要有英伟达Orin、TI的TDA4、黑芝麻智能的A1000和A1000L等。

其中,轻量级行泊一体方案大多数采用的是双TDA4、智能摄像头+TDA4等为代表的芯片组合,可以提供超高的性价比,主打的是入门及中端车型的智能驾驶需求;而以Orin为代表的大算力行泊一体,一般主打的是高端车型。

黑芝麻智能的华山二号A1000/A1000L芯片搭载了自研的两大核心IP——车规级图像处理器NeuralIQ ISP以及DynamAI NN车规级低功耗神经网络加速引擎,AI算力分别为58TOPS、16TOPS,是国内首款单芯片支持L2+/L2++级自动驾驶、同时集成360环视及低速泊车功能的产品。

王治中表示,“我们在芯片设计之初,就已经按照智能驾驶的需求定义好芯片的架构和功能模块。与其他芯片相比,A1000芯片的神经网络加速器(NPU)利用率有明显优势,最高可以达到80%,并且整体配置较为均衡。”

据了解,同样是在5R5V的传感器配置下,基于单TDA4VM或者TDA4VM Eco(AI算力在8TOPS左右)实现的行泊一体方案,必须使用分时复用的方式实现行泊的场景切换。所谓“分时复用”,就是芯片的算力相对有限,很难实现行车前向摄像头和环视摄像头等的同时调用。

与之形成明显对比的是,黑芝麻智能的单颗A1000L和A1000芯片就足以支持入门级(5V5R)和高阶(10V5R)行泊一体方案,无论是性能、成本、算力,还是开发效率,都可以高度适配行泊一体方案的需求。

王治中表示,黑芝麻智能的A1000L和A1000芯片采用的是pin2pin的平台化方案设计,软硬件架构完全兼容,可以方便客户打造平台化的行泊一体方案,也有利于后续功能的拓展与升级。

截止目前,黑芝麻智能的华山二号A1000系列芯片已经拿下了江汽集团、吉利等车企行泊一体项目的量产定点。比如江汽集团旗下思皓品牌就有多款量产车型将搭载黑芝麻智能华山二号A1000系列芯片,打造行泊一体式智能驾驶平台。

很显然,在汽车芯片短缺的大环境下,一批中国本土芯片厂商凭借高性价比、出色的产品性能、优质的本土化服务等优势,正在行泊一体、智能驾驶、智能座舱等领域加速“攻城略地”。而黑芝麻智能,正是中国芯片产业加速崛起时期的一道缩影。

这篇关于行泊一体的“进阶战”打响,单芯片方案成主流趋势的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!