本文主要是介绍基于光口的以太网 udp 回环实验,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 前言

- 一、系统框架整体设计

- 二、系统工程及 IP 创建

- 三、UDP回环模块修改说明

- 四、接口讲解

- 五、顶层模块设计

- 六、下载验证

前言

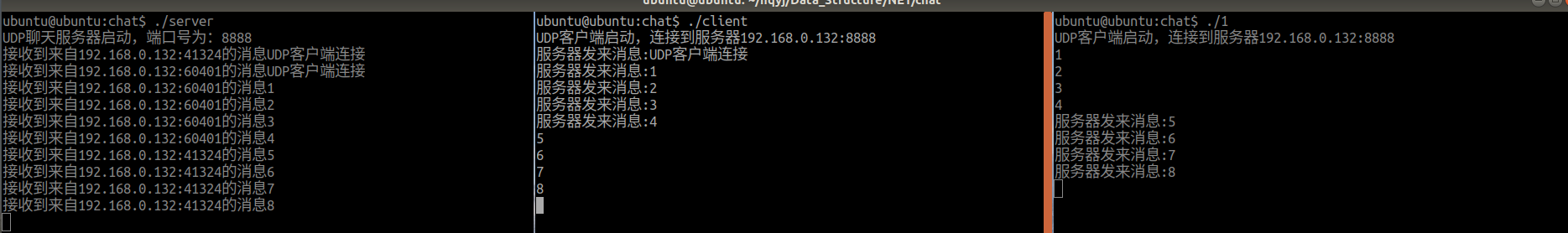

本章实验我们通过网络调试助手发送数据给 FPGA,FPGA通过光口接收数据并将数据使用 UDP 协议发送给电脑。

提示:任何文章不要过度深思!万事万物都经不起审视,因为世上没有同样的成长环境,也没有同样的认知水平,更「没有适用于所有人的解决方案」 ;不要急着评判文章列出的观点,只需代入其中,适度审视一番自己即可,能「跳脱出来从外人的角度看看现在的自己处在什么样的阶段」才不为俗人 。怎么想、怎么做,全在乎自己「不断实践中寻找适合自己的大道」

一、系统框架整体设计

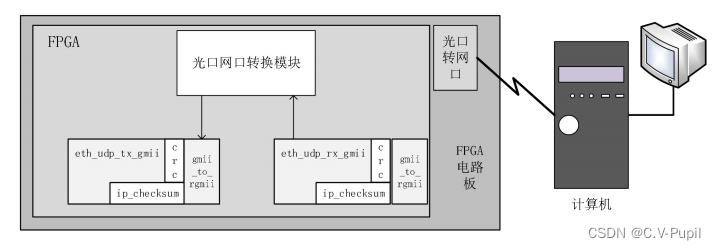

本次设计基于以太网 UDP 回环实验,在该系统上进行了一定的添加和修改,本章实验的整体框图。

本例程在 ACZ7015 开发板上使用光口网口转换模块(1G/2.5G Ethernet PCS/PMA or SGMII IP),再将转换后的数据送到 UDP 回环通信模块中。

在前面小节中我们设计的 UDP 发送模块以及 UDP 接收模块(千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP回环)),FPGA 程序接收到上位机发来的 UDP 数据包,通过解析目标 MAC_address 来确定是否是发给FPGA 的数据包。如果是的话,FPGA 会把数据包中的数据以及 IP 地址等信息,再通过发送程序将数据包发送回指定上位机。

对上图中各个模块的功能介绍如下:

(1)光口网口转换模块(gig_ethernet_pcs_pma_0):该模块的功能就是将输入的光口数据转换为网口数据,并将数据送入 UDP 回环通信模块中;

(2)UDP 回环通信模块:这个模块例化了 UDP 接收以及 UDP 发送模块,这个模块中完成了回环测试(千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP回环));

二、系统工程及 IP 创建

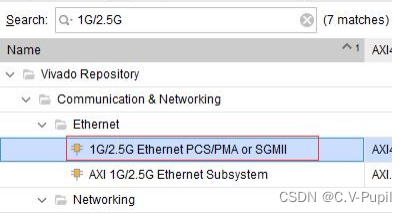

创建一个工程名为 sfp_eth_udp_loop 的工程,接下来我们来介绍一下1G/2.5G Ethernet PCS/PMA or SGMII IP,首先在 IP Catalog 里面搜索 1G/2.5G,然后选择红框中的 1G/2.5G Ethernet PCS/PMA or SGMII,再点击该 IP 进入 IP 的配置界面。

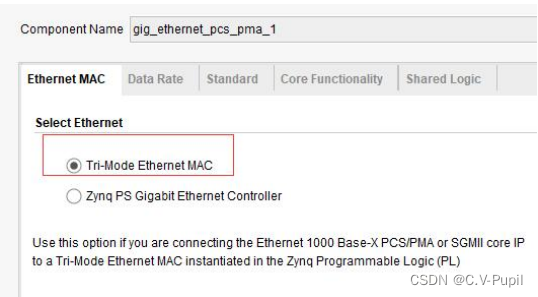

由于我们用到的是 PL 端的以太网,而且我们实验中以太网的传输速率为1Gbps,Tri-Mode Ethernet MAC 选项可以提供 1Gbps 的传输速率,所以我们在Select Ethernet 选项中选择的是 Tri-Mode Ethernet MAC 选项。点击图 中Data Rate 选项进入 Data Rate 界面配置。

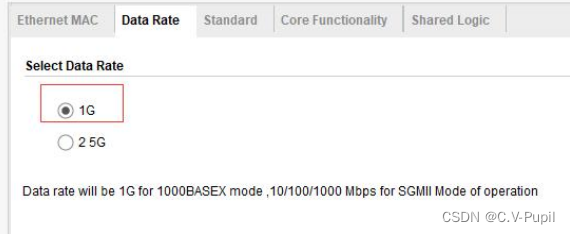

本次实验以太网的传输速率为 1Gbps,所以 Select Data Rate 选择 1G 即可。

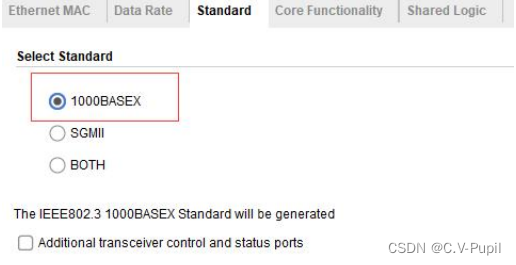

图是网口的标准选择界面:

1000BASEX:勾选该选项表示使用千兆以太网 1000BASEX 接口标准 ,简单来说就是使用千兆光口的物理层规范。在该标准下数据编码和解码都是使用 8B/10B 方式,信道上数据的传输速率为1.25Gbps,实际的数据传输速率则为 1.25G*8/10=1000Mbps,本章实验就是采用 1000BASEX 网口标准。

SGMII:勾选该选项表明使用千兆以太网的 SGMII标准,SGMII(Serilal GMII)串行 GMII。SGMII 支持 10/100/1000Mbps ,可以根据实际情况自行协商速率转换。SGMII 接口标准在使用电口(RJ45)时使用。

BOTH:勾选该选项可以在 1000BASEX 标准以及 SGMII 接口标准之间进行动态切换,哪一个稳定就优先使用哪一种接口标准。下面我们点击图中的Core Functionality 选项。

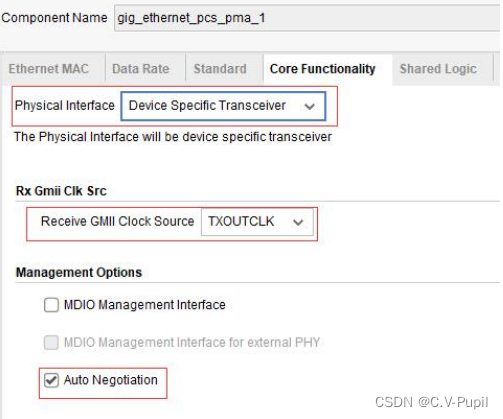

在 Core Functionality 界面中,Physical Interface 选项是选择物理接口, 物理接口选择的是 Device Specific Transceiver 表明物理接口使用设备特定的收发器(GTP 收发器);

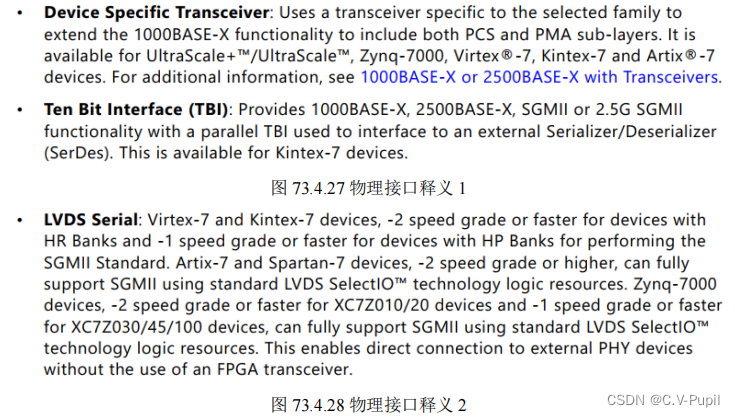

Physical Interface:这个选项是物理接口的选项,这个选项有 3 种物理接口。物理接口的选择和前面的选项以及芯片的型号有关,下面是文档中的原文:

Receive GMII Clock Source 选项是选择接收 GMII 时钟源,这里可以选择 TXOUTCLK 和

RXOUTCLK,本次实验选择默认选项 TXOUTCLK;在Management Options 选项栏下,我们本次实验勾选 Auto Negotiation 选项表明使用自协商管理功能来配置该 IP。接下来,我们点击图 4- 6 中的 Shared Logic 选项,进入 Shared Logic 配置界面。

Shared Logic 选项卡主要是选择共享逻辑是否被包含在 IP 内部。如果使用 1 个 IP 就将共享逻辑包含在IP 内部,这种方式会减少所生成的模块数量,简化设计;若使用多个 IP,那么将其中一个 IP 采用共享逻辑包含在 IP 内部的方式,其他 IP 选择将共享资源包含在 example 中。

至此,gig_ethernet_pcs_pma 的 IP 就生成成功了。

三、UDP回环模块修改说明

在千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP回环)中对udp接收模块做出修改,修改原因为:

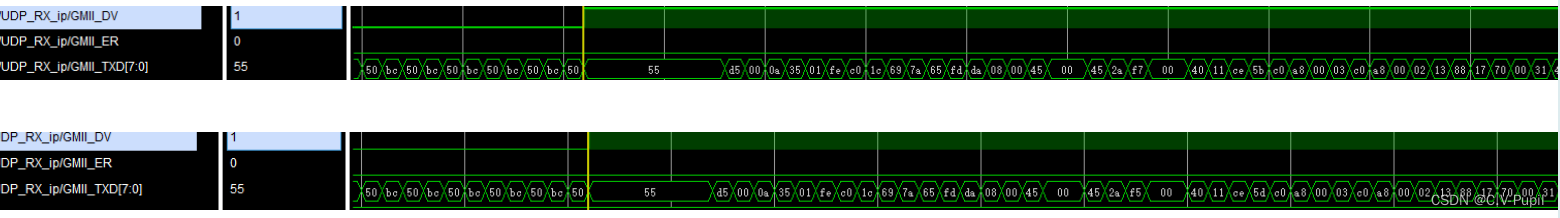

在实测上板ila抓取信号时当DV为高(有效时),TXD发送为6个55或7个55的前导码,故以往只判断7个55会导致接收失败,做出如下修改:

(1)

//判断条件always @ (posedge clk125m_o or negedge reset_n)if(!reset_n)preamble_code_check_ok <这篇关于基于光口的以太网 udp 回环实验的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!