本文主要是介绍FPGA IP核之 FIFO,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

FIFO是英文 First In First Out的缩写,即先进先出,常常作为数据缓冲器,实现数据先入先出的读写方式。我们学过ROM 和 RAM,它们都是按照地址进行数据的读写操作,而FIFO则更像一根管子,数据从一头流向另一头。也因此,FIFO 只有一个写端口和一个读端口,外部无需使用地址。

FIFO的作用,以及基本引脚

FIFO很类似于存储器,但是又有所不同。试想当我们采集数据的速度比读取数据的速度快时,我们要怎么样才能保证两个节奏不同的系统协调工作呢?我们肯定是要在中间设置一个缓冲器对数据流进行缓冲,这样才能避免数据流丢失或者读非所送的情况发生。

FIFO最基本的几个引脚有 :

- full 写满标志位:当full 有效时说明FIFO已经写满了

- empty 读空标志位:说明FIFO已经空了没有数据了

- rdreq 读请求信号:有效时,读出FIFO内数据

- wreq 写请求信号:有效时,写入数据到FIFO内

SCFIFO IP核配置

1、Basic Functions --> Miscellaneous --> FIFO

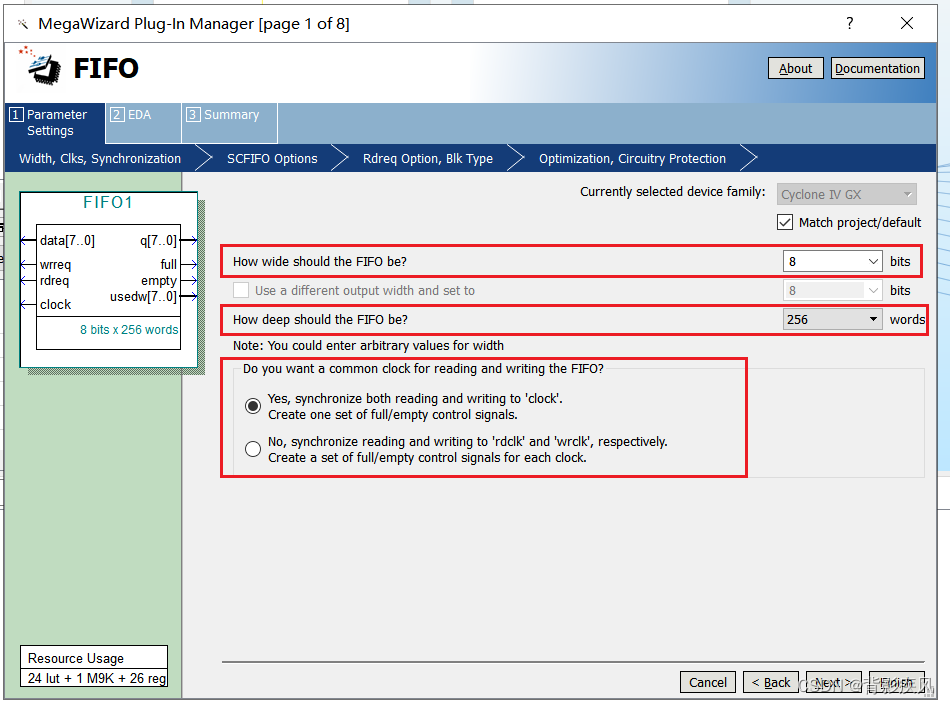

2、三个框分别是配置FIFO的位宽,深度,以及是读和写同步还是异步(SCFIFO or DCFIFO)

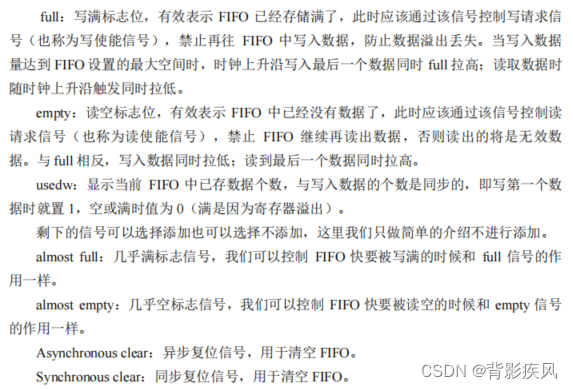

此页面主要配置FIFO的引脚,具体引脚功能描述如下:

wrreq 和 rdreq :写使能 和 读使能信号,用于指示FIFO是写还是读;注意:FIFO 的读请求信号 rdreq 当 FIFO 的满标志信号 full 有效 时拉高,当 FIFO 的空标志信号 empty 有效时拉低,以此保证FIFO不被写满也不被读空。

一般默认即可

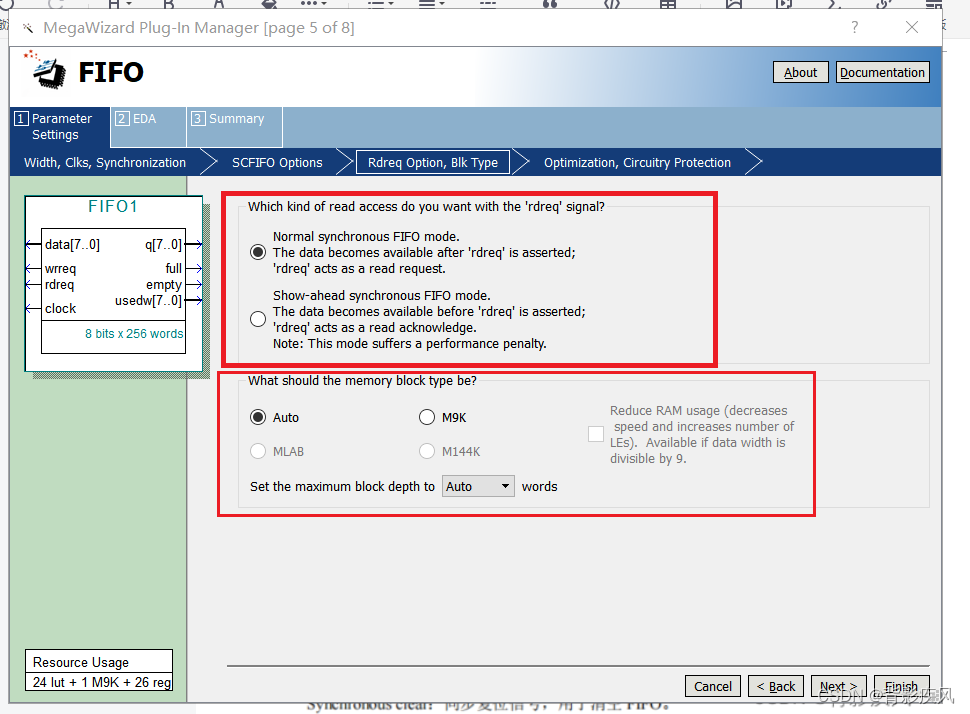

3、这个页面上面的框用于配置FIFO的属性(重点介绍),下面的框用于配置FIFO使用的资源(Auto即可)

从上面的框中可以看出,FIFO有两个模式:

普通同步模式:即当检测到读请求有效时的下一拍数据才出来,而下面的则是先出数据FIFO模式,因为读请求来临前,第一个数据就已经出来了,所以当检测到读有效时,立刻就能输出数据。

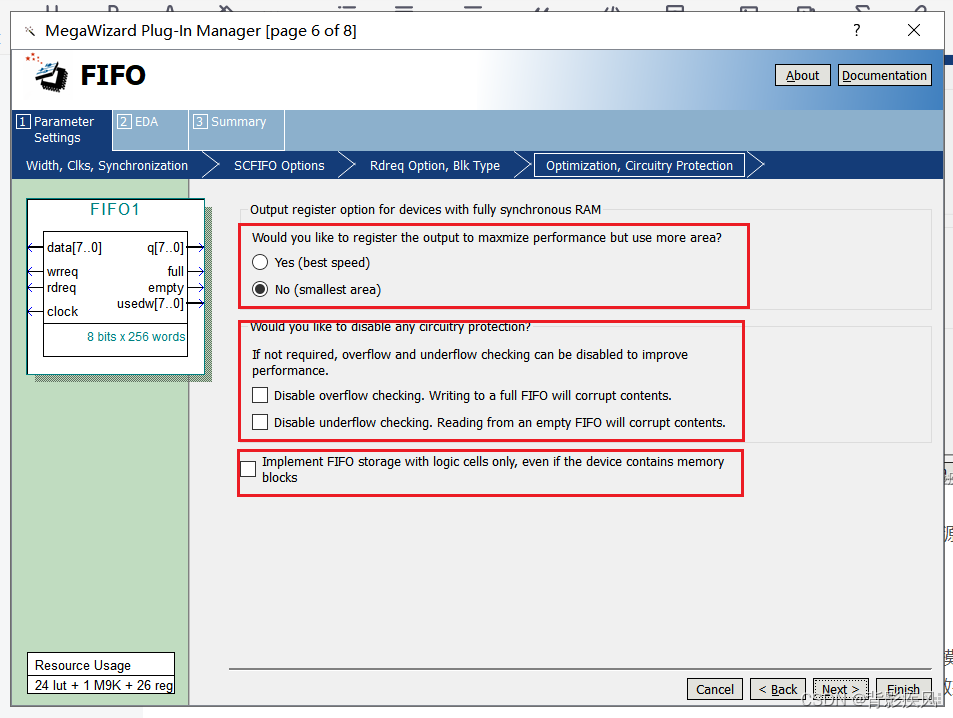

4、 FIFO性能、是否禁用保护电路、以及实现方式(存储器还是逻辑方式)

第一个框为性能设置,选择“Yes(best speed)”将获得最大的速度(性能),但是需要牺牲 更多的资源(面积);选择“No(smallest area)”将使用更少的资源(面积)但是速度(性 能)可能不是最快的。这里我们没有特殊要求,默认即可。

框 2 为选择是否禁止上溢检测和下溢检测的保护电路(上溢检测保护电路主要是用于 在 FIFO 存储满时禁止继续写数据;下溢检测保护电路主要是用于 FIFO 被读空时,禁止继 续读数据)。如果需要则保持默认,如果不需要可以选择禁用下面的两个选项来提高 FIFO 速度(性能),这里我们没有特殊需求所以保持默认即可。

框 3 为选择是否只使用逻辑单元实现 FIFO 存储器。这里使用默认设置,即用存储块实现 FIFO

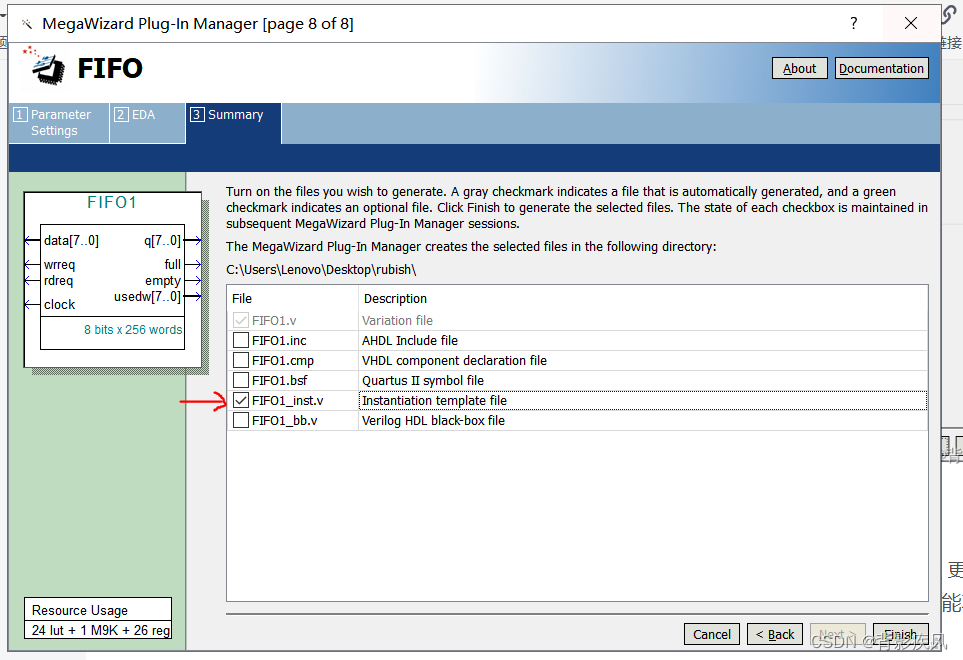

接下来的EDA和Summary步骤都没有什么特殊的配置的地方,这里我们顺便输出一个FIFO_Inst的实例,方便调用。

· 至此,我们的SCFIFO IP核配置就完成了。

DCFIFO IP核配置

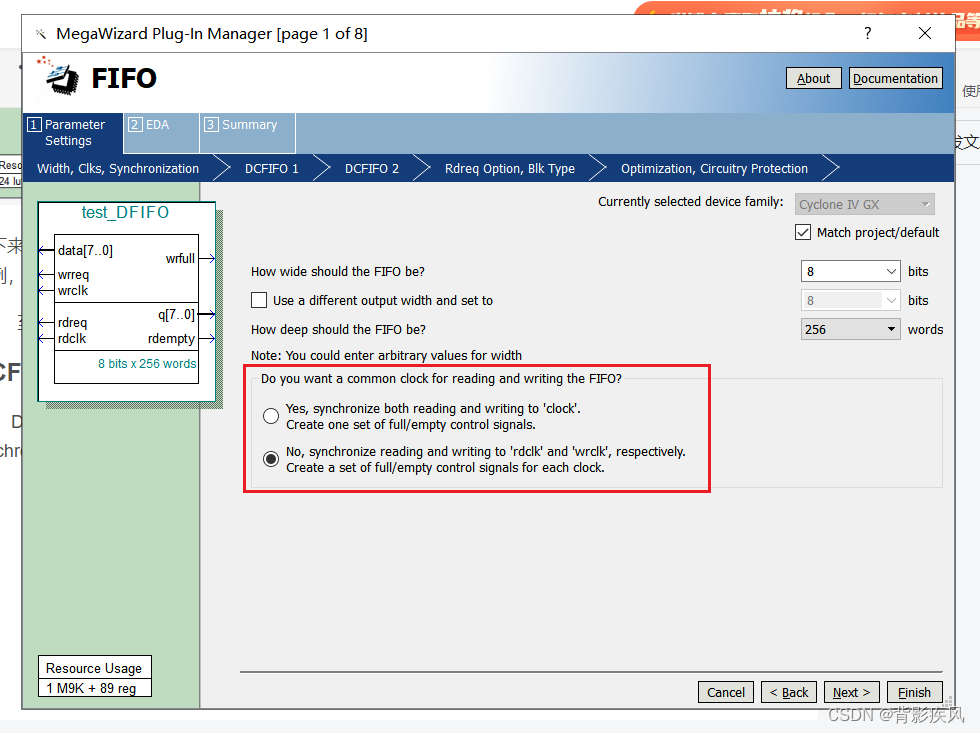

DCFIFO IP核的配置其实与SCFIFO大同小异,在第一个页面中,我们选择下方的 “sychronize reading and writing”,即异步读写,同时我们还可以看到,现在可以自由设置输出的位宽。

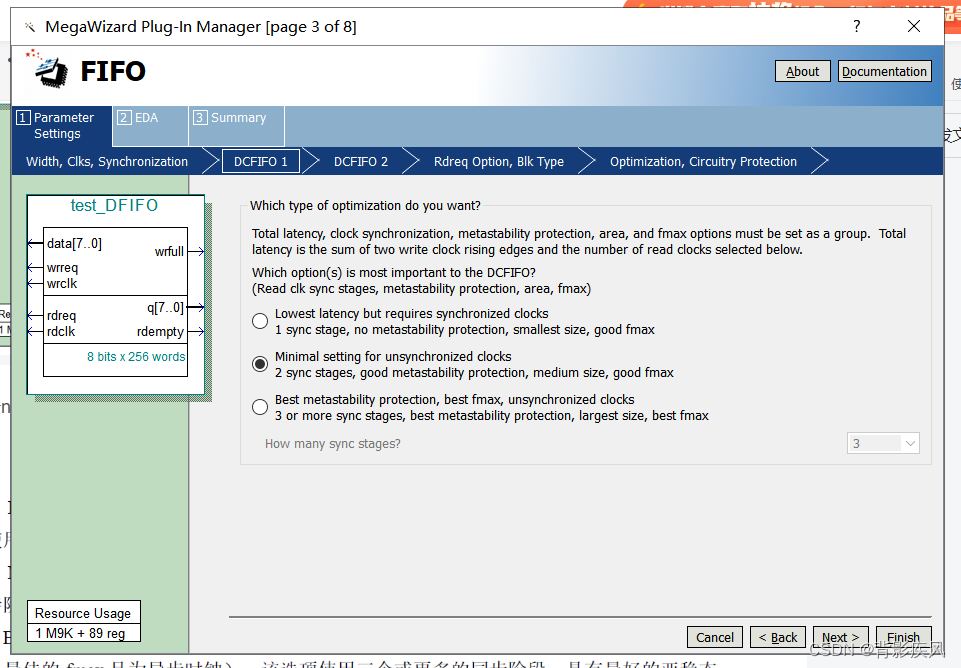

点击next后我们看到DCFIFO的优化配置界面:

三个选项的作用是:

可能有同学会不懂什么叫“亚稳态”?

大家都知道“亚健康”,就是处于健康和疾病之间的一种状态,同理,“亚稳态”就是触发器无法在某个规定时间段内达到一个可确认的状态,此时输出处于不稳定状态。

我们知道,触发器有在时钟脉冲来临时有建立时间和保持时间两个时间段,而在这两个时间段中,数据应该保持稳定,如果数据不稳,那么输出信号将处于亚稳态,之后才会回到稳态,因为亚稳态时输出的电平无法确定,因此我们需要避免亚稳态的产生。

同步时钟电路的输入信号和时钟信号是满足时序要求的,因此不会出现亚稳态;而在异步时钟电路中,输入信号和时钟是不固定的,以DCFIFO为例,可能会出现数据写入未稳定就开始读取,因此有可能会发生建立时间和保持时间中数据的不稳定,从而导致亚稳态。

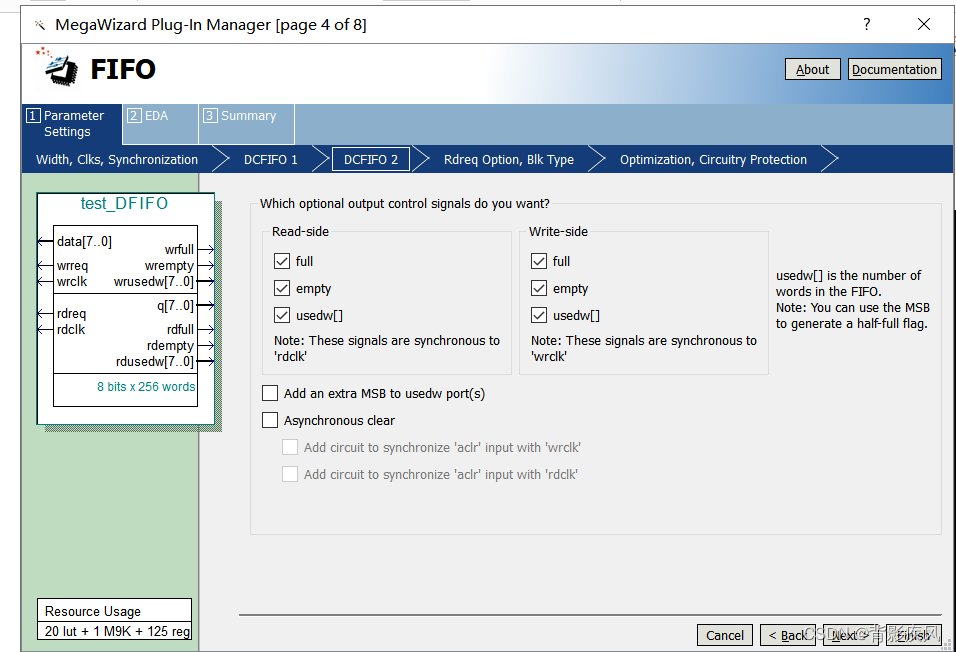

接下来就是DCFIFO的接口配置:

其中,大部分引脚可以参考前文的讲解,都是一样的。

之后的步骤内容都与SCFIFO相同,按步骤操作即可。

FIFO IP核基础知识是为了以后学习图像处理打基础,等以后遇到实际项目时,我会再写一篇实战心得。

这篇关于FPGA IP核之 FIFO的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!