核之专题

IP核之FIFO实验

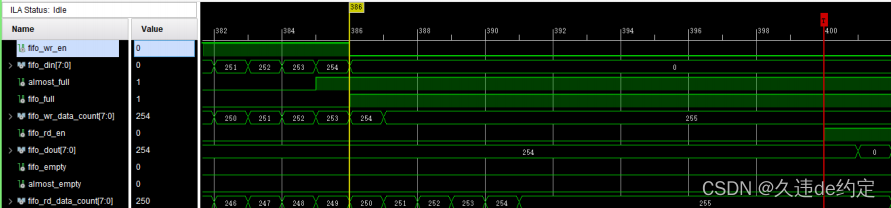

FIFO 的英文全称是 First In First Out ,即先进先出。 FPGA 使用的 FIFO 一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存, 或者高速异步数据的交互也即所谓的跨时钟域信号传递。它与 FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带

FPGA IP核之 FIFO

FIFO是英文 First In First Out的缩写,即先进先出,常常作为数据缓冲器,实现数据先入先出的读写方式。我们学过ROM 和 RAM,它们都是按照地址进行数据的读写操作,而FIFO则更像一根管子,数据从一头流向另一头。也因此,FIFO 只有一个写端口和一个读端口,外部无需使用地址。 FIFO的作用,以及基本引脚 FIFO很类似

小梅哥Xilinx FPGA学习笔记22——ip核之FIFO

目录 一:章节说明 1.1 FIFO IP简介 1.2 FIFO Generato IP 核信号框图 1.3 实验任务 二:FIFO 写模块设计 2.1 简介 2.2 模块框图 2.3 模块端口与功能描述 2.4 写模块代码 三 FIFO 读模块设计 3.1 简介 3.2 模块框图 3.3 模块端口与功能描述 3.4 读模块代码 四: 顶层模块设计 4

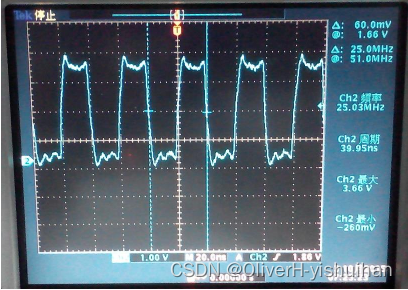

Vivado 下 IP核之 PLL实验

目录 实验任务:Vivado 下 IP核之 PLL实验 1、实验简介 2、实验环境 3、实验原理 3.1、PLL IP核简介 3.2、MMCM 和 PLL 各自的含义以及两者的区别 3.3、PLL 分频 和 倍频 的工作原理 3.4、实验任务 4、建立工程 4.1、PLL IP 核配置 4.2、模块设计 4.3、编写代码 4.4、Vivado 自带仿真器的使用