本文主要是介绍vivado XDC优先级,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

XDC优先级

关于XDC优先级

Xilinx Design Constraints(XDC)的优先级规则继承自Synopsys Design限制(SDC)。本章讨论如何解决约束冲突或重叠。

XDC约束顺序

XDC约束是按顺序解释的命令。对于等效约束,最后一个约束优先。

约束顺序示例:

在该示例中,第二时钟定义覆盖第一时钟定义,因为:

•它们都连接到同一个输入端口。

•未使用create_clock-add选项。

例外优先级

如果约束重叠(例如,如果多个定时异常应用于同一路径)从最高到最低的优先级为:

1.时钟组(set_Clock_Groups)

2.错误路径(set_False_Path)

3.最大延迟路径(set_max_Delay)和最小延迟路径(set _min_Delay)

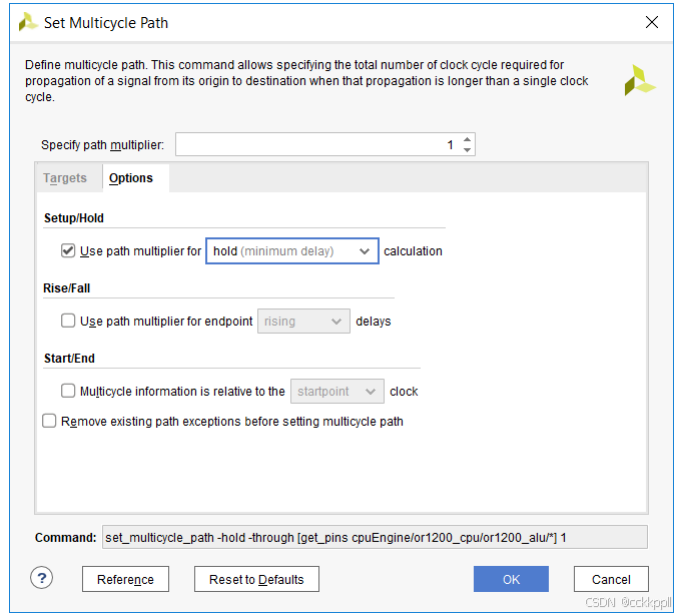

4.多循环路径(set_multycle_path)

注意:set_bus_skew约束不影响上述约束的优先级。这个set_bus_skew约束不覆盖,也不被时钟组、最大延迟、false覆盖路径和多循环路径。原因是总线偏斜不是对特定路径的约束,而是路径之间的约束。

注意:错误路径、最大/最小延迟和多周期路径之间的优先级可以更改使用选项-reset_path。时钟组约束不能被覆盖。A最大值/最小值延迟或多周期路径约束只能覆盖先前定义的错误路径或最大值/当两个约束都使用完全相同的参数定义时的最小延迟约束/-到/-through,并且最新的约束使用-reset_path。

此外,对于相同类型的异常,约束越具体,则越高优先根据过滤选项和约束中使用的对象类型,您可以修改约束的特定性。对象的优先级规则为:

1.端口、引脚和单元

使用单元的引脚而不是单元本身。

2.时钟

时钟的优先级总是低于端口、引脚和单元。使用的定时异常时钟对象总是具有比用端口定义的另一个定时例外更低的优先级,引脚和单元。

过滤器的优先级规则(从高到低)为:

在本例中,对于从clk1到clk1的路径,第一个约束覆盖第二个约束clk2.异常中使用的through选项的数量不会影响优先级。这个正时发动机使用最严格的约束。

在本例中,第一个约束仅使用单元对象,第二个约束使用时钟对象尽管inst0由clk1计时,但第一个约束会覆盖第二个约束用于从单元inst0到单元inst1的路径。

具有多个直通选项的异常优先级实例

这两个例外都由正时发动机保持。更具挑战性的约束用于计时分析在本例中,4 ns最大延迟约束将用于通过的路径引脚inst1/I3。

带有-reset_path的异常优先级示例

时钟clkA和clkB之间的路径由具有路径的最大延迟覆盖1ns的要求。“最大延迟”是用-from/-到和的相同参数定义的指定-reset_path,它将覆盖False path。

reg0/CLK和reg1/D之间的路径由False Path覆盖,因为该约束具有比最大延迟更高的优先级。最大延迟不会覆盖错误路径尽管有-reset_path,因为它不是用-from/-to的相同参数定义的。

建议:您必须避免在同一路径上使用多个定时异常,以便定时分析结果不依赖于优先级规则,而且更容易验证约束。建议您使用report_exceptions验证计时异常命令此命令提供了有关哪些定时异常被覆盖或忽略的详细信息。对于更多信息,请参阅Vivado Design Suite用户指南:设计分析和闭合技术(UG906)。

如果将字符串而不是对象传递给约束,Tcl解释器将使用以下内容序列以确定哪个对象与字符串匹配:

1.端口

2.销

3.细胞

4.净

搜索并不详尽。一旦某个类型的对象与字符串模式匹配,它们返回,即使列表中其他类型的对象也可能匹配相同的对象图案。

这篇关于vivado XDC优先级的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!