xdc专题

Xilinx FPGA 管脚的默认电平配置方法 XDC约束

目录 未使用的引脚,XDC约束其他已使用的引脚,XDC约束 未使用的引脚,XDC约束 set_property BITSTREAM.CONFIG.UNUSEDPIN PULLDOWN [current_design]set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]set_property BITST

codec engine代码阅读1~3:根目录package.xdc,release notes和example文件夹

codec engine代码阅读1~3: http://www.usr.cc/thread-52029-1-3.html http://www.usr.cc/thread-52030-1-3.html http://www.usr.cc/thread-52032-1-3.html codec engine代码阅读一---根目录下的package.xdc

vivado xdc约束基础知识0:常用命令

先简单描述常用命令,后续将详细介绍。 1. 外部时钟输入的约束如下:create_clock -period (clock period) -name (clock name) -waveform { (Traise), (Tfall) } [get_ports (clock port name)] 2. 已建立的时钟改名 create_generated_clock -name (

vivado XDC / ISE UCF 约束文件

1、CLOCK_DEDICATED_ROUTE(不打算使用板子上的晶振) vivado XDC:set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets XXX] set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {clk_wiz_0/inst/clk_i

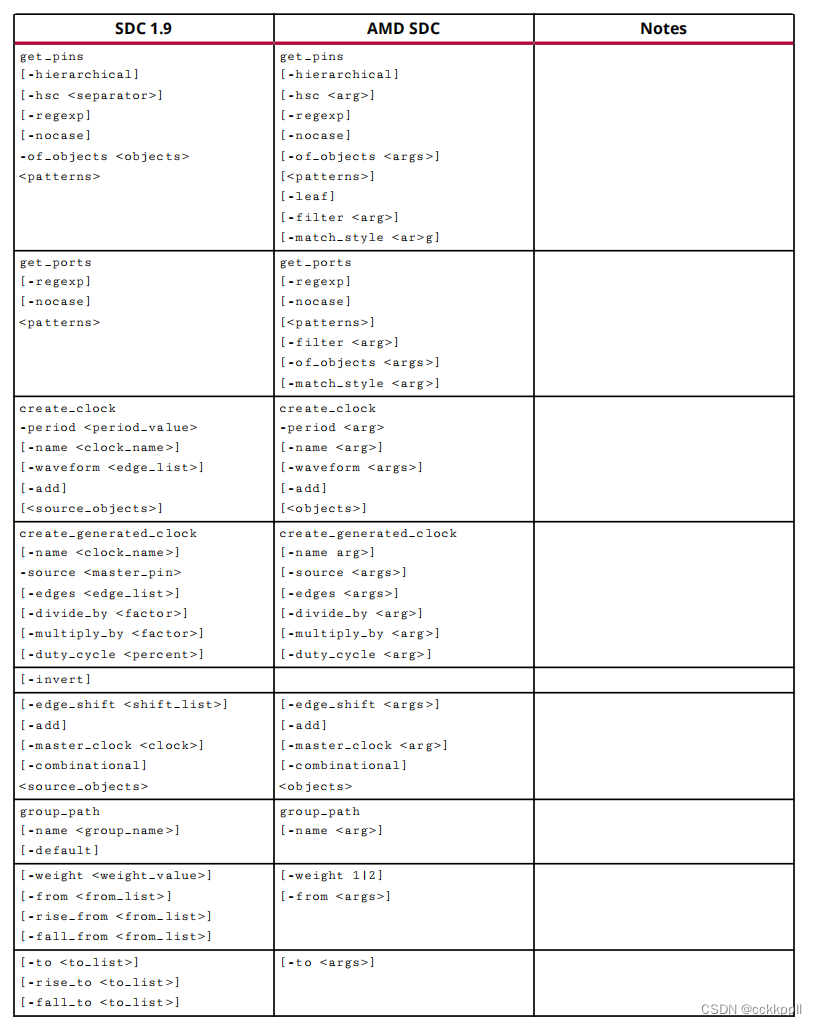

vivado 支持的XDC和SDC命令

支持的XDC和SDC命令 本附录讨论了支持的Xilinx设计约束(XDC)和Synopsys设计AMD Vivado中的约束(SDC)命令™ 集成设计环境(IDE)。 XDC文件中的有效命令 支持的SDC命令 注意:由于所有AMD Tcl命令都支持-quiet和-verbose选项,因此下表没有列出它们。

vivado XDC优先级

XDC优先级 关于XDC优先级 Xilinx Design Constraints(XDC)的优先级规则继承自Synopsys Design限制(SDC)。本章讨论如何解决约束冲突或重叠。 XDC约束顺序 XDC约束是按顺序解释的命令。对于等效约束,最后一个约束优先。 约束顺序示例: > create_clock -name clk1 -period 10 [get_ports cl

VivadoAndTcl: read_xdc

读取一个或者多个物理和时序约束。 read_xdc constraints0.xdcread_xdc {constraints0.xdc constraints1.xdc}