本文主要是介绍29 UVM Command Line Processor (CLP),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

随着设计和验证环境的复杂性增加,编译时间也增加了,这也影响了验证时间。因此,需要对其进行优化,以便在不强制重新编译的情况下考虑新的配置或参数。我们已经看到了function or task如何基于传递参数进行行为。类似地,UVM提供了一个接口来提供命令行参数,从而提供了灵活性,在“uvm_cmdline_processor”类的帮助下可以避免重新编译testbench。它允许使用不同的配置运行测试。

uvm_cmdline_processor类提供了从命令行设置各种uvm变量的功能,例如组件详细性(component verbosity)以及整数类型和字符串的配置。

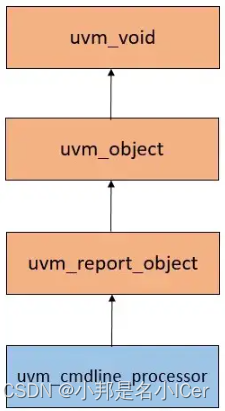

1 uvm_cmdline_processor class hierarchy

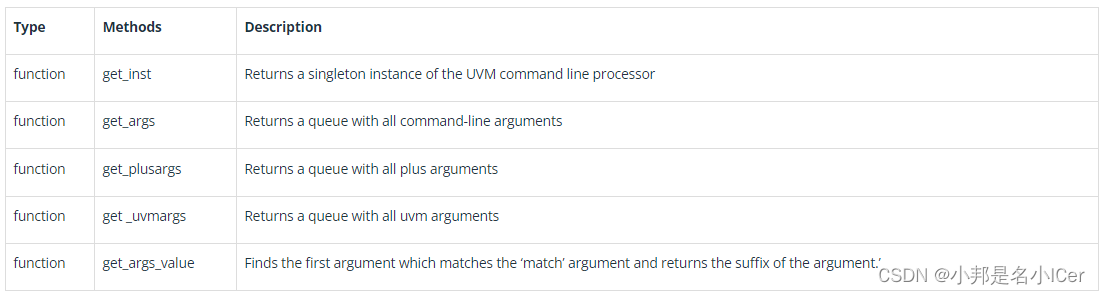

2 uvm_cmdline_processor Methods

这里讨论了命令行处理器和内置命令行参数的几种方法。

`include "uvm_macros.svh"

import uvm_pkg::*;class my_test extends uvm_test;uvm_cmdline_processor clp;bit [31:0] addr;string clp_addr_str;string clp_pattern_str;string pattern;`uvm_component_utils(my_test)function new(string name = "my_test", uvm_component parent = null);super.new(name, parent);endfunctionfunction void build_phase(uvm_phase phase);super.build_phase(phase);clp = uvm_cmdline_processor::get_inst();addr = clp.get_arg_value("+ADDR=", clp_addr_str) ? clp_addr_str.atohex(): 32'hF;pattern = clp.get_arg_value("+PATTERN=", clp_pattern_str) ? clp_pattern_str: "Hello";endfunctionfunction void end_of_elaboration_phase(uvm_phase phase);super.end_of_elaboration_phase(phase);`uvm_info(get_full_name(), $sformatf("addr = %0h, pattern = %s", addr, pattern), UVM_LOW)endfunction

endclassmodule tb_top;initial beginrun_test("my_test");end

endmodulePlease check “Run Options” while running the code.[-access +rw +ADDR=AA +PATTERN=World]

UVM: command line processor - EDA Playground

Output:

UVM_INFO testbench.sv(25) @ 0: uvm_test_top [uvm_test_top] addr = aa, pattern = World3 Built-in command line arguments in UVM

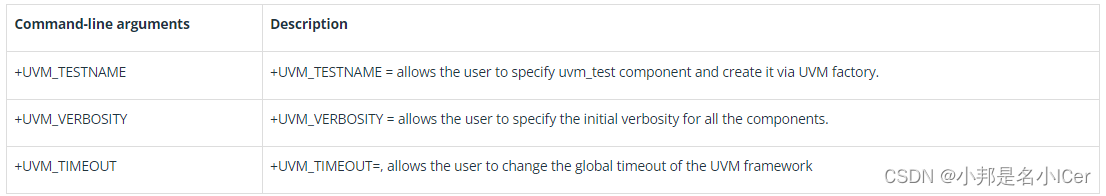

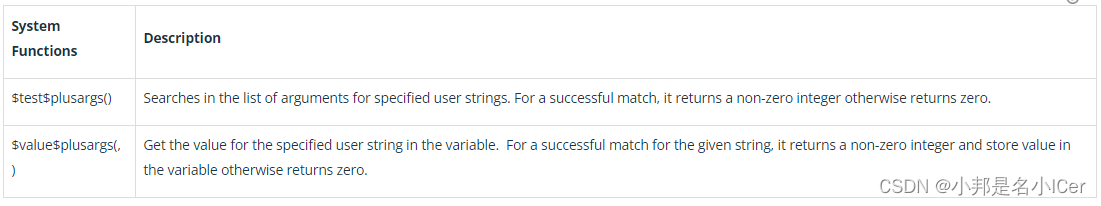

4 System functions for command line arguments in SystemVerilog

和uvm_cmdline_processor类方法类似,SV也提供了一些系统函数。

module cmd_line_args_ex;bit [31:0] addr_1, addr_2;string pattern;initial begin// +ADDR argument uses $test$plusargs and $value$plusargsif($test$plusargs("ADDR="))void'($value$plusargs("ADDR=%0h", addr_1));elseaddr_1 = 'hF;if($test$plusargs("PATTERN="))void'($value$plusargs("PATTERN=%s", pattern));elsepattern = "Hello";$display("address = %0h, pattern = %s", addr_1, pattern);if($test$plusargs("ENABLE"))$display("You have successfully received ENABLE as argument");// +ADDR argument uses $value$plusargs onlyif($value$plusargs("ADDR=%0h", addr_2))$display("You have successfully received %0h value for ADDR argument", addr_2);end

endmodulePlease check “Run Options” while running the code.【-access +rw +ADDR=AA +PATTERN=World +ENABLE】

Output:

address = aa, pattern = World

You have successfully received ENABLE as argument

You have successfully received aa value for ADDR argument这篇关于29 UVM Command Line Processor (CLP)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!