本文主要是介绍20231215给AIO-3399J适配Rockchip的原始Andoroid10的挖掘机开发板01,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

20231215给AIO-3399J适配Rockchip的原始Andoroid10的挖掘机开发板01

2023/12/15 10:49

【请严重注意:】如果刷不适配的SDK,可能会引起您的开发板【硬件发生物理】损坏!

如果您按照本步骤刷机引起的一切后果,请自行承担责任!

本人【明示】不承担任何责任。

开发板:Firefly的AIO-3399J

SDK:

AF6554D06A7C09C677BD3DB44A85A4AA Rockchip_Android10.0_SDK_Release.tar.gz00

6670B93020F599C2E67E7954368B0A5D Rockchip_Android10.0_SDK_Release.tar.gz01

8EA0D6462402C53554B1E225B3E387A3 Rockchip_Android10.0_SDK_Release.tar.gz02

3C67DC7007F9E70A85F69370D7931D5E Rockchip_Android10.0_SDK_Release.tar.gz03

C901FB21C1A4417FAB187BB4ACCB569D Rockchip_Android10.0_SDK_Release.tar.gz04

BE04E2A442636E6983B188C681A52F9F Rockchip_Android10.0_SDK_Release.tar.gz05

D972C7CB0BF6C527EA592F34FD3396A3 Rockchip_Android10.0_SDK_Release.tar.gz06

A6279BE1EBD29C67C83288C4C1E5302E Rockchip_Android10.0_SDK_Release.tar.gz07

D23FDBA115E14EC2F9E5D7D0821FE000 Rockchip_Android10.0_SDK_Release.tar.gz08

B883B9689636F3ED97EE1CCC5DFB634A Rockchip_Android10.0_SDK_Release.tar.gz09

cat Rockchip_Android10.0_SDK_Release.tar.gz0* > Rockchip_Android10.0_SDK_Release.tar.gz

tar zxvf Rockchip_Android10.0_SDK_Release.tar.gz

.repo/repo/repo sync -l

rootroot@rootroot-X99-Turbo:~/3TB/Rockchip_Android10.0_SDK_Release$

rootroot@rootroot-X99-Turbo:~/3TB/Rockchip_Android10.0_SDK_Release$ source build/envsetup.sh

rootroot@rootroot-X99-Turbo:~/3TB/Rockchip_Android10.0_SDK_Release$

rootroot@rootroot-X99-Turbo:~/3TB/Rockchip_Android10.0_SDK_Release$ lunch

22. rk3399_Android10-userdebug

Which would you like? [aosp_arm-eng] 22

rootroot@rootroot-X99-Turbo:~/3TB/Rockchip_Android10.0_SDK_Release$

rootroot@rootroot-X99-Turbo:~/3TB/Rockchip_Android10.0_SDK_Release$ ./build.sh -UACKu

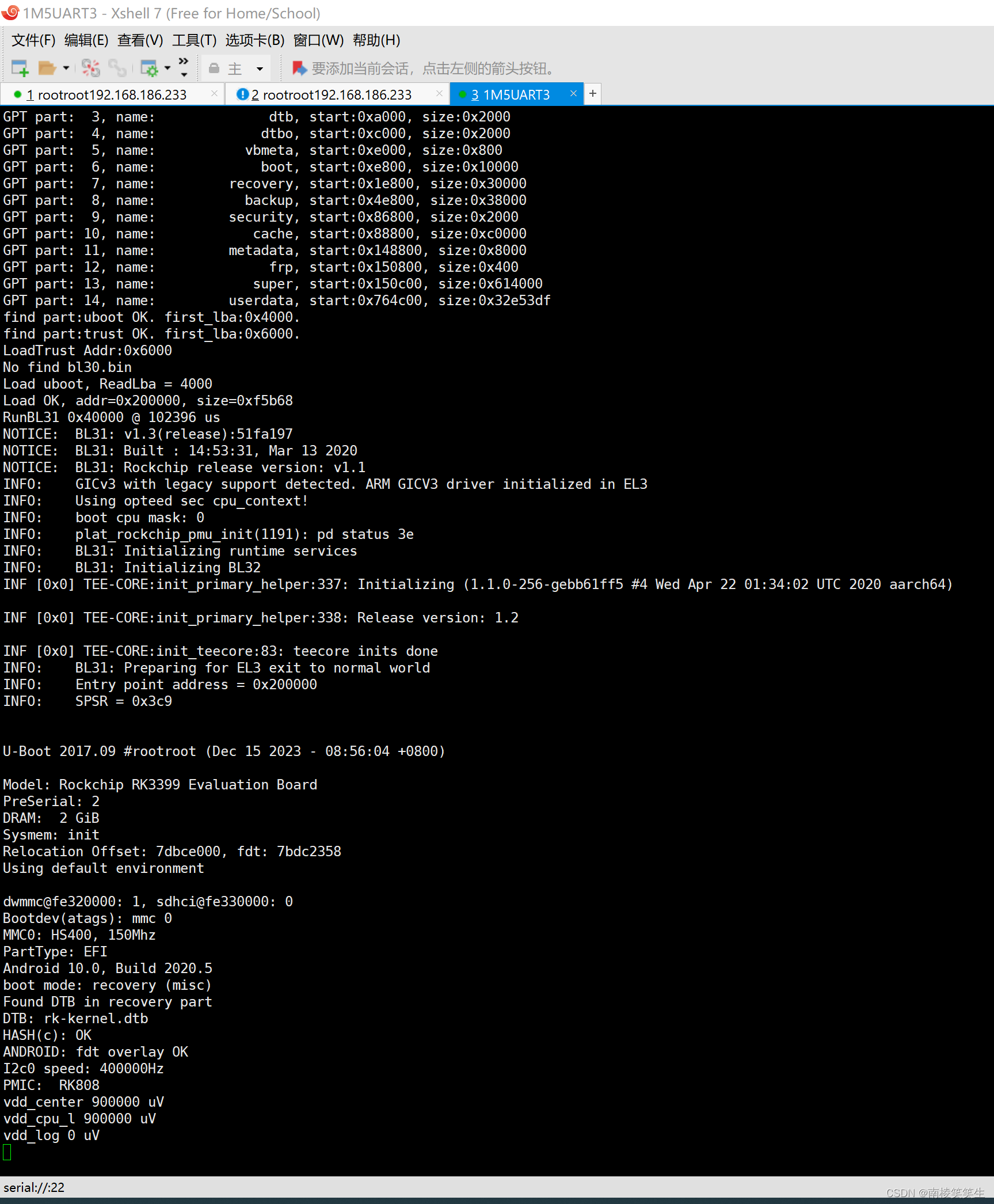

刷机之后的LOG:

[BEGIN] 2023/12/15 10:31:31

DDR Version 1.24 20191016

In

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 416MHz 0,1

Channel 0: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

Channel 1: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

256B stride

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 856MHz 1,0

ch 0 ddrconfig = 0x101, ddrsize = 0x20

ch 1 ddrconfig = 0x101, ddrsize = 0x20

pmugrf_os_reg[2] = 0x3281F281, stride = 0x9

OUT

Boot1 Release Time: Apr 23 2020 18:22:10, version: 1.25

CPUId = 0x0

SdmmcInit=2 0

BootCapSize=100000

UserCapSize=29844MB

FwPartOffset=2000 , 100000

UsbBoot ...73611

powerOn 85830

DDR Version 1.24 20191016

In

soft reset

SRX

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 416MHz 0,1

Channel 0: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

Channel 1: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

256B stride

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

channel 0, cs 0, advanced training done

channel 1, cs 0, advanced training done

change freq to 856MHz 1,0

ch 0 ddrconfig = 0x101, ddrsize = 0x20

ch 1 ddrconfig = 0x101, ddrsize = 0x20

pmugrf_os_reg[2] = 0x3281F281, stride = 0x9

ddr_set_rate to 328MHZ

ddr_set_rate to 666MHZ

ddr_set_rate to 416MHZ, ctl_index 0

ddr_set_rate to 856MHZ, ctl_index 1

support 416 856 328 666 MHz, current 856MHz

OUT

Boot1 Release Time: Apr 23 2020 18:20:09, version: 1.25

CPUId = 0x0

ChipType = 0x10, 428

SdmmcInit=2 0

BootCapSize=100000

UserCapSize=29844MB

FwPartOffset=2000 , 100000

SdmmcInit=0 ffffffff

StorageInit ok = 55312

SecureMode = 0

SecureInit read PBA: 0x4

SecureInit read PBA: 0x404

SecureInit read PBA: 0x804

SecureInit read PBA: 0xc04

SecureInit read PBA: 0x1004

SecureInit read PBA: 0x1404

SecureInit read PBA: 0x1804

SecureInit read PBA: 0x1c04

SecureInit ret = 0, SecureMode = 0

atags_set_bootdev: ret:(0)

GPT part: 0, name: uboot, start:0x4000, size:0x2000

GPT part: 1, name: trust, start:0x6000, size:0x2000

GPT part: 2, name: misc, start:0x8000, size:0x2000

GPT part: 3, name: dtb, start:0xa000, size:0x2000

GPT part: 4, name: dtbo, start:0xc000, size:0x2000

GPT part: 5, name: vbmeta, start:0xe000, size:0x800

GPT part: 6, name: boot, start:0xe800, size:0x10000

GPT part: 7, name: recovery, start:0x1e800, size:0x30000

GPT part: 8, name: backup, start:0x4e800, size:0x38000

GPT part: 9, name: security, start:0x86800, size:0x2000

GPT part: 10, name: cache, start:0x88800, size:0xc0000

GPT part: 11, name: metadata, start:0x148800, size:0x8000

GPT part: 12, name: frp, start:0x150800, size:0x400

GPT part: 13, name: super, start:0x150c00, size:0x614000

GPT part: 14, name: userdata, start:0x764c00, size:0x32e53df

find part:uboot OK. first_lba:0x4000.

find part:trust OK. first_lba:0x6000.

LoadTrust Addr:0x6000

No find bl30.bin

Load uboot, ReadLba = 4000

Load OK, addr=0x200000, size=0xf5b68

RunBL31 0x40000 @ 102396 us

NOTICE: BL31: v1.3(release):51fa197

NOTICE: BL31: Built : 14:53:31, Mar 13 2020

NOTICE: BL31: Rockchip release version: v1.1

INFO: GICv3 with legacy support detected. ARM GICV3 driver initialized in EL3

INFO: Using opteed sec cpu_context!

INFO: boot cpu mask: 0

INFO: plat_rockchip_pmu_init(1191): pd status 3e

INFO: BL31: Initializing runtime services

INFO: BL31: Initializing BL32

INF [0x0] TEE-CORE:init_primary_helper:337: Initializing (1.1.0-256-gebb61ff5 #4 Wed Apr 22 01:34:02 UTC 2020 aarch64)

INF [0x0] TEE-CORE:init_primary_helper:338: Release version: 1.2

INF [0x0] TEE-CORE:init_teecore:83: teecore inits done

INFO: BL31: Preparing for EL3 exit to normal world

INFO: Entry point address = 0x200000

INFO: SPSR = 0x3c9

U-Boot 2017.09 #rootroot (Dec 15 2023 - 08:56:04 +0800)

Model: Rockchip RK3399 Evaluation Board

PreSerial: 2

DRAM: 2 GiB

Sysmem: init

Relocation Offset: 7dbce000, fdt: 7bdc2358

Using default environment

dwmmc@fe320000: 1, sdhci@fe330000: 0

Bootdev(atags): mmc 0

MMC0: HS400, 150Mhz

PartType: EFI

Android 10.0, Build 2020.5

boot mode: recovery (misc)

Found DTB in recovery part

DTB: rk-kernel.dtb

HASH(c): OK

ANDROID: fdt overlay OK

I2c0 speed: 400000Hz

PMIC: RK808

vdd_center 900000 uV

vdd_cpu_l 900000 uV

vdd_log 0 uV

[END] 2023/12/15 10:33:06

根据在firefly的AIO-3568J开发板的经验,直接整体替换掉u-boot部分:还是启动不了!

由于原Rockchip官方的Android10之后,AIO-3399J已经不能进recovery模式刷机了。

所以需要进入MASKROM模式!

https://wiki.t-firefly.com/AIO-3399J/04-maskrom_mode.html

3. MaskRom模式 — Firefly Wiki

如果AIO-3399J使用比较久【氧化】了,AIO-3399J进MaskRom的那两个触电就算你用镊子点也可能会接触不良!

可选焊接一根线出来接地用!

Firefly完全是可以将触电改为按键的!

刷机之后的LOG:

DDR Version 1.24 20191016

In

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 416MHz 0,1

Channel 0: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

Channel 1: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

256B stride

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 856MHz 1,0

ch 0 ddrconfig = 0x101, ddrsize = 0x20

ch 1 ddrconfig = 0x101, ddrsize = 0x20

pmugrf_os_reg[2] = 0x3281F281, stride = 0x9

OUT

Boot1 Release Time: Apr 23 2020 18:22:10, version: 1.25

CPUId = 0x0

SdmmcInit=2 0

BootCapSize=100000

UserCapSize=29844MB

FwPartOffset=2000 , 100000

UsbBoot ...98337

powerOn 110554

DDR Version 1.24 20191016

In

soft reset

SRX

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 416MHz 0,1

Channel 0: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

Channel 1: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

256B stride

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

channel 0, cs 0, advanced training done

channel 1, cs 0, advanced training done

change freq to 856MHz 1,0

ch 0 ddrconfig = 0x101, ddrsize = 0x20

ch 1 ddrconfig = 0x101, ddrsize = 0x20

pmugrf_os_reg[2] = 0x3281F281, stride = 0x9

ddr_set_rate to 328MHZ

ddr_set_rate to 666MHZ

ddr_set_rate to 416MHZ, ctl_index 0

ddr_set_rate to 856MHZ, ctl_index 1

support 416 856 328 666 MHz, current 856MHz

OUT

Boot1 Release Time: Apr 23 2020 18:20:09, version: 1.25

CPUId = 0x0

ChipType = 0x10, 427

SdmmcInit=2 0

BootCapSize=100000

UserCapSize=29844MB

FwPartOffset=2000 , 100000

SdmmcInit=0 ffffffff

StorageInit ok = 55663

SecureMode = 0

SecureInit read PBA: 0x4

SecureInit read PBA: 0x404

SecureInit read PBA: 0x804

SecureInit read PBA: 0xc04

SecureInit read PBA: 0x1004

SecureInit read PBA: 0x1404

SecureInit read PBA: 0x1804

SecureInit read PBA: 0x1c04

SecureInit ret = 0, SecureMode = 0

atags_set_bootdev: ret:(0)

GPT part: 0, name: uboot, start:0x4000, size:0x2000

GPT part: 1, name: trust, start:0x6000, size:0x2000

GPT part: 2, name: misc, start:0x8000, size:0x2000

GPT part: 3, name: dtb, start:0xa000, size:0x2000

GPT part: 4, name: dtbo, start:0xc000, size:0x2000

GPT part: 5, name: vbmeta, start:0xe000, size:0x800

GPT part: 6, name: boot, start:0xe800, size:0x10000

GPT part: 7, name: recovery, start:0x1e800, size:0x30000

GPT part: 8, name: backup, start:0x4e800, size:0x38000

GPT part: 9, name: security, start:0x86800, size:0x2000

GPT part: 10, name: cache, start:0x88800, size:0xc0000

GPT part: 11, name: metadata, start:0x148800, size:0x8000

GPT part: 12, name: frp, start:0x150800, size:0x400

GPT part: 13, name: super, start:0x150c00, size:0x614000

GPT part: 14, name: userdata, start:0x764c00, size:0x32e53df

find part:uboot OK. first_lba:0x4000.

find part:trust OK. first_lba:0x6000.

LoadTrust Addr:0x6000

LoadTrust Addr:0x6400

LoadTrust Addr:0x6800

LoadTrust Addr:0x6c00

LoadTrust Addr:0x7000

LoadTrust Addr:0x7400

LoadTrust Addr:0x7800

LoadTrust Addr:0x7c00

Addr:0x6000 No find trust.img!

LoadTrustBL error:-3

DDR Version 1.24 20191016

In

soft reset

SRX

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 416MHz 0,1

Channel 0: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

Channel 1: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

256B stride

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 856MHz 1,0

ch 0 ddrconfig = 0x101, ddrsize = 0x20

ch 1 ddrconfig = 0x101, ddrsize = 0x20

pmugrf_os_reg[2] = 0x3281F281, stride = 0x9

OUT

Boot1 Release Time: Apr 23 2020 18:22:10, version: 1.25

CPUId = 0x0

SdmmcInit=2 0

BootCapSize=100000

UserCapSize=29844MB

FwPartOffset=2000 , 100000

UsbBoot ...74504

powerOn 86769

DDR Version 1.24 20191016

In

soft reset

SRX

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

change freq to 416MHz 0,1

Channel 0: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

Channel 1: LPDDR4,416MHz

Bus Width=32 Col=10 Bank=8 Row=15 CS=1 Die Bus-Width=16 Size=1024MB

256B stride

channel 0

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 1

CS = 0

MR0=0x18

MR4=0x2

MR5=0x1

MR8=0x8

MR12=0x72

MR14=0x72

MR18=0x0

MR19=0x0

MR24=0x8

MR25=0x0

channel 0 training pass!

channel 1 training pass!

channel 0, cs 0, advanced training done

channel 1, cs 0, advanced training done

change freq to 856MHz 1,0

ch 0 ddrconfig = 0x101, ddrsize = 0x20

ch 1 ddrconfig = 0x101, ddrsize = 0x20

pmugrf_os_reg[2] = 0x3281F281, stride = 0x9

ddr_set_rate to 328MHZ

ddr_set_rate to 666MHZ

ddr_set_rate to 416MHZ, ctl_index 0

ddr_set_rate to 856MHZ, ctl_index 1

support 416 856 328 666 MHz, current 856MHz

OUT

Boot1 Release Time: Apr 23 2020 18:20:09, version: 1.25

CPUId = 0x0

ChipType = 0x10, 427

SdmmcInit=2 0

BootCapSize=100000

UserCapSize=29844MB

FwPartOffset=2000 , 100000

SdmmcInit=0 ffffffff

StorageInit ok = 55204

SecureMode = 0

SecureInit read PBA: 0x4

SecureInit read PBA: 0x404

SecureInit read PBA: 0x804

SecureInit read PBA: 0xc04

SecureInit read PBA: 0x1004

SecureInit read PBA: 0x1404

SecureInit read PBA: 0x1804

SecureInit read PBA: 0x1c04

SecureInit ret = 0, SecureMode = 0

atags_set_bootdev: ret:(0)

GPT part: 0, name: uboot, start:0x4000, size:0x2000

GPT part: 1, name: trust, start:0x6000, size:0x2000

GPT part: 2, name: misc, start:0x8000, size:0x2000

GPT part: 3, name: dtb, start:0xa000, size:0x2000

GPT part: 4, name: dtbo, start:0xc000, size:0x2000

GPT part: 5, name: vbmeta, start:0xe000, size:0x800

GPT part: 6, name: boot, start:0xe800, size:0x10000

GPT part: 7, name: recovery, start:0x1e800, size:0x30000

GPT part: 8, name: backup, start:0x4e800, size:0x38000

GPT part: 9, name: security, start:0x86800, size:0x2000

GPT part: 10, name: cache, start:0x88800, size:0xc0000

GPT part: 11, name: metadata, start:0x148800, size:0x8000

GPT part: 12, name: frp, start:0x150800, size:0x400

GPT part: 13, name: super, start:0x150c00, size:0x614000

GPT part: 14, name: userdata, start:0x764c00, size:0x32e53df

find part:uboot OK. first_lba:0x4000.

find part:trust OK. first_lba:0x6000.

LoadTrust Addr:0x6000

No find bl30.bin

Load uboot, ReadLba = 4000

Load OK, addr=0x200000, size=0x101868

RunBL31 0x40000 @ 102987 us

NOTICE: BL31: v1.3(release):51fa197

NOTICE: BL31: Built : 14:53:31, Mar 13 2020

NOTICE: BL31: Rockchip release version: v1.1

INFO: GICv3 with legacy support detected. ARM GICV3 driver initialized in EL3

INFO: Using opteed sec cpu_context!

INFO: boot cpu mask: 0

INFO: plat_rockchip_pmu_init(1191): pd status 3e

INFO: BL31: Initializing runtime services

INFO: BL31: Initializing BL32

INF [0x0] TEE-CORE:init_primary_helper:337: Initializing (1.1.0-256-gebb61ff5 #4 Wed Apr 22 01:34:02 UTC 2020 aarch64)

INF [0x0] TEE-CORE:init_primary_helper:338: Release version: 1.2

INF [0x0] TEE-CORE:init_teecore:83: teecore inits done

INFO: BL31: Preparing for EL3 exit to normal world

INFO: Entry point address = 0x200000

INFO: SPSR = 0x3c9

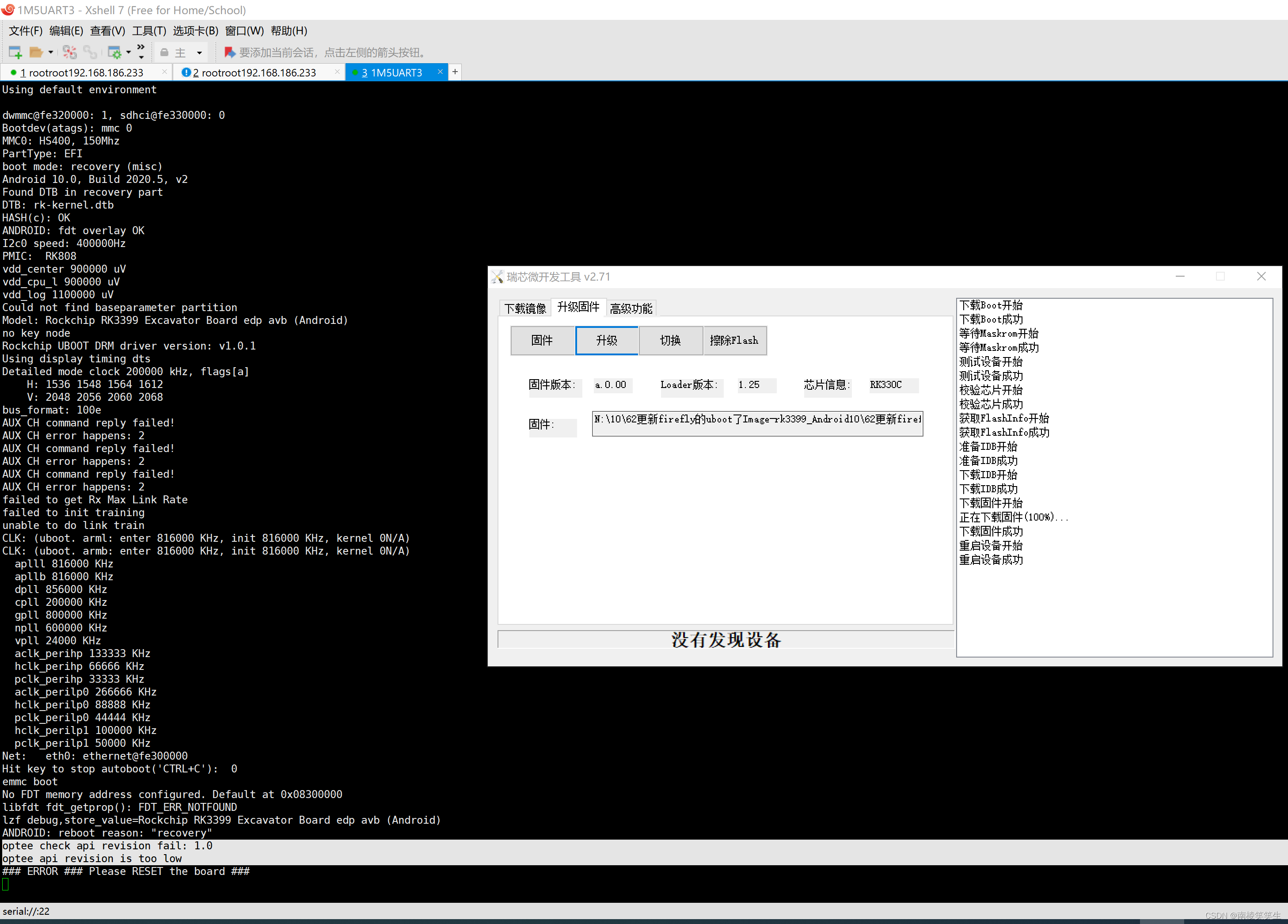

U-Boot 2017.09 (Dec 15 2023 - 10:35:06 +0800)

Model: Rockchip RK3399 Evaluation Board

PreSerial: 2, raw, 0xff1a0000

DRAM: 2 GiB

Sysmem: init

Relocation Offset: 7db7a000

Relocation fdt: 7bd6e2d0 - 7bd70ceb

CR: M/C/I

Using default environment

dwmmc@fe320000: 1, sdhci@fe330000: 0

Bootdev(atags): mmc 0

MMC0: HS400, 150Mhz

PartType: EFI

boot mode: recovery (misc)

Android 10.0, Build 2020.5, v2

Found DTB in recovery part

DTB: rk-kernel.dtb

HASH(c): OK

ANDROID: fdt overlay OK

I2c0 speed: 400000Hz

PMIC: RK808

vdd_center 900000 uV

vdd_cpu_l 900000 uV

vdd_log 1100000 uV

Could not find baseparameter partition

Model: Rockchip RK3399 Excavator Board edp avb (Android)

no key node

Rockchip UBOOT DRM driver version: v1.0.1

Using display timing dts

Detailed mode clock 200000 kHz, flags[a]

H: 1536 1548 1564 1612

V: 2048 2056 2060 2068

bus_format: 100e

AUX CH command reply failed!

AUX CH error happens: 2

AUX CH command reply failed!

AUX CH error happens: 2

AUX CH command reply failed!

AUX CH error happens: 2

failed to get Rx Max Link Rate

failed to init training

unable to do link train

CLK: (uboot. arml: enter 816000 KHz, init 816000 KHz, kernel 0N/A)

CLK: (uboot. armb: enter 816000 KHz, init 816000 KHz, kernel 0N/A)

aplll 816000 KHz

apllb 816000 KHz

dpll 856000 KHz

cpll 200000 KHz

gpll 800000 KHz

npll 600000 KHz

vpll 24000 KHz

aclk_perihp 133333 KHz

hclk_perihp 66666 KHz

pclk_perihp 33333 KHz

aclk_perilp0 266666 KHz

hclk_perilp0 88888 KHz

pclk_perilp0 44444 KHz

hclk_perilp1 100000 KHz

pclk_perilp1 50000 KHz

Net: eth0: ethernet@fe300000

Hit key to stop autoboot('CTRL+C'): 0

emmc boot

No FDT memory address configured. Default at 0x08300000

libfdt fdt_getprop(): FDT_ERR_NOTFOUND

lzf debug,store_value=Rockchip RK3399 Excavator Board edp avb (Android)

ANDROID: reboot reason: "recovery"

optee check api revision fail: 1.0

optee api revision is too low

### ERROR ### Please RESET the board ###

[END] 2023/12/15 10:53:00

这篇关于20231215给AIO-3399J适配Rockchip的原始Andoroid10的挖掘机开发板01的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!