本文主要是介绍Vivado中的Elaborate是做什么的?,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

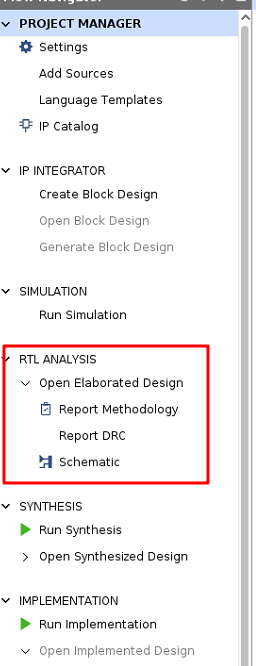

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。

elaborate可以翻译为“详尽解析”,就是将RTL源代码翻译转换成对应的电路。

有同学会问,这不是Synthesis做的工作吗?

我们可以来比较一下Elaborate和Synthesis后的Schematic就很直观了:

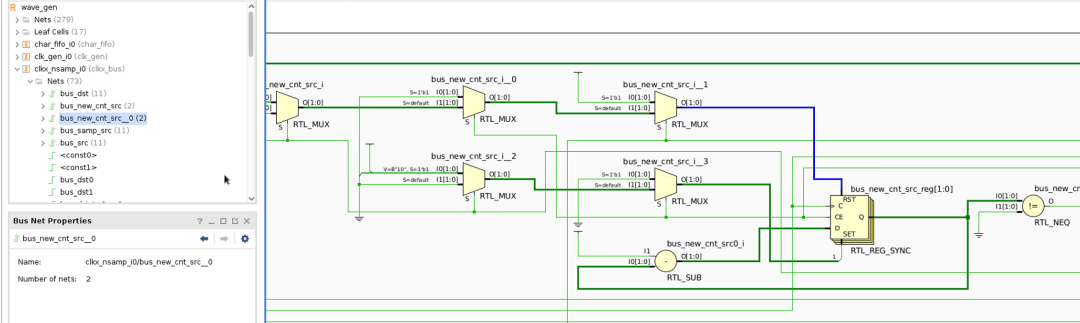

Elaborated Design:

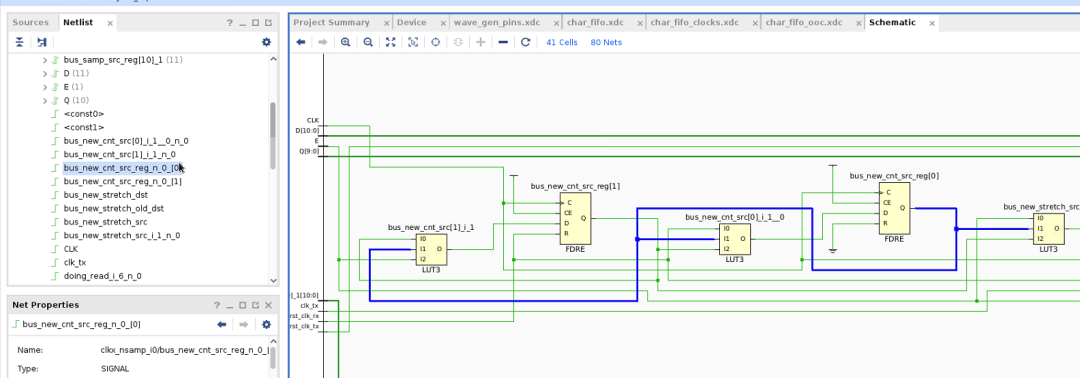

Synthesisd Design:

可以看出,Elaborated Design里面的电路是单纯的对RTL源代码的解析,到了Synthesisd Design,则可以看到Xilinx的具体的库单元,比如LUT3、FDRE等,都是在Xilinx FPGA中真实存在的。

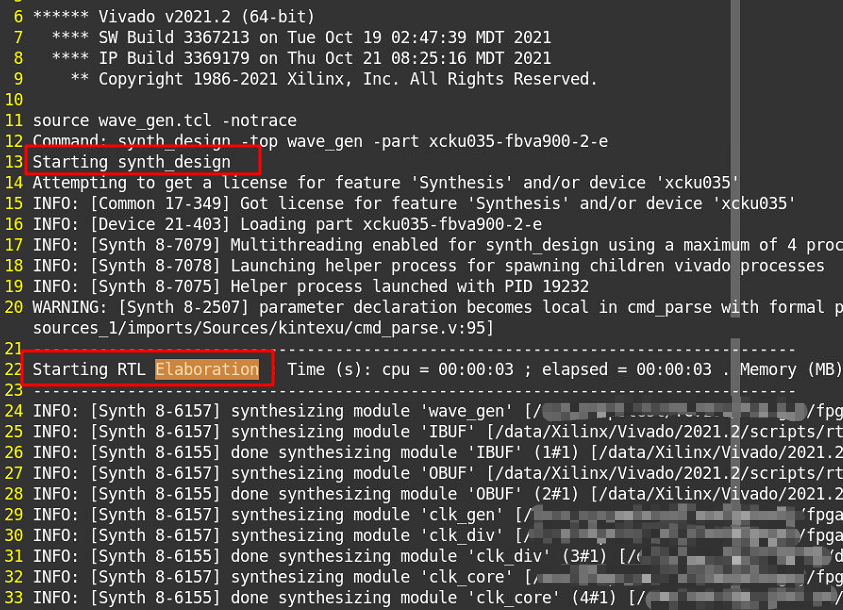

其实在综合的log文件,看到Elaborate的存在,综合的第一步就是先进行Elaborate:

FPGA时钟篇

FPGA时钟篇(一) 7系列的时钟结构

FPGA时钟篇(二) 7系列clock region详解

FPGA时钟篇(三) MRCC和SRCC的区别

FPGA博客整理

Vivado non-project模式示例

linux vivado安装时卡在最后一步解决方案

set_output_delay如何约束?

set_input_delay如何约束?

FPGA中的fast corner和slow corner是什么?

Vivado DDR4仿真

FPGA中BEL Site Tile FSR SLR分别指什么?

vivado如何快速找到schematic中的object

Xilinx FPGA中HP HR HD bank分别是什么用途

FPGA的虚拟时钟如何使用?

进入IP Core的时钟,都不需要再手动添加约束么?

false path和asynchronous的区别

Xilinx FPGA的DNA是什么?

Xilinx Ethernet MAC IP调试的小坑

管脚约束问题导致生成bit时报错 如何在不重新Implentation情况下生成bit?

FPGA跨异步时钟ASYNC_REG和XPM_CDC处理

VS Code自动例化Verilog模块

XDC约束中加入注释,为什么会导致该约束失效?

GTX/GTH/GTY/GTP/GTZ/GTM有什么区别?

Vivado IP中的Shared Logic到底是干嘛的?

Vivado的Implementation都包含哪些步骤?

导出ILA数据到Python

DDR突然初始化失败 Debug记录

D触发器都有哪几种类型?对应什么样的代码?

Xilinx DDR4/DDR3 - Hardware Debug Guide

Virtex7 Microblaze下DDR3测试

Vivado综合后要解决哪些问题?

如何设定寄存器的初始值?

使用SystemVerilog简化FPGA中的接口

FPGA 中的有符号数乘法

大家一致避免使用的锁存器为什么依然存在于FPGA中?我们对锁存器有什么误解?

FPGA中截位导致的直流分量如何去除?

FPGA复位的正确打开方式

影响FPGA时序的进位链(Carry Chain), 你用对了么??

Xilinx FPGA Partial Reconfiguration 部分重配置 详细教程

Vivado HLS教程笔记

Hold Time违例,该如何解决

Vivado中jobs和threads的区别?选择多个jobs能加快实现速度么?

Vivado调试小结:ILA debug中的数据也许并不可信

Vivado时序收敛技术(一) Baseline基础理论

Vivado时序收敛技术(二) 时序违例的根本原因及解决方法

Vivado中模块封装成edif和dcp

生成Verilog HDL例化模板

‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧ END ‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧

欢迎关注微信公众号【数字积木】,更精彩的内容等着你!

这篇关于Vivado中的Elaborate是做什么的?的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!