本文主要是介绍Vivado中添加Pynq-Z2板卡文件,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

2023.5.31

今天在Vivado中导入pynq_z2板卡文件废了好些功夫,正好在这里里分享一下,希望对遇到相同困难的人有所帮助。

在xilinx官网的pynq-z2板卡文件已经失效,所以我自己去找了一个文件

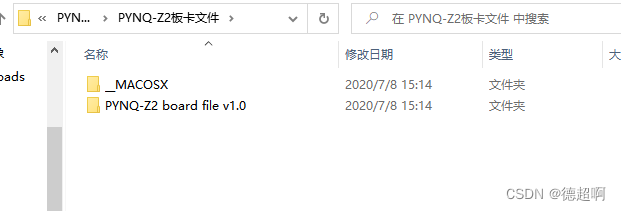

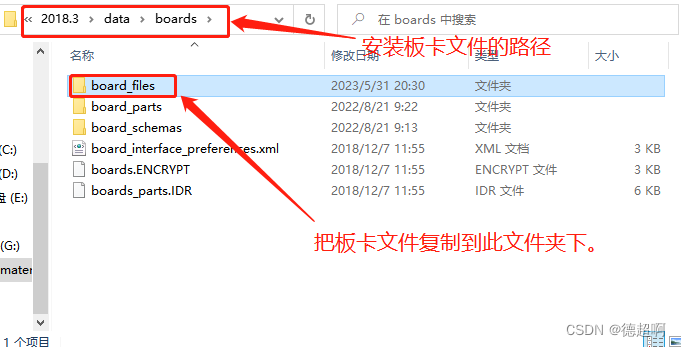

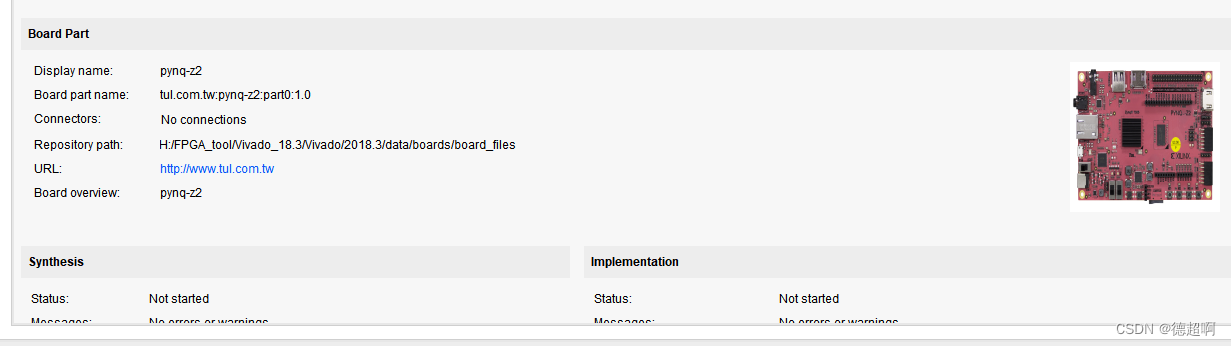

主要的的步骤也比较简单:首先复制板卡文件(上图中的两个文件),然后添加到Vivado路径中。具体的路径是先找到Vivado的安装路径:Vivado->2018.3(因为我安装的是2018.3 的版本,具体的要看你安装的版本)->data -> boards -> board_files 。把板卡文件复制到在boards_files文件夹中,再重启Vivado文件即可选择pynq_z2文件。

pynq-z2板卡文件

链接:https://pan.baidu.com/s/1yPv41kf_1ogfaKeVZfvr8A

提取码:im0k

这篇关于Vivado中添加Pynq-Z2板卡文件的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!