本文主要是介绍【上海大学数字逻辑实验报告】三、组合电路(二),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、实验目的

- 掌握8421码到余3码的转换。

- 掌握2421码到格雷码的转换。

- 进一步熟悉组合电路的分析和设计方法。

- 学会使用Quartus II设计8421码到余3码的转换电路逻辑图。

- 学会使用Quartus II设计2421码到格雷码的转换电路逻辑图。

二、实验原理

- 8421码是最常用的BCD码,在这种编码方式中,每一位二进制代码的“1”都代表一个固定数值。将每位“1”所代表的二进制数加起来就可以得到它所代表的十进制数字。

- 2421码是一种有权码,从左到右,第一位“1”代表“2”,第二位“1”代表“4”,第三位“1”代表“2”,第四位“1”代表“1”。

- 余3码是由8421BCD码加上0011形成的一种无权码,其特点为当两个十进制数的和是9时,相应的余3码的和正好是15,于是可自动产生进位信号,而不需修正。

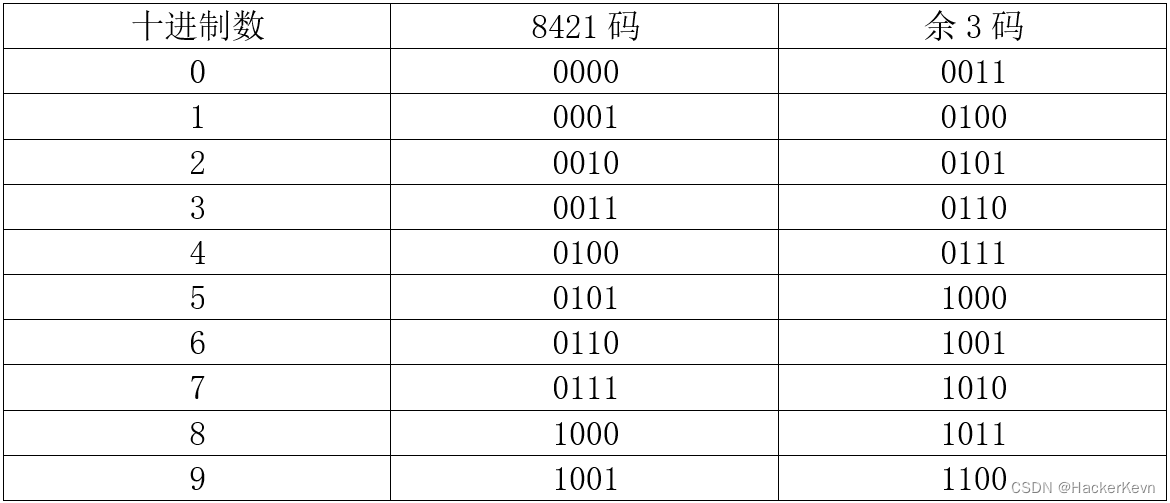

- 8421码与余3码之间的关系:

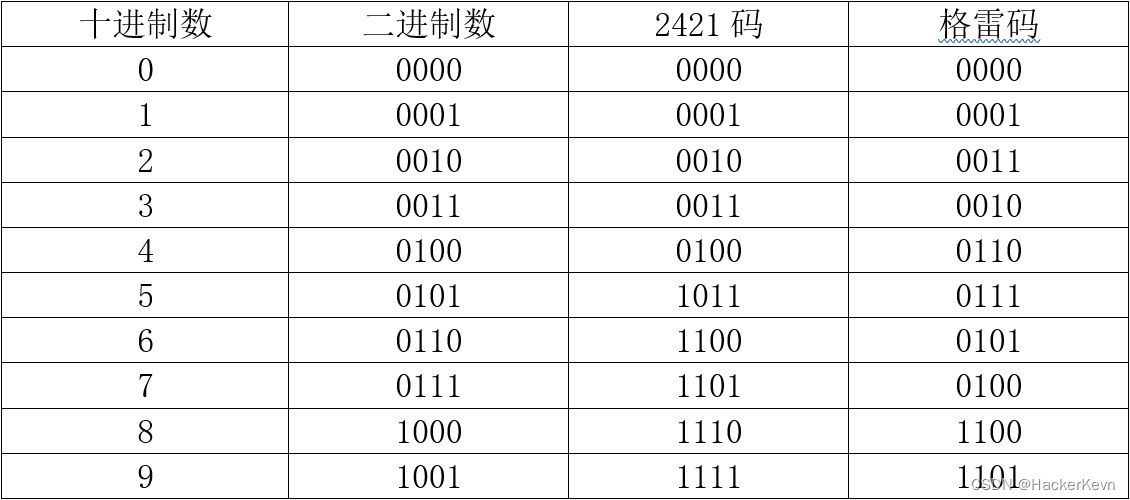

- 2421码与Gray码之间的关系:

三、实验内容

实验任务一:设计8421码到余3码的转换电路

(1) 实验步骤

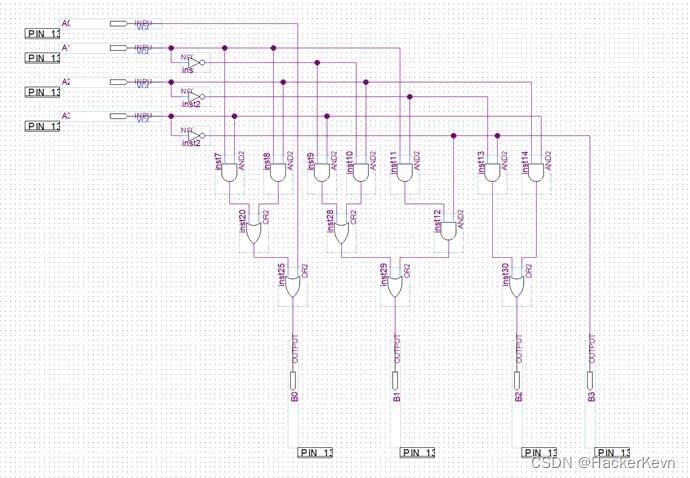

- 用Quartus II设计出如下电路:

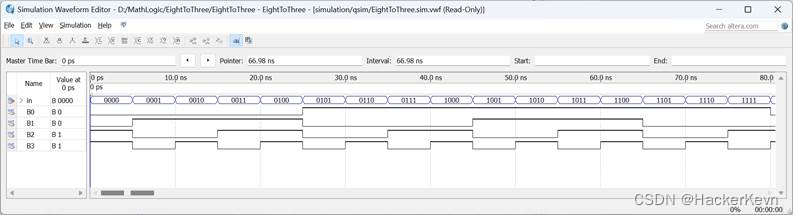

- 编译通过后进行波形仿真,验证电路逻辑功能:

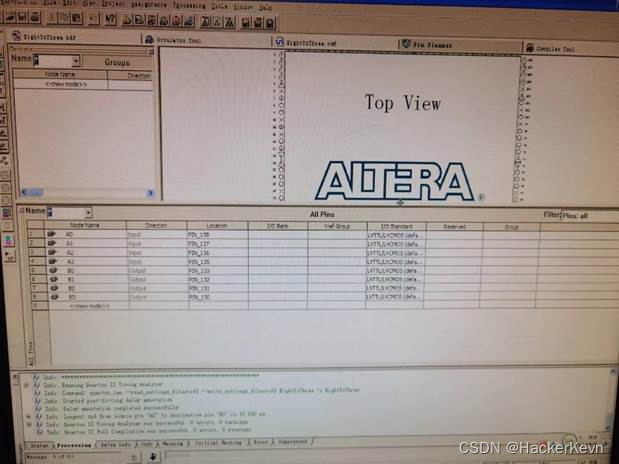

- 仿真通过后,参照原理图定义引脚:

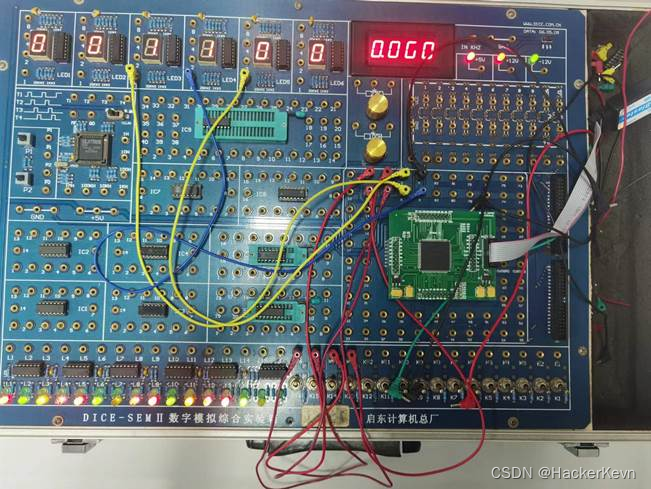

- 生成编程并将文件下载到FPGA。

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

当输入一个8421BCD码时,电路总是能输出对应的余3码。

(3) 数据记录、分析与处理

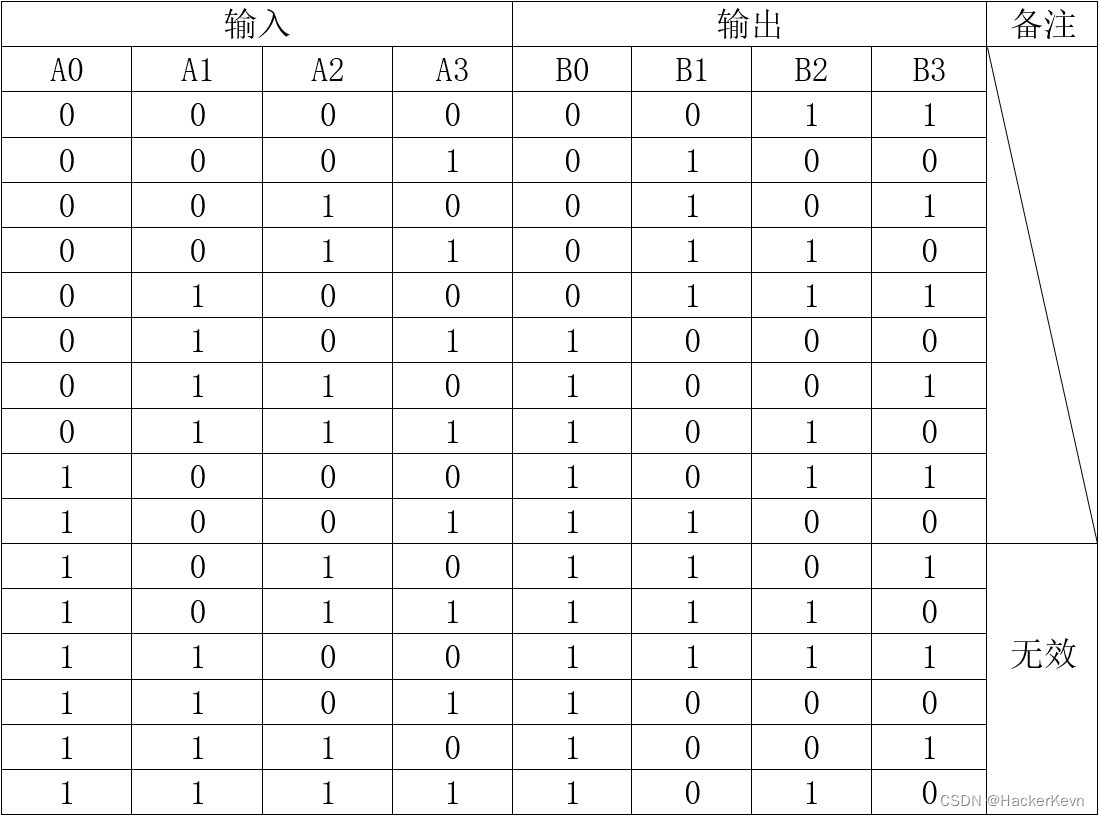

8421码到余3码转换电路的输入输出状态记录表:

(4) 实验结论

通过使用Quartus II设计工具,我们成功地设计并测试了一个8421码到余3码的转换电路。该电路的功能包括输入一个8421BCD码,并产生相应的余3码。实验结果表明,电路在各种输入条件下都表现出良好的性能,符合预期行为。

实验任务二:设计2421码到Gray码的转换电路

(1) 实验步骤

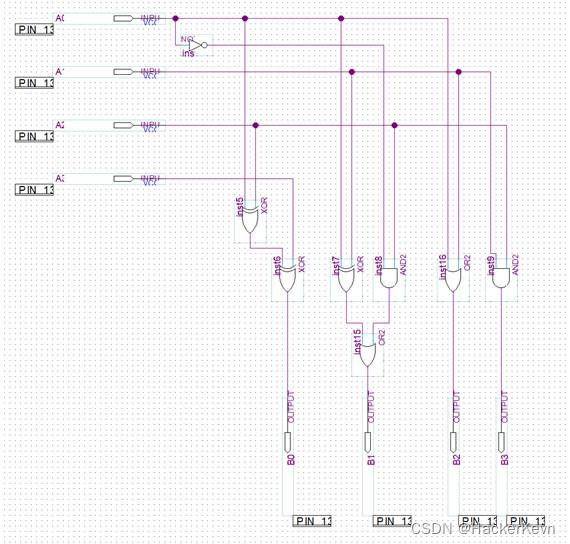

- 用Quartus II设计出如下电路:

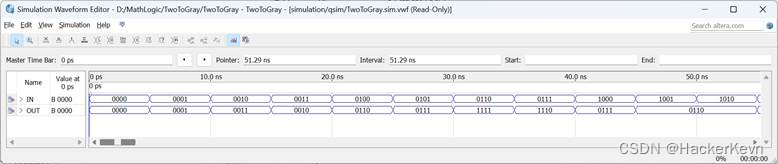

- 编译通过后进行波形仿真,验证电路逻辑功能:

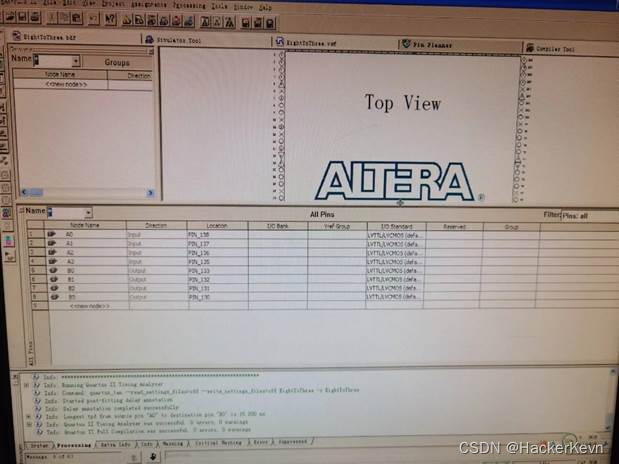

- 仿真通过后,参照原理图定义引脚:

- 生成编程并将文件下载到FPGA。

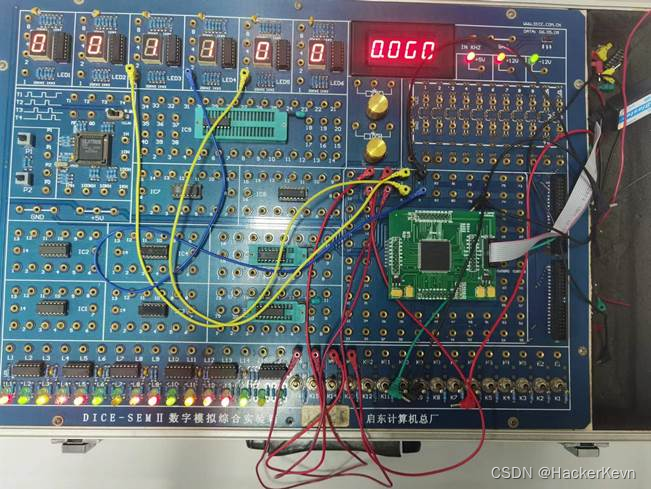

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

当输入一个2421码时,电路总是能输出对应的格雷码。

(3) 数据记录、分析与处理

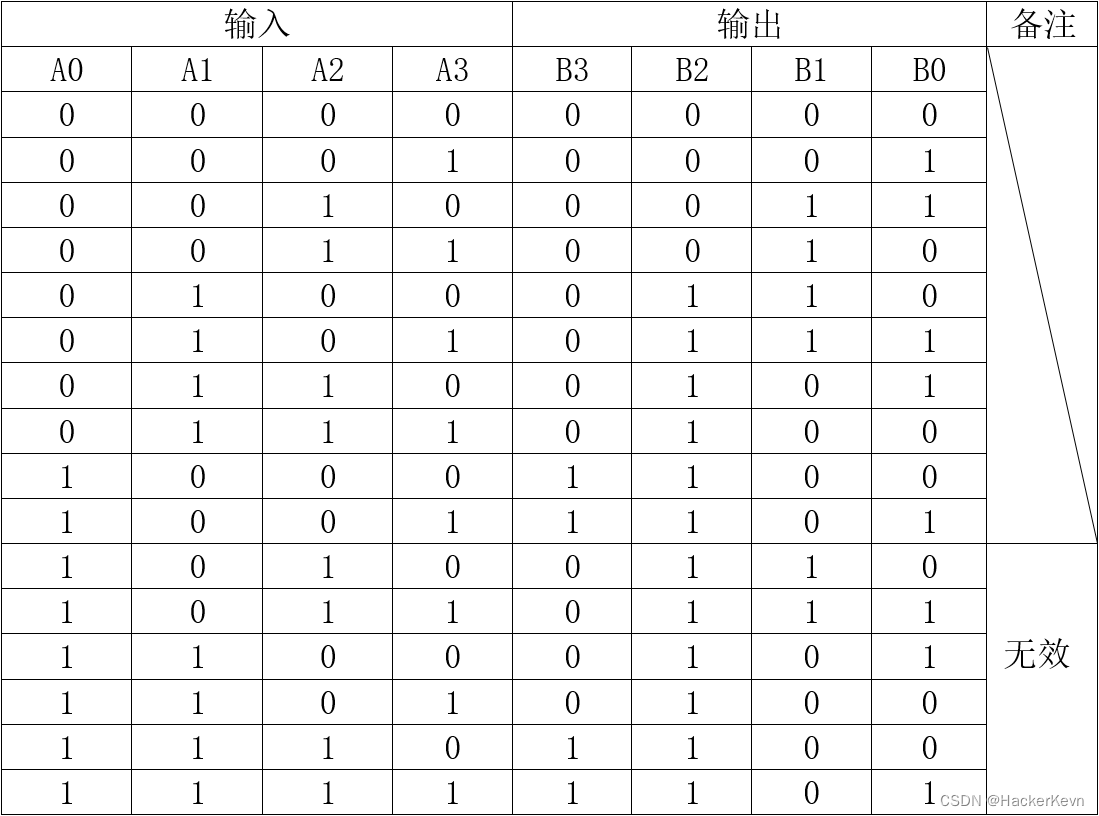

2421码到Gray码转换电路的输入输出状态记录表:

(4) 实验结论

通过使用Quartus II设计工具,我们成功地设计并测试了一个2421码到Gray码的转换电路。该电路的功能包括输入一个2421BCD码,并产生相应的Gray码。实验结果表明,电路在各种输入条件下都表现出良好的性能,符合预期行为。

四、建议和体会

- 在实验前,深入理解编码系统和逻辑门的工作原理是非常重要的。

- 在设计电路时,要确保逻辑门的连接和布局正确无误,以避免错误输出。

- 在测试阶段,使用不同的8421码输入组合来验证电路的正确性。

- 波形模拟的结果对于评估电路的正确性非常重要。

- 这个实验有助于加深对编码系统和逻辑电路设计原理的理解,同时也提供了一个实际的编程和模拟测试经验。为后续进行更复杂的电路设计打下基础。

这篇关于【上海大学数字逻辑实验报告】三、组合电路(二)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!