本文主要是介绍「Verilog学习笔记」整数倍数据位宽转换8to16,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

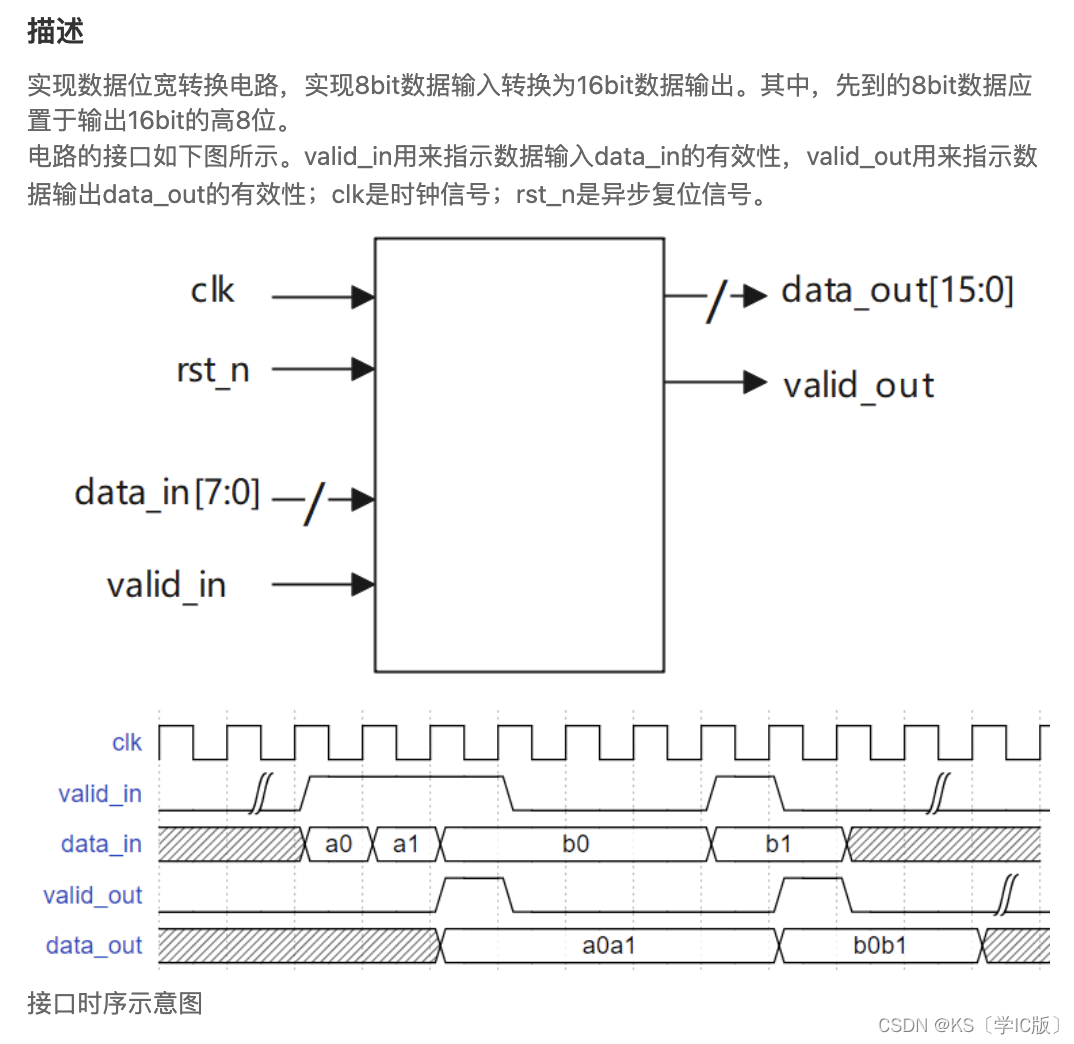

根据时序图,数据是在第二个数据到来之后输出,当仅有一个数据到来时,不产生输出,所以内部需要一个指示信号valid_cnt,用来指示数据缓存状态。当data_lock内已缓存第一个数据时,valid_cnt拉高,当第二个数据到来后valid_cnt拉低

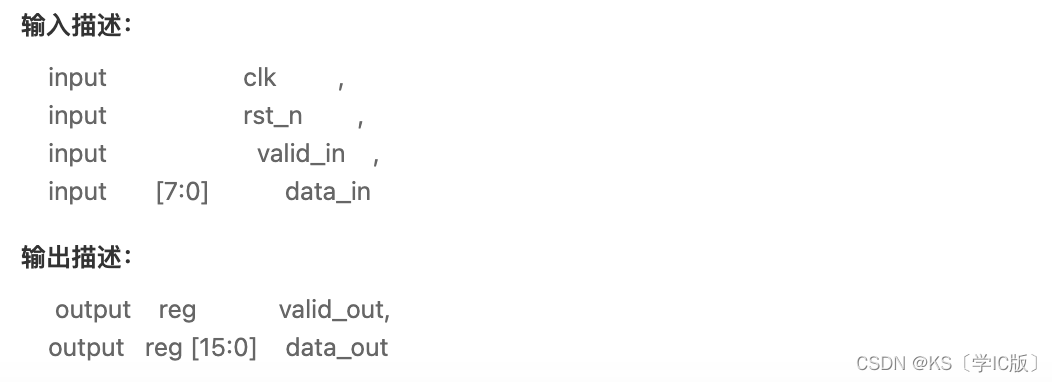

`timescale 1ns/1nsmodule width_8to16(input clk , input rst_n ,input valid_in ,input [7:0] data_in ,output reg valid_out,output reg [15:0] data_out

);reg [7:0] data_lock ; reg valid_cnt ; always @ (posedge clk or negedge rst_n) begin if (~rst_n) valid_cnt <= 'd0 ; else if (valid_in) valid_cnt <= ~valid_cnt ; endalways @ (posedge clk or negedge rst_n) begin if (~rst_n) data_lock <= 'd0 ; else if (valid_in && !valid_cnt) data_lock <= data_in ; endalways @ (posedge clk or negedge rst_n) begin if (~rst_n) valid_out <= 'd0 ; else if (valid_in && valid_cnt == 1'd1) valid_out <= 1'd1 ; else valid_out <= 'd0 ; endalways @ (posedge clk or negedge rst_n) begin if (~rst_n) data_out <= 'd0 ; else if (valid_in && valid_cnt == 1'd1) data_out <= {data_lock, data_in} ; endendmodule这篇关于「Verilog学习笔记」整数倍数据位宽转换8to16的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!