数据位专题

当存在待发送数据时波特发生器才产生对应数据位模式的时钟脉冲

串行外设接口(Serial Peripheral Interface,SPI)模块是用于同外部外设和其他单片机器件进行 通信的同步串行接口。这些外设可以是串行EEPROM、移位寄存器、显示驱动器和模数转换器 (ADC)或音频编解码器。 SPIx 串行接口由以下四个引脚组成:(可由引脚的映射确定四个引脚) ?? SDIx:串行数据输入 ?? SDOx:串行

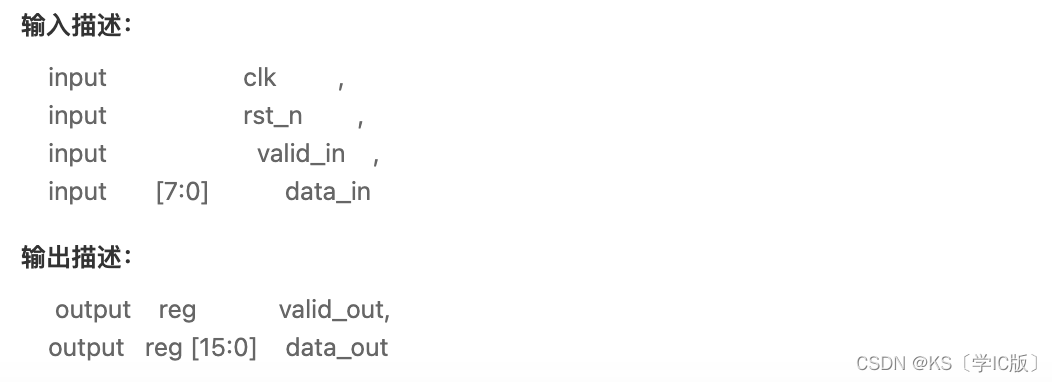

「Verilog学习笔记」整数倍数据位宽转换8to16

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 根据时序图,数据是在第二个数据到来之后输出,当仅有一个数据到来时,不产生输出,所以内部需要一个指示信号valid_cnt,用来指示数据缓存状态。当data_lock内已缓存第一个数据时,valid_cnt拉高,当第二个数据到来后valid_cnt拉低 `timescale 1ns

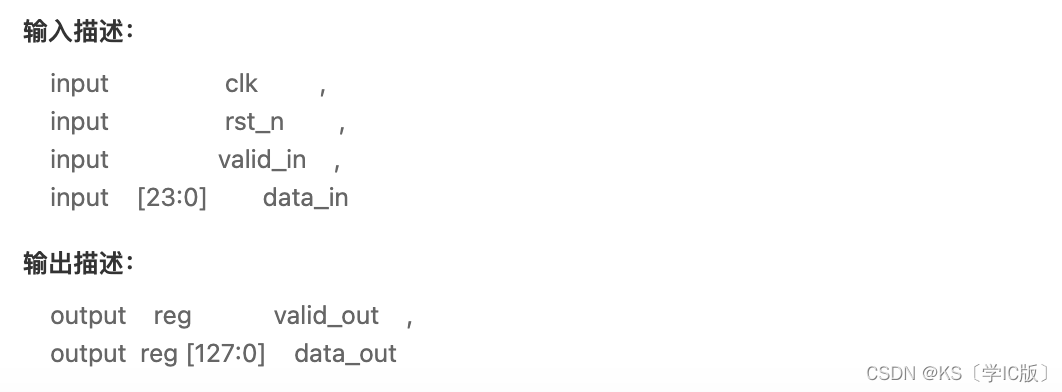

「Verilog学习笔记」非整数倍数据位宽转换24to128

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 要实现24bit数据至128bit数据的位宽转换,必须要用寄存器将先到达的数据进行缓存。24bit数据至128bit数据,相当于5个输入数据+第6个输入数据的拼接成一个输出数据,出于对资源的节省以及时序要求,采用120bit的寄存器(data_lock)进行数据缓存。由

「Verilog学习笔记」非整数倍数据位宽转换24to128

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 要实现24bit数据至128bit数据的位宽转换,必须要用寄存器将先到达的数据进行缓存。24bit数据至128bit数据,相当于5个输入数据+第6个输入数据的拼接成一个输出数据,出于对资源的节省以及时序要求,采用120bit的寄存器(data_lock)进行数据缓存。由

一文读懂串口(波形分析、起始位、数据位、停止位、空闲位)

串口 一、串口(串行接口)二、异步串口(以下统称串口)三、重要参数1、波特率2、报文格式2.1、起始位2.2、数据位2.3、奇偶校验位2.4、停止位2.5、空闲位 四、波形1、具体连接2、波形分析2.1 发送1报文2.2 发送65报文 五、总结 本文使用 STM32F407ZGT6单片机基于标准库进行测试 一、串口(串行接口) 概念: 串行接口 (英文:Serial

Android 串口开发 支持N-8-1(数据位停止位校验方式) 设定

依据使用Cmake的方式 对串口开发的便捷了很多,但是的大多数例子,都不支持对 数据位 停止位 和校验位的设定,毕竟大多数人并不会linux 下的串口编程,查阅很多例子和资料主要参考了:https://www.cnblogs.com/rui1236/p/5988074.html但是按照这个 例子中的 C的写法 无校验(N-8-1)的时候正常,有奇偶校验 发出去的准确,但是收到的却不准确。 比如H