本文主要是介绍ADC采样对MIC的干扰,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

使用EFM8SB的MCU做ADC采样,检测MIC Bias的电源,解码android耳机的线控。

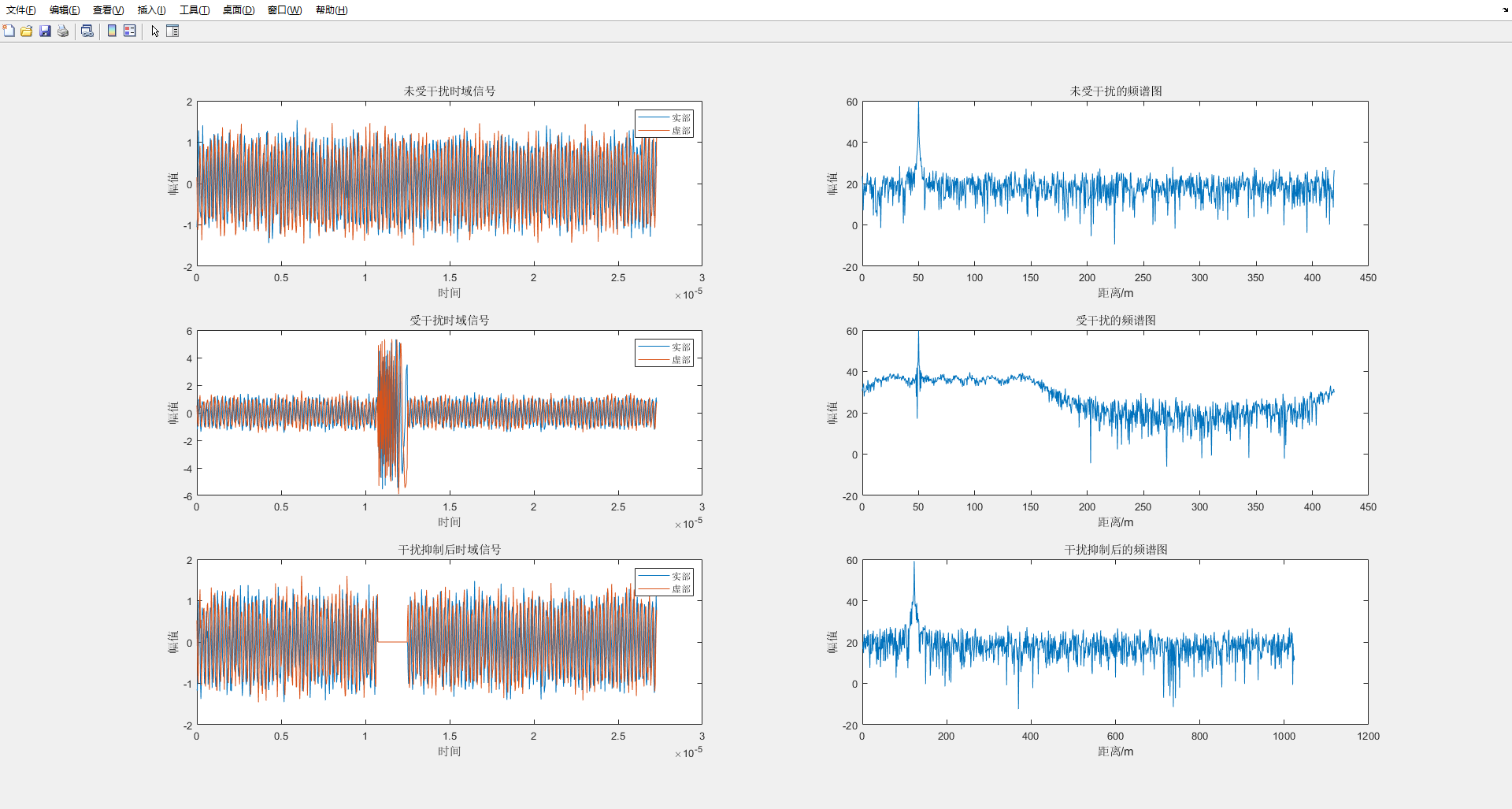

初始时, ADC的采样频率2KHz, 在录音时后播放,能固定的听到接近2K的一个噪声。示波器探测不到明显的噪声信号。

增大ADC采样频率到30KHz, 声音变得更加尖锐,幅度变小,但是听起来很不舒服。

减少到10Hz, 噪声幅度变大,噪声频率跟随到低频。

MicBias增加RC滤波器, ADC恢复到初始2K, MIC录音噪声消除,但是ADC采样结果变差。

查datasheet中

电容增加,导致ADC的settling time增加, 要等到采样值建立起来以后才能开始采样,也就是说采样速度要变慢。

最终将采样速率降到了200Hz, 保证了采样的准确度和Mic+RC(0.1uF)滤波后的效果。

下图是ADC settling time的说明

这篇关于ADC采样对MIC的干扰的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!