本文主要是介绍基于Xilinx CMT设计低抖动的高性能时钟,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

随着FPGA内部同步电路运行时钟频率的提高,时钟抖动将成为制约设计时序性能的显著因素。Xilinx FPGA提供高性能的时钟管理单元(CMT,Clock Management Tiles),可帮助设计者获得低抖动的FPGA内部运行时钟。

Xilinx对其各系列FPGA,均提供时钟资源的专用手册,本文不是手册的翻译,而是针对实际设计的一些对比测试,以加深对Xilinx FPGA CMT应用的理解。本设计基于Spartan-6 LX150完成,其中部分电路需要运行至240MHz或300MHz,最终,此FPGA片内高速时钟的方案如下图:

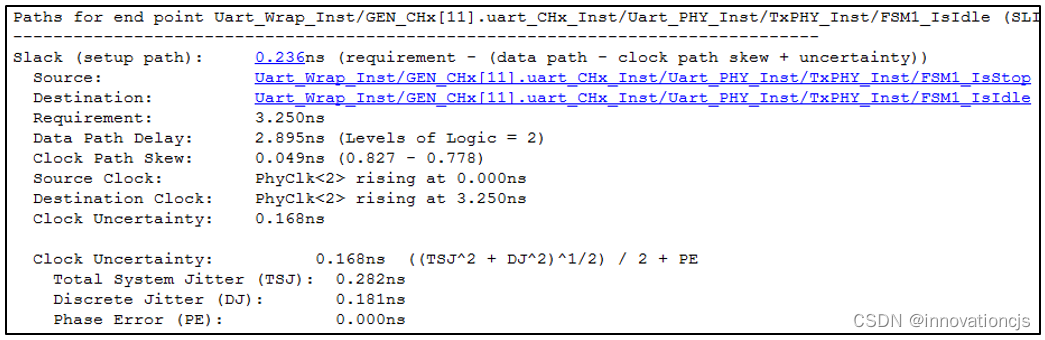

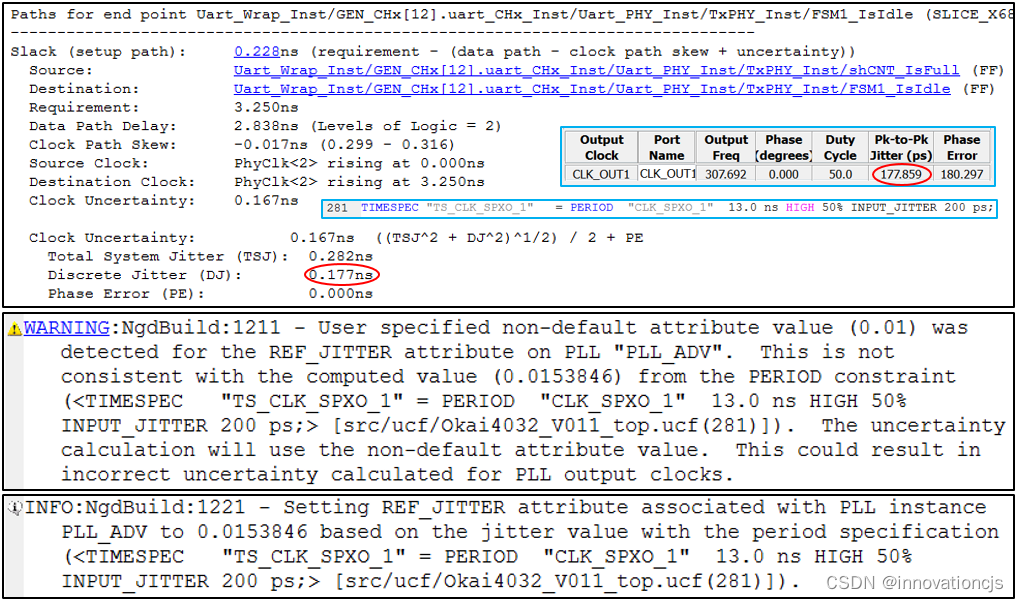

布局/布线后,静态时序报告中给出的PhyClk[3:0]抖动情况如下图(注:四组PhyClk的抖动指标一致,且在UCF文件中添加了200ps的SYSTEM_JITTER,并为输入时钟添加了200ps的INPUT_JITTER):

可以看到,时钟周期约束为3.25ns的设计,其中PLL输出时钟的离散抖动(Discrete Jitter)为0.181ns,设计指定的系统抖动(System Jitter)为0.282ns,合成时钟不确定度(Clock Uncertainty)为0.168ns(占比时钟周期的5.17%),可以认为针对本设计的时钟是一个低抖动的高性能时钟,不会成为设计时序的瓶颈。

注:本文初稿完成至1.5.1章节,经后续研究,在1.7章节给出了更优性能的设计。

1.1 DCM输出至PLL输入布线方式的测试

根据Xilinx UG382(v1.10)第112页的介绍,DCM + PLL应用时,PLL输出时钟抖动性能最优的方案是将DCM + PLL布局进同一个CMT,并由DCM输出直接驱动PLL输入,当然,也可在DCM输出至PLL输入之间插入一级BUFG:

作为对比测试,在DCM输出至PLL输入之间插入一级BUFG, XST布局/布线完成后,DCM → BUFG → PLL的布局如下:

- DCM_CLKGEN_X0Y3 → BUFGMUX_X2Y4 → PLL_ADV_X0Y3;

- DCM_CLKGEN_X0Y8 → BUFGMUX_X2Y1 → PLL_ADV_X0Y2。

可以看到,在DCM输出至PLL输入之间插入一级BUFG后,XST未采用位于同一CMT的DCM和PLL实现,但静态时序报告给出的输出时钟性能指标,与DCM输出直接驱动PLL输入的方案一致:

虽然XST的静态时序分析工具没有区分DCM输出至PLL输入之间不同布线方式的抖动性能,但UG382中解释的比较清楚:“DCM与PLL布局于同一个CMT,DCM输出直接驱动PLL输入,将采用CMT内较短的、专用的布线资源,因此拾取更低的电源和线路噪声,可降低PLL输出时钟的抖动”。

所以,当采用DCM驱动PLL构建Spartan-6 FPGA片内低抖动时钟时,建议设计保证:DCM与PLL位于同一CMT,DCM输出直接驱动PLL,DCM输出至PLL输入之间不插入BUFG。

1.2 CMT输出时钟抖动的快速评估

Xilinx强调,基于其FPGA器件之设计的时序性能,以静态时序分析软件给出的分析报告数据为准。

但要获得一个设计的静态时序分析报告,并不是一件容易的事,这需要设计者进行完整的设计,当设计指标不满足需求时,参数迭代是一个费时间的工作。

以本文基于Spartan-6 LX150的设计为例,一次综合、布局、布线、静态时序分析的完整流程大致需要10分钟的时间。那么,针对Spartan-6 FPGA片内时钟的抖动性能,Xilinx提供了哪些快速评估的手段?

1.2.1 基于数据手册的快速评估

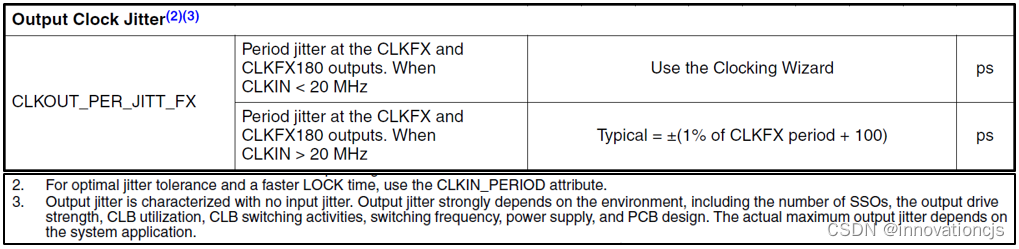

Spartan-6数据手册DS162(V3.1.1)中,未以数据或公式的方式给出PLL输出时钟的抖动性能指标,要求查看Clocking Wizard软件给出的数据。如下图:

DS162以计算公式的方式给出了DCM_CLKGEN的DFS输出抖动指标,如下图:

DCM_SP的DFS输出抖动指标分两种情况:输入时钟频率 < 20MHz时,需使用Clocking Wizard软件评估;输入时钟频率 > 20MHz时,DS162给出了输出抖动的计算公式。如下图:

本例中UCF给定的输入时钟周期为52ns,前级DCM倍频4x,输出时钟周期为13ns,仅DCM_CLKGEN可依据数据手册评估其输出抖动。代入数据手册的计算公式,可得DCM_CLKGEN的输出时钟抖动为:

1.2.2 基于Clocking Wizard软件快速评估

将输入19.231MHz(周期52ns),输出76.925MHz(周期13ns)的设计参数导入Clocking Wizard软件,给出的DCM_CLKGEN输出抖动峰-峰值为251.999ps,与根据数据手册计算的典型值一致。值得注意的是:

- Clocking Wizard计算DCM_CLKGEN输出时钟抖动时,未计算输入时钟抖动;

- UG382指明了DCM在原理上不具备抑制输入抖动的功能;

- DS162中的备注指明了DCM的实际输出抖动与设计强相关。

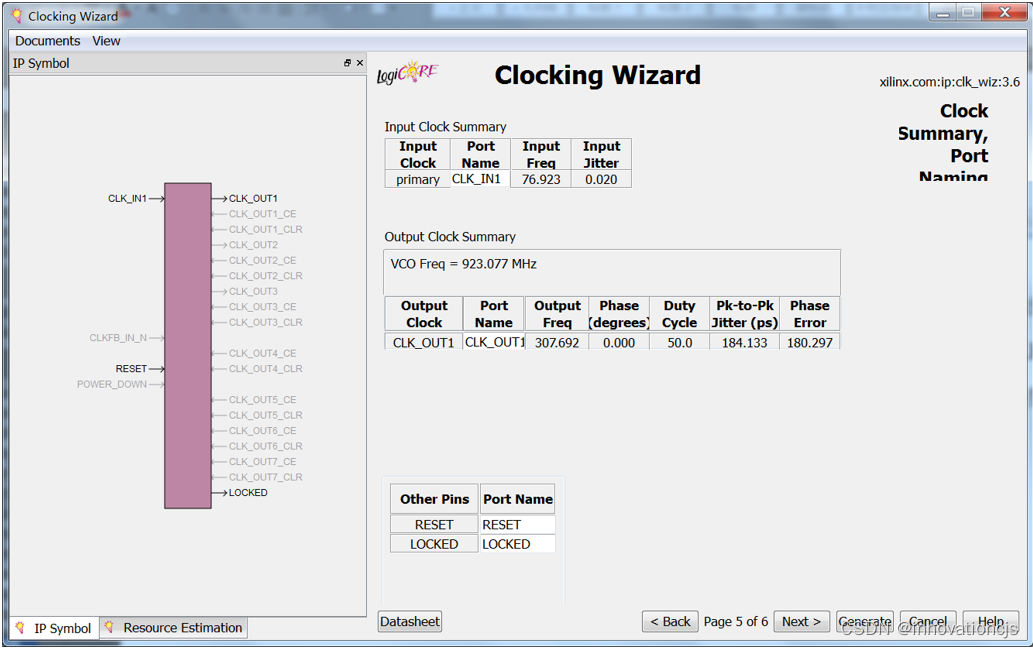

对于PLL的输出时钟抖动,Spartan-6数据手册DS162(V3.1.1)中未给出计算公式,数据手册要求查看Clocking Wizard软件的结果。将前级DCM_CLKGEN的输出参数:13ns ±126ps导入Clocking Wizard,并手动配置PLL的属性参数与前文设计文件中的一致:

Clocking Wizard给出的PLL输出抖动峰-峰值为184.133ps,前文中相同参数下XST静态时序报告中给出的峰-峰值为181ps,可以看到,Clocking Wizard软件给出的计算数据与XST静态时序报告中的数据一致性很高。(注:本文初稿完成至1.5.1章节,经后续研究,对于DCM驱动PLL的时钟结构,未能明确XST静态时序分析工具是如何将DCM输出时钟抖动计算入PLL的输入时钟抖动?故此处Clocking Wizard与XST静态时序分析工具的数据对比方式是不合适的。)

1.3 前级DCM的选择

Spartan-6 FPGA的数字时钟管理单元(DCM,Digital Clock Managers)在使用时有两种模式:DCM_SP、DCM_CLKGEN。从Xilinx UG382和DS162可以获知,使用DCM的数字频率合成器(DFS,Digital Frequency Synthesizer)时,输出时钟(CLKFX)的抖动性能有较为明显的差距,DCM_CLKGEN的抖动性能显著优于DCM_SP。

本设计基于DCM驱动PLL实现低抖动的片内时钟,前级DCM有两种选择,作为对比测试,分别使用DCM_SP、DCM_CLKGEN实现设计,并完成综合、布局、布线和静态时序分析。

值得注意的是:两种方式,针对PLL的输出时钟抖动,XST的静态时序分析工具给出了相同的数据。意味着在本设计的时钟方案下,XST的静态时序分析工具未能区分出PLL前级不同DCM元件的抖动性能差异?

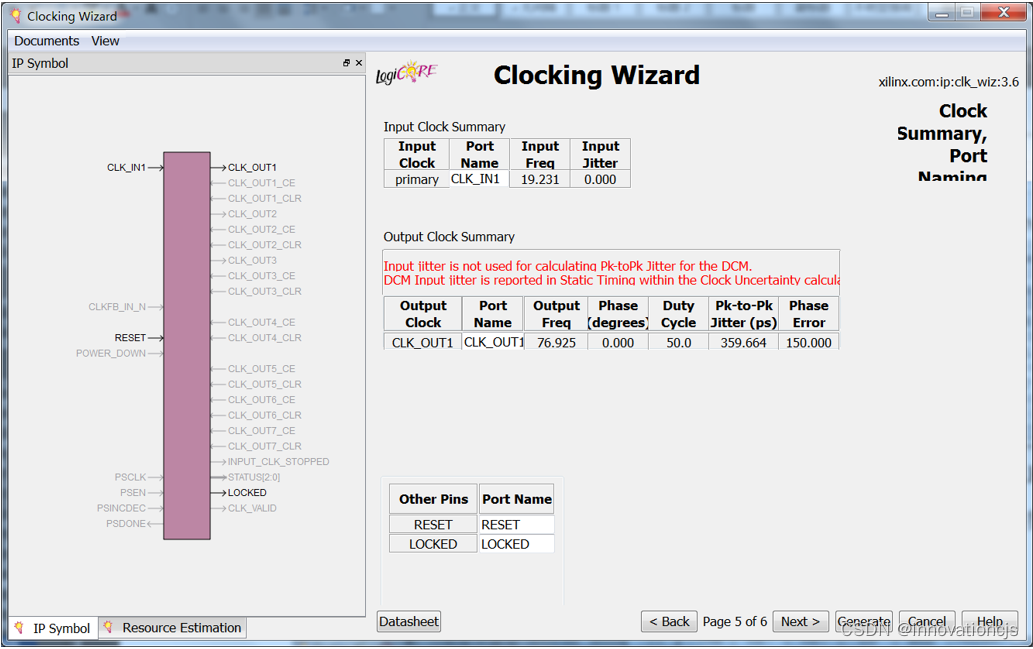

将输入19.231MHz(周期52ns),输出76.925MHz(周期13ns)的设计参数导入Clocking Wizard软件,并选择DCM_SP元件,Clocking Wizard软件给出的输出抖动峰-峰值为359.664ps,相对同样参数时,DCM_CLKGEN的251.999ps输出抖动,DCM_SP的性能下降了约42.9%:

将前级DCM_SP的输出参数:13ns ±180ps导入Clocking Wizard,并手动配置PLL的属性参数与前文设计文件中的一致,最终给出的PLL输出抖动峰-峰值为198.104ps:

可以看到,DCM_SP + PLL和DCM_CLKGEN + PLL两个方案,Clocking Wizard给出的输出抖动数据,后者相对前者有着明显的改善,这更符合UG382和DS162手册的描述。

所以,当采用DCM驱动PLL构建Spartan-6 FPGA片内低抖动时钟时,建议采用DCM_CLKGEN + PLL的方案。

1.4 本设计案例前级DCM的必要性

从前文的测试情况来看,本设计基于DCM驱动PLL实现FPGA片内低抖动时钟时,XST的静态时序分析工具可能存在两个容易导致设计者忽略的问题:

- DCM输出至PLL输入之间能否插入一级BUFG?

- 前级DCM选择DCM_SP、DCM_CLKGEN对最终PLL输出时钟的抖动性能有无影响?

从本文设计案例的测试来看,XST的静态时序分析工具不能区分这两个问题中各自的两种情况。

本设计中,PLL前级需要保留DCM的原因在于:本设计之电路板的板载晶振CLK0_SPXO为10MHz,CLK1_SPXO为14.7456MHz,均不满足Spartan-6 FPGA的最低PLL输入时钟频率指标,故而需要在PLL前级,采用DCM将板载晶振输入至FPGA的时钟倍频到PLL输入频率允许的范围(最低19MHz):

既然选择的板载晶振频率,增加了FPGA片内时钟设计的复杂度,那么选择这两个晶振频率的权衡因素有哪些?这与本文主旨的相关度不是很高,不展开介绍:

- 从降低电路板EMI的角度,希望给FPGA提供频率尽量低的外部晶振输入;

- Spartan-6 FPGA DCM的输入频率范围是5 ~ 250MHz,而我设计时通常会避开器件的参数边界;

- 10MHz/14.7456MHz这两种规格的晶振,使用的人多,货源充足,价格便宜。

1.5 PLL_BASE属性参数的测试

UUG382第104~106页给出了Spartan-6 FPGA PLL的属性参数说明,对其中个人理解不够透彻的参数进行测试。

1.5.1 BANDWIDTH属性参数

UG382第104页对BANDWIDTH属性参数的描述如下:

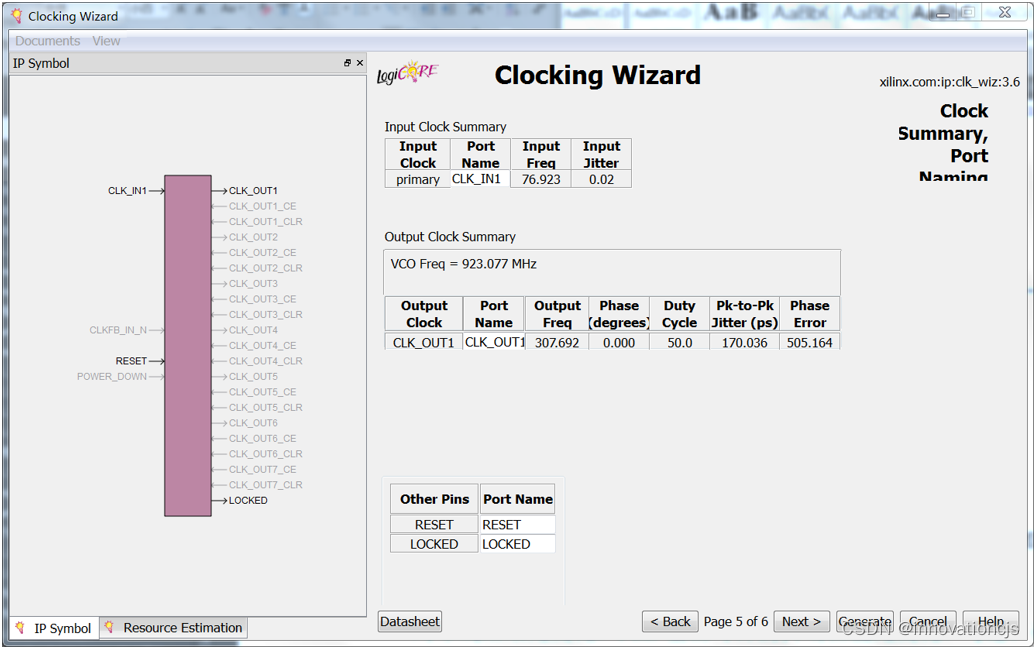

PLL的属性参数BANDWIDTH设为LOW,XST静态时序报告中给出的PLL输出时钟抖动为0.172ns,相比设为OPTIMIZED的0.181ns,有0.009ns的改善:

将前级DCM_CLKGEN的输出参数:13ns ±126ps导入Clocking Wizard,并手动配置PLL的属性参数BANDWIDTH为LOW,Clocking Wizard给出的输出抖动峰-峰值为170.036ps,相比设为OPTIMIZED的184.133ps,有约14ps的改善:

从PLL的基本工作原理可知,PLL是一个闭环负反馈系统,它能减小输入时钟抖动的原理正是来自于环路低通滤波器对输入抖动的积分,环路低通滤波器带宽越低,输出时钟的抖动越低,与之对应的,输出时钟相对输入时钟的静态相位误差越大(即Clocking Wizard软件中给出的Phase Error)。

Spartan-6 FPGA的PLL提供HIGH/LOW两个带宽档位选择,DS162给出了各自典型的环路带宽值:

在例化Spartan-6 FPGA的PLL_BASE原语时,其属性参数BANDWIDTH有HIGH/LOW/OPTIMIZED三个选项,本文进行的各项测试中,选择HIGH或OPTIMIZED,Clocking Wizard软件和XST静态时序分析工具均处理为HIGH。

关于属性参数BANDWIDTH的设计建议:如本文引用的案例设计,当FPGA片外输入时钟与PLL输出时钟之间无相位关系的要求时,从降低片内高速时钟抖动的角度优化,建议将PLL的属性参数BANDWIDTH设为LOW。

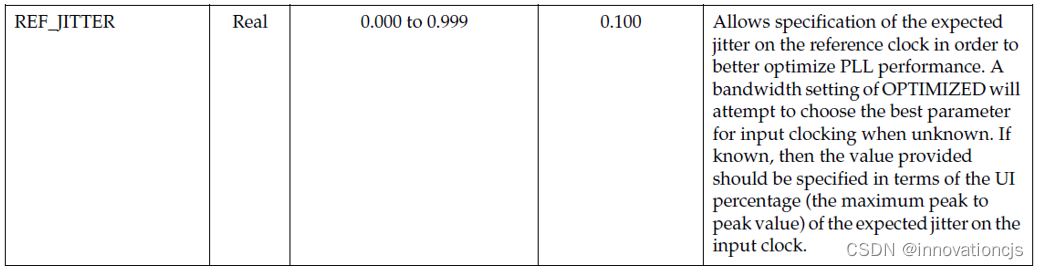

1.5.2 REF_JITTER属性参数

UG382第105页对REF_JITTER属性参数描述如下:

使用Clocking Wizard软件,保持其它参数不变的情况下,修改REF_JITTER属性参数,Clocking Wizard软件给出的输出抖动数据无变化。

PLL的属性参数BANDWIDTH设为OPTIMIZED,COMPENSATION设为DCM2PLL,对比测试了属性参数REF_JITTER分别设为0.01和0.1,XST的布局布线结果无变化,PLL输出时钟的抖动性能无变化。

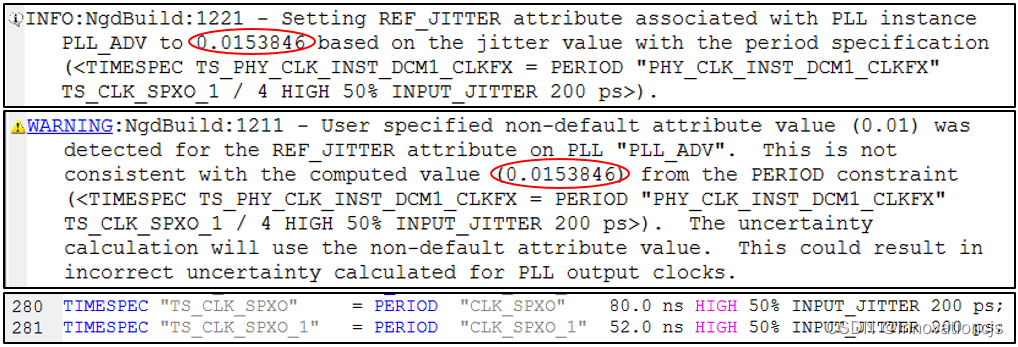

查看XST的Translation Report,发现XST依据:UCF文件中对输入时钟CLK1_SPXO的INPUT_JITTER约束,设计文件中DCM_CLKGEN和PLL_BASE的倍/分频系数设置,计算出一个PLL_BASE输入时钟的抖动参数,覆盖了例化PLL_BASE原语时填写的REF_JITTER属性参数,同时发现,REF_JITTER设为默认值(0.1)和非默认值时,XST在Translation Report中给出的提示信息不一致,设为默认值时,给出的是提示信息(INFO:NgdBuild:1221),非默认值时,给出的是警告信息(WARNING: NgdBuild:1211),如下图:

PLL_BASE属性参数REF_JITTER的单位是UI,即填写的数据是输入时钟周期的比例,CLK1_SPXO在UCF中指定的周期是52ns,经前级DCM的4倍频后,PLL_BASE的输入时钟周期为13ns,附加200ps的峰-峰值输入抖动,有:0.2ns / 13ns = 0.0153846。进一步的测试表明:

- UCF文件中,去掉CLK1_SPXO的INPUT_JITTER约束,XST不覆盖例化PLL_BASE原语时填写的REF_JITTER属性参数(Translation Report中无相关信息);

- UCF文件中,指定CLK1_SPXO的INPUT_JITTER,即便约束为0.0ps,XST都将用指定的数据覆盖例化PLL_BASE原语时填写的REF_JITTER属性参数(Translation Report中有相关信息)。

Clocking Wizard软件计算PLL输出时钟的抖动时,未计算REF_JITTER属性参数值,那么,XST静态时序分析工具到底是怎么考虑这个输入时钟的抖动数据呢?没办法,继续测试…

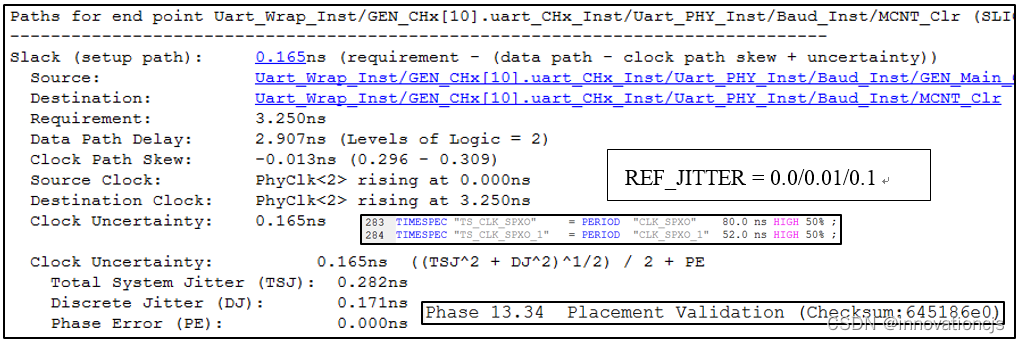

在UCF中分别为CLK1_SPXO指定0.00ps、100ps、200ps的INPUT_JITTER,例化PLL_BASE原语时,BANDWIDTH = OPTIMIZED、REF_JITTER = 0.1。测试结果表明:XST静态时序分析工具将CLK1_SPXO指定的INPUT_JITTER参数导入了PLL_BASE的REF_JITTER属性参数,并给出不同的输出时钟抖动指标(0.171ns、0.174ns、0.181ns)。如下图:

去掉UCF文件中CLK1_SPXO的INPUT_JITTER约束,例化PLL_BASE原语时,BANDWIDTH = OPTIMIZED,REF_JITTER分别设为0.0、0.01、0.1。

测试发现,XST静态时序分析工具忽略了REF_JITTER属性参数值,给出的输出时钟抖动数据与前项测试中INPUT_JITTER = 0.0ps时一致:0.171ns。更进一步的对比INPUT_JITTER = 0.0ps,REF_JITTER = 0.0、0.01、0.1共计四次布局结果,XST给出的布局验证校验和一致:645186e0。测试结果如下图:

综合上述针对属性参数REF_JITTER的测试,建议:例化PLL_BASE原语时,属性参数REF_JITTER保持默认值(0.1)不变。

在前文1.3节中,关于前级DCM选择DCM_SP或DCM_CLKGEN的测试时,尚未进行属性参数REF_JITTER的测试研究,1.3节测试时,UCF中设定的INPUT_JITTER = 200ps,测试发现,PLL前级分别为DCM_SP和DCM_CLKGEN时,XST静态时序分析工具给出了相同的PLL输出时钟抖动数据。

此处补充测试INPUT_JITTER = 0.0ps时,PLL前级分别为DCM_SP和DCM_CLKGEN的情况?XST静态时序分析工具在两种情况下,仍然给出了一致的PLL输出时钟抖动数据:

至此,不得不提出一个疑问: Spartan-6 FPGA DCM(DCM_SP/DCM_CLKGEN)驱动PLL的时钟方案,XST静态时序分析工具是否准确地评估了PLL输入时钟的抖动数据?

1.5.3 CLKIN_PERIOD属性参数测试

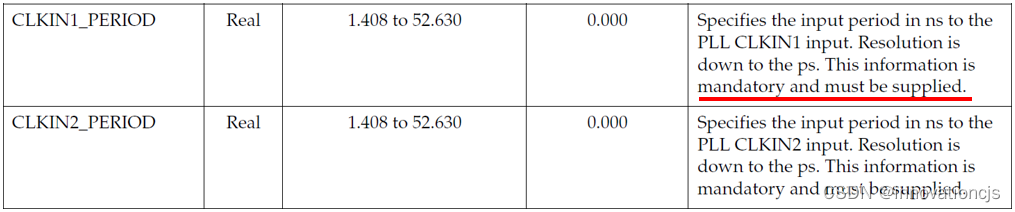

UG382第 105页对CLKIN_PERIOD属性参数的描述如下(这是一个强制的,因此必须提供的参数):

XST的布局、布线、静态时序分析工具会依据UCF文件中对输入时钟的PERIOD约束值,覆盖例化PLL_BASE原语时设定的CLKIN_PERIOD属性参数值。查看XST的Translation Report可以获知相关信息:例化PLL_BASE原语时设定为默认值(0.0),以提示信息的方式给出;非默认值时,以警告信息的方式给出。如下图:

建议:例化PLL_BASE原语时,属性参数CLKIN_PERIOD保持默认值(0.0)不变。

1.6 片外时钟输入直接驱动PLL

在前文1.3节和1.5.2节的测试中发现:DCM + PLL的时钟方案,XST静态时序分析工具不区分前级是DCM_SP还是DCM_CLKGEN。而:

- DS162中DCM_SP和DCM_CLKGEN的抖动指标有着显著差异;

- Clocking Wizard软件对相同输入/输出参数,给出的输出抖动数据有着显著差异;

- 本文1.8节的测试,XST静态时序分析工具给出的输出抖动数据有着显著差异。

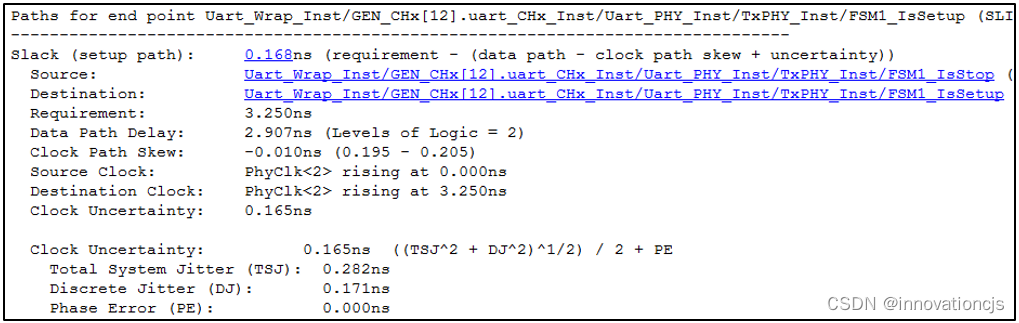

为验证XST静态时序分析工具是否直接忽略了前级DCM的输出抖动?修改设计文件,将PhyClk[0:3]的方案修改为直接由片外晶振CLK1_SPXO驱动PLL倍频输出,UCF文件中约束CLK1_SPXO的周期为13ns,分别测试INPUT_JITTER = 0.0ps、100ps、200ps时,XST静态时序工具对PhyClk[2]抖动的计算结果,并与相同参数下Clocking Wizard软件的计算结果对比,二者完全一致,如下图:

可以看到,单独使用PLL,INPUT_JITTER = 0.0ps、100ps、200ps时,XST静态时序分析工具给出的PLL输出时钟抖动数据依序为:0.168ns、0.170ns、0.177ns。DCM_CLKGEN + PLL时,19.5.2节对应的测试结果依序为:0.171ns、0.174ns、0.181ns。

至此,彻底不明白:DCM + PLL的时钟方案,XST静态时序分析工具是如何将前级DCM输出时钟抖动计算入PLL输入时钟抖动?只能按照Xilinx的要求,以静态时序报告的数据为准。

1.7 PLL倍/分频系数组合的测试及优化

Xilinx Spartan-6 FPGA PLL的工作原理如下图(框图摘自UG382,各节点频率指标摘自DS162中-2速度等级器件栏):

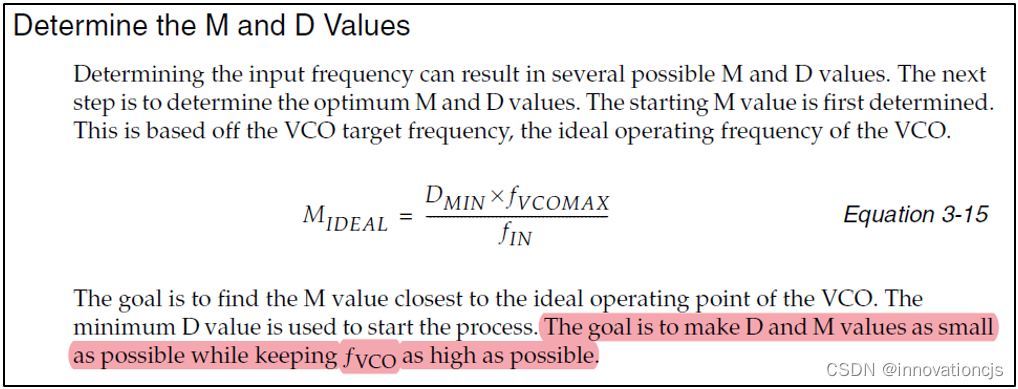

从PLL的原理FO=FIN×M/D/O 可知,当我们选定输入和输出频率后,需要根据各节点的频率范围,结合M、D、O系数各自的取值范围,从众多系数组合中剔除掉不满足限制条件的组合,即便如此,一个设计通常都会有多个系数组合满足各节点频率范围的限制条件。

UG382第102页给出了Spartan-6 FPGA PLL的系数选择指南。其中有这样一段(UG472第77页、UG572第46页有着完全一致的描述):

我看见了,但仍然主动忽略了,原因在前文提到过:我在设计中总是习惯避开器件指标的边界。所以,我为本设计的PLL选择了M = 24、D = 2、O = 3的系数组合,在添加SYSTEM_JITTER(= 200ps)和INPUT_JITTER(= 200ps)的约束条件下,获得了181ps的片内时钟抖动性能,本以为已经很好了,事实证明,我错了!

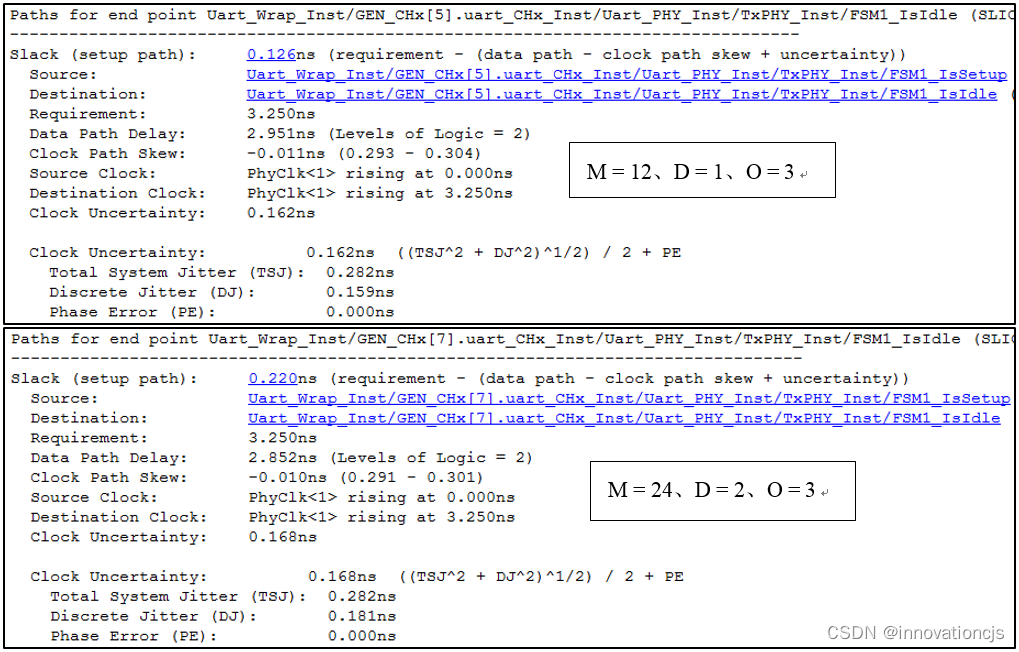

为了感受这个系数组合的影响,保持前级DCM_CLKGEN倍频系数4不变,UCF中SYSTEM_JITTER(= 200ps)和INPUT_JITTER(= 200ps)不变,PLL_BASE的属性参数如下设定:

- BANDWIDTH = OPTIMIZED

- CLK_FEEDBACK = CLKFBOUT

- REF_JITTER = 0.1

测试(M = 12、D = 1、O = 3),(M = 24、D = 2、O = 3),(M = 36、D = 3、O = 3)三组PLL_BASE系数组合,XST静态时序分析工具给出的PLL输出时钟抖动数据依序为:0.159ns、0.181ns、0.195ns。本组测试中,FVCO、FO相同,FPFD由高到低变化,可以看到,PLL环路鉴频鉴相器(PFD)的工作频率越高,FVCO输出抖动越小。就本组测试而言,最差(0.195ns)相对最好(0.159ns),其性能下降了约22.6%。三组测试的静态时序报告如下图:

本设计的需求是:将板载晶振CLK0_SPXO(10MHz)倍频24倍、CLK1_SPXO(14.7456MHz)倍频16倍,经BUFGMUX切换输出至片内目标电路,优化倍频输出时钟的抖动性能。从前文的测试和分析可知:

- 因板载晶振时钟频率不满足Spartan-6 FPGA PLL的最低输入频率要求,须采用DCM_CLKGEN + PLL_BASE的方案实现;

- PLL_BASE的FPFD和FVCO工作频率越高,FVCO输出抖动越小。

将本时钟方案修改为:

- 前级DCM_CLKGEN倍频24或16,获得目标频率;

- 后级PLL_BASE系数设定M = 3、D = 1、O = 3,令PLL_BASE的FPFD和FVCO工作频率尽量高。

修改后的设计,XST静态时序分析工具给出的时序报告如下图(特将前文的报告截图放于此处,便于对比):

可以看到,相同的设计需求和基础实现方案,通过研读Xilinx官方手册,优化DCM_CLKGEN和PLL_BASE的系数组合,可以在一个本已不错的设计性能(0.181ns)基础之上,提升至更高性能(0.128ns),获得了约29.3%的性能提升。

1.8 本设计能差到什么程度?

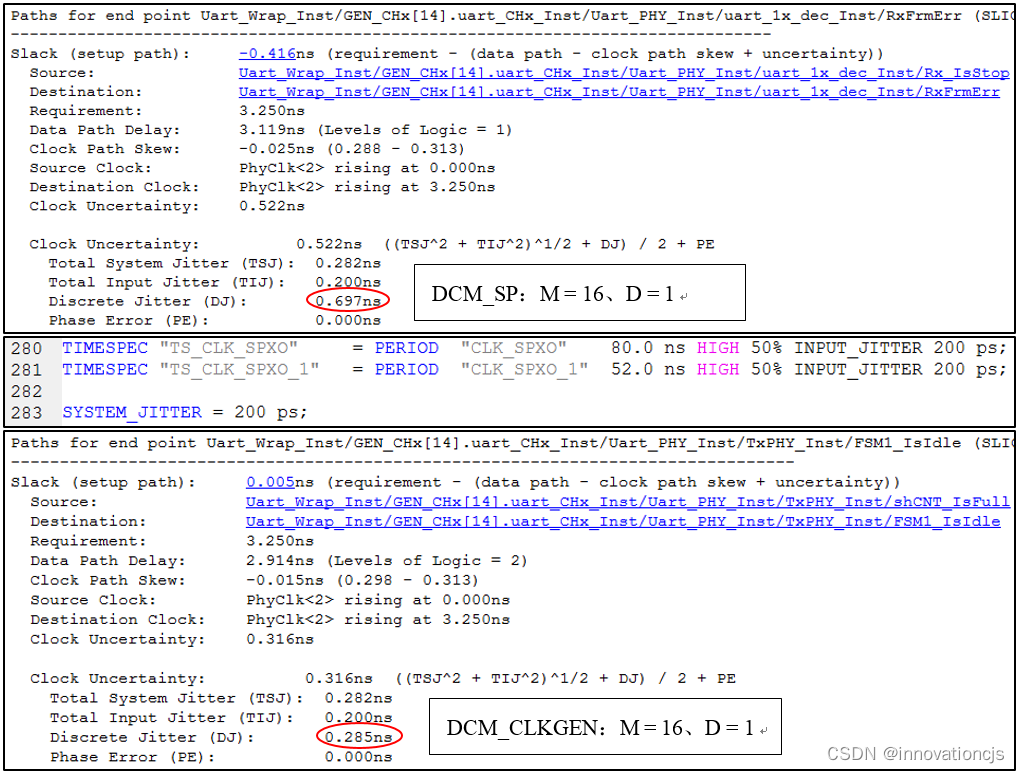

从前文的测试和分析可知,实现本设计的需求,最差方案是采用DCM_SP倍频至目标频率,不经后级PLL做抖动抑制,直接输出至片内目标电路使用。

能有多差?试试呗,按构想修改设计,布局、布线完成后,XST静态时序分析工具给出的报告数据如下图:

可以看到(对比基准为DCM_CLKGEN + PLL_BASE的方案,PLL_BASE输出时钟抖动为0.128ns,合成时钟不确定度为0.155ns):

- 采用DCM_SP直接倍频至目标频率时:输出时钟抖动为0.697ns,是0.128ns的5.45倍;合成时钟不确定度为0.522ns,是0.155ns的3.37倍。

- 采用DCM_CLKGEN直接倍频至目标频率时:输出时钟抖动为0.285ns,是0.128ns的2.23倍;合成时钟不确定度为0.316ns,是0.155ns的2.04倍。

这篇关于基于Xilinx CMT设计低抖动的高性能时钟的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!