cmt专题

基于RTOS(实时操作系统)的CMT液晶屏控制器驱动程序开发与实现

RTOS(实时操作系统)提供了一种有效的方式来管理和调度多任务系统,对于液晶屏控制器的驱动程序开发来说,RTOS能够提供良好的实时性和可靠性。本文以RTOS为基础,设计并实现了一个用于控制CMT液晶屏的驱动程序。在设计过程中,我们首先介绍了液晶屏和RTOS的基本概念和工作原理。然后,我们详细讨论了RTOS的任务管理、消息传递和同步机制,并根据实际情况分析了CMT液晶屏控制的需求。在此基础上,我们设

基于STM32的CMT液晶屏控制器驱动程序设计与优化

本文以STM32微控制器为基础,设计并优化了一个用于控制CMT液晶屏的驱动程序。在设计过程中,我们首先介绍了液晶屏的基本工作原理,包括CMT液晶屏的结构和信号传输机制。然后,我们详细讨论了STM32微控制器的GPIO、SPI和DMA模块的特性和使用方法,并结合实际情况分析了CMT液晶屏控制的需求。在此基础上,我们设计了一个具有良好可扩展性和稳定性的驱动程序,并对其进行了优化,以提高性能和降低资源占

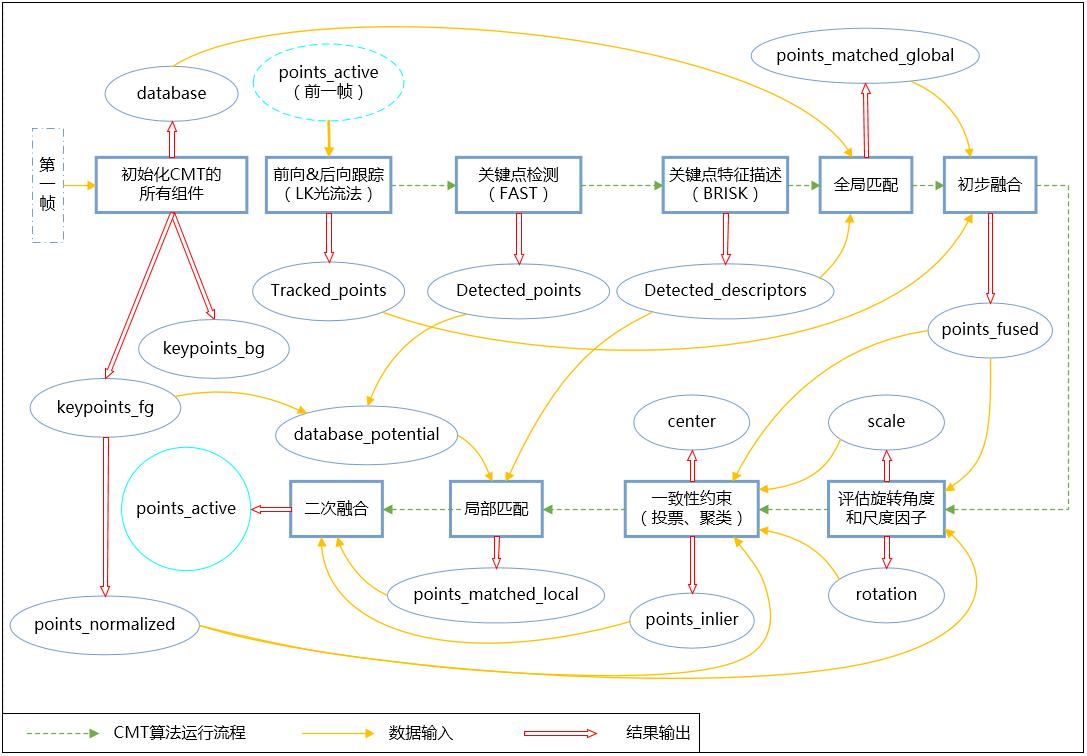

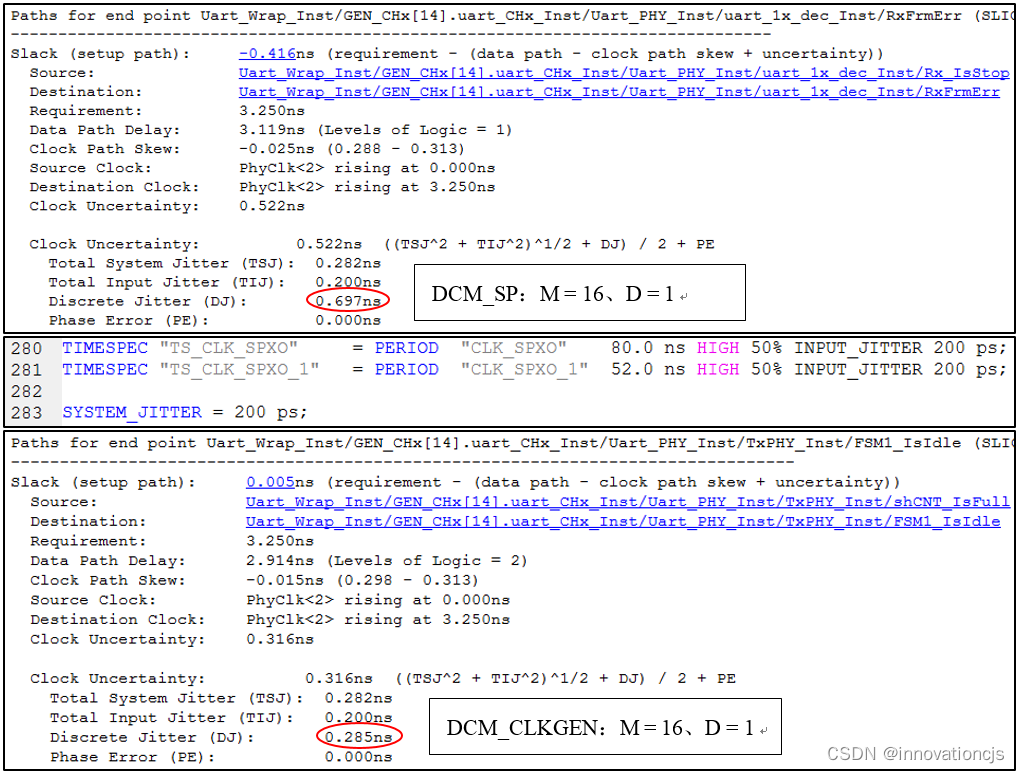

基于Xilinx CMT设计低抖动的高性能时钟

随着FPGA内部同步电路运行时钟频率的提高,时钟抖动将成为制约设计时序性能的显著因素。Xilinx FPGA提供高性能的时钟管理单元(CMT,Clock Management Tiles),可帮助设计者获得低抖动的FPGA内部运行时钟。 Xilinx对其各系列FPGA,均提供时钟资源的专用手册,本文不是手册的翻译,而是针对实际设计的一些对比测试,以加深对Xilinx FPGA CMT应用的理解。

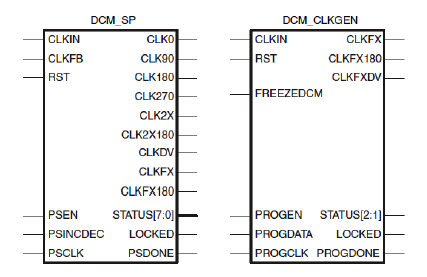

【FPGA】Spartan-6的时钟管理器(CMT)之数字时钟管理器(DCM)

目录 时钟管理器(CMT) DCM(digital clock manager) 组成结构 DCM原语 时钟管理器(CMT) Spartan-6 CMT是一个灵活、高性能的时钟管理模块。它位于芯片中央、垂直的全局时钟网络旁。如图2-17所示,它包含一个PLL和两个DCM。 图2-17 Spartan-6 FPGA CMT片内布局图 DCM(digit