本文主要是介绍Verilog实现一阶sigma_delta DAC,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一阶 sigma-delta 调制器类似于 PWM,但如果需要对其进行滤波,则具有更好的频率响应,因为它具有更高的频率输出内容。

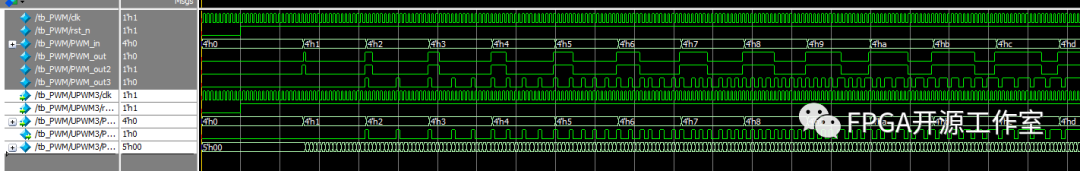

创建一阶 sigma-delta 调制器的最简单方法是使用硬件累加器……每次累加器溢出时,输出“1”。否则输出’0’。这在 FPGA 中很容易完成。

module PWM3(clk, rst_n,PWM_in, PWM_out);

input clk;

input rst_n;

input [3:0] PWM_in;

output PWM_out;reg [4:0] PWM_accumulator;

always @(posedge clk or negedge rst_n) if(!rst_n)PWM_accumulator <=0;elsePWM_accumulator <= PWM_accumulator[3:0] + PWM_in;assign PWM_out = PWM_accumulator[4];

endmodule

输入值越高,累加器溢出越快(“ PWM _ 累加器[4]”) ,输出“1”的频率越高。

这篇关于Verilog实现一阶sigma_delta DAC的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!