本文主要是介绍【紫光同创国产FPGA教程】——【PGL22G第九章】HDMI环路实验例程,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

适用于板卡型号:

紫光同创PGL22G开发平台(盘古22K)

一:盘古22K开发板(紫光同创PGL22G开发平台)简介

盘古22K开发板是基于紫光同创Logos系列PGL22G芯片设计的一款FPGA开发板,全面实现国产化方案,板载资源丰富,高容量、高带宽,外围接口丰富,不仅适用于高校教学,还可以用于实验项目、项目开发,一板多用,满足多方位的开发需求。

二:实验目的

HDMI输入接口采用宏晶微MS7200 HMDI接收芯片。芯片兼容HDMI1.4b及以下标准视频的3D传输格式,最高分辨率高达4K@30Hz,最高采样率达到300MHz,MS7200支持YUV和RGB之间的色彩空间转换,数字接口支持YUV及RGB格式输出。

MS7200的IIC配置接口与FPGA的IO相连,通过FPGA的编程来对芯片进行初始化和配置操作。MES22GP开发板上将MS7200的SA管脚下拉到地,故IIC的ID地址为0x56(详情可查看“MES22GP开发板硬件使用手册”)。

掌握HDMI接收芯片的配置及HDMI输出的实现。

三:实验原理

本实验实现的数据源和输出的分辨率及帧率均为:1280*720@60。

HMDI的Source端输入数据主要有像素点数据、行场同步、控制信号、辅助信号(音频)。显示器上一整幅画面由多个像素点组成,实际的显示过程是很快速的把显示器的各个像素点点亮。

显示时序标准

若下图表示一个5*5的画面,图中每个格子表示一个像素点,显示图像时像素点快速点亮的过程按表格中编号的顺序逐个点亮,从左到右,从上到下,按图中箭头方向的“Z”字形顺序.

以上图为例,每行 5 个像素点,每完成一行信号的传输,会转到下一行信号传输,直到完成第五行数据的传输,就完成了一个画面的数据传输了,一个画面也称为一场或一帧,显示每 1 / 6 秒中刷新的帧数称为帧率。比如 1920*1080P 像素,就是 1 行有效像素点 1920,一场有效行为1080行。

每个像素点的像素值数据,对应每个像素点的颜色。常见的像素值表示格式比如:RGB888,

RGB 分别代表:红 R,绿 G,蓝 B,888 是指 R、G、B 分别有 8bit,也就是 R、G、B 每一色光有

28=256 级阶调 , 通 过 RGB 三色光 的 不 同 组 合 , 一 个 像 素 上 最 多 可 显 示 24 位 的

256*256*256=16,777,216 色。

像素数据源源不断输送进来,行、场的切换通过行场同步信号来控制,即 hsync(行同步)和 vsync(场同步信号)。

上图中 Addressable 部分内容是在显示器中可看到的区域,像素点是否有效通过 DE 信号标识;Border 可理解为显示黑边或者显示边框,通常 Border 显示的像素值是 0(黑色)。行、场切换过程都是在用户感受不到的区域进行的,这个区域就是 Blanking 部分,称为消隐区间。同步信号上升沿表示新的一行/一场开始,Hsync 对应行,Vsync 对应场。

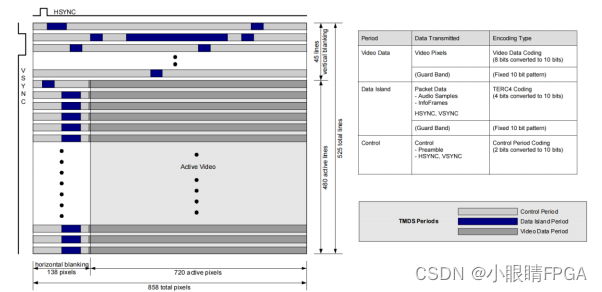

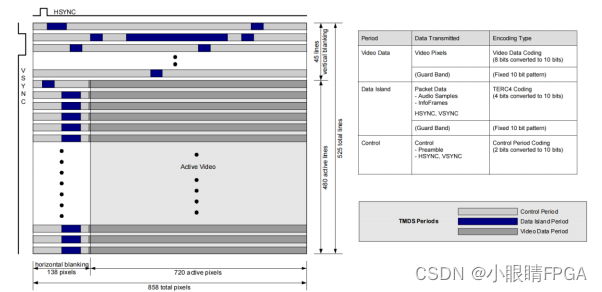

下图是 HDMI 显示的 720X480 分辨率的 TMDS 编码帧结构。

本实验只考虑 video 信号的传输,实现图像的 TMDS 编码时只需要 Video data Period 和 control period。

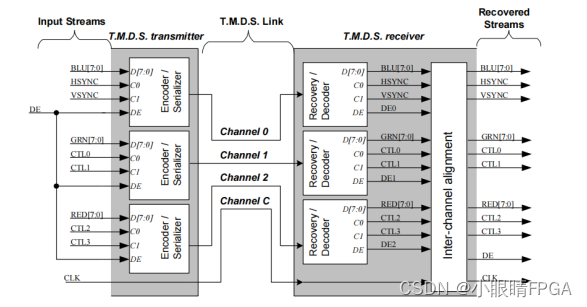

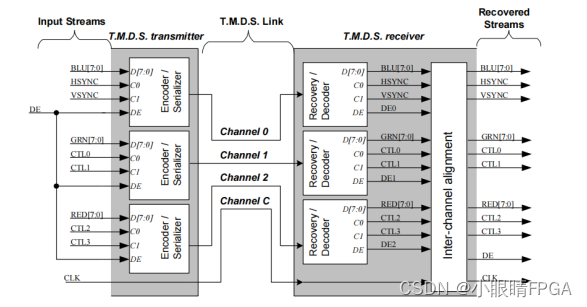

完整的信号链路如下:

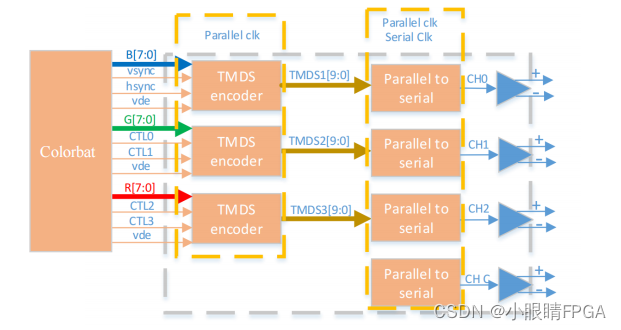

每个 channel 链路如下:

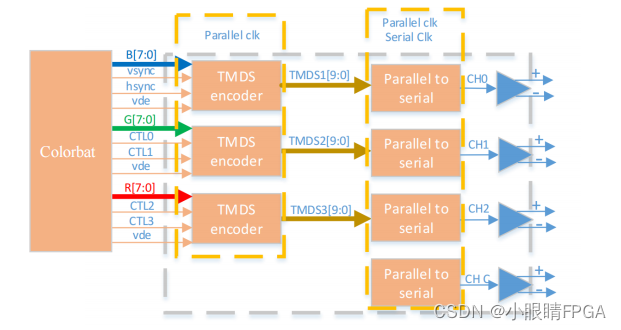

TMDS 编码

TMDS 的编码会把 D[7:0]或 C[1:0]编码成 10bit 的数据,编码的目的是为了是 TMDS 在传输过程中维持直流平衡,也就是说传输的 0 和 1 的数量保持基本一致。下图是 TMDS 编码的流程图。

四:实验源码

实验源码详见参考例程。

五:实验现象

开发板的 HDMI 输入接口连接电脑端 HDMI 输出接口,开发板的 HDMI 输出接口连接一个HDMI 的屏幕。然后将显示器 2(即 HDMI 的屏幕)的实际分辨率改为 1280*720@60,下载程序,便可以看到 HDMI 屏幕显示与电脑桌面一致的图像。

下图为电脑端设置分辨率步骤

HDMI 屏幕显示图像示意:

这篇关于【紫光同创国产FPGA教程】——【PGL22G第九章】HDMI环路实验例程的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!