本文主要是介绍【CPLD Verilog】WARNING - IO buffer missing for top level port,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在编写的一个监控风扇板的TACH信号的程序中

module FanTachMonitor (input sys_clk

,input auxgood

,input [31:0] fan_count_num // fan_count_num * 20ns = fan_time

,input fan_tach

,output reg [15:0] fan_rps

);综合之后报了一组warning

WARNING - IO buffer missing for top level port i_CPLD_FAN1_TACH0...logic will be discarded.

WARNING - IO buffer missing for top level port i_CPLD_FAN1_TACH1...logic will be discarded.

WARNING - IO buffer missing for top level port i_CPLD_FAN2_TACH0...logic will be discarded.

WARNING - IO buffer missing for top level port i_CPLD_FAN2_TACH1...logic will be discarded.

WARNING - IO buffer missing for top level port i_CPLD_FAN3_TACH0...logic will be discarded.

WARNING - IO buffer missing for top level port i_CPLD_FAN3_TACH1...logic will be discarded

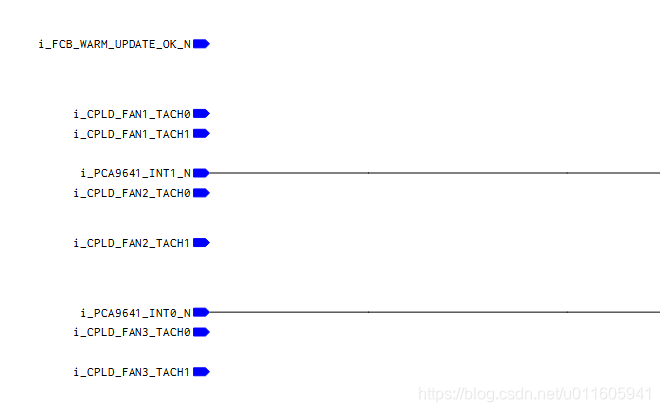

从网上搜了一下这个warning,发现了一个案例是说这个warning是综合器在综合的时候将部分net优化掉了。通过RTL发现相关的net根本没有连到任何模块,实际上整个FanTachMonitor都没有被综合!

相应的检查FanTachMonitor的输出端口,发现本应输出给RAM模块的信号,在RAM中只是接了一个0的常数寄存器。

回到程序中,检查发现在顶层模块存在这样的一组语句:

wire [15:0] w_CPLD_FAN1_RPS0=16'b0; //mean round per second

wire [15:0] w_CPLD_FAN1_RPS1=16'b0;

wire [15:0] w_CPLD_FAN2_RPS0=16'b0;

wire [15:0] w_CPLD_FAN2_RPS1=16'b0;

wire [15:0] w_CPLD_FAN3_RPS0=16'b0;

wire [15:0] w_CPLD_FAN3_RPS1=16'b0;猜测是否是这里将wire型的变量的“赋初始值”的动作,导致综合器在综合的时候认为这里的wire型变量和常数寄存器相连,从而综合器在优化时认为,FanTachMonitor这个模块无法输出任何东西(输出的wire锁死为常数),因此将整个FanTachMonitor给优化掉了。

将上面的代码中的赋值动作去掉后,RTL正确生成的该部分的电路,并且warning也消除了。

总结:

(1)wire型变量别乱赋初始值;

(2)综合器有时候会优化掉一些模块,但是这种情况会被认为是warning,而不是error,有可能出错。

这篇关于【CPLD Verilog】WARNING - IO buffer missing for top level port的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!