本文主要是介绍FPGA与ASIC有什么差异?二者该如何选用?,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前言

对于一个数字电路的新手来说,这可能是会经常遇到的一个问题:FPGA和ASIC之间的区别是什么?

接下来本文将尝试讲解 “什么是FPGA?” 和 “什么是ASIC?”,然后讲述一些关于FPGA和ASIC的问题,例如它们之间的异同。我们将总结二者的优点和缺点,以便您能够根据应用需求来做出一个明智的选择。

什么是FPGA?

FPGA是指现场可编程门阵列(Field Programmable Gate Array)。它是一个可以现场编程的、并按照预定设计意图来工作的集成电路。这意味着它可以既作为一个微处理器工作,也可以作为一个加密单元工作,还可以作为一张显卡来工作,它甚至可以同时具备这三者的功能。顾名思义,FPGA是可编程的,因此我们可以对作为以微处理器模式工作的FPGA重新编程,使其在工作现场(不需要去半导体工厂)就可以在功能上变成一张显卡。在FPGA上运行的设计通常使用诸如VHDL和Verilog等硬件描述语言(HDL)构造。

FPGA由成千上万个可配置逻辑块(Configurable Logic Blocks ,CLB)组成,这些CLB嵌在可编程互联结构中。CLB主要由查找表(Look-Up Table,LUT)、多路复用器(Multiplexer)和触发器(Flip-Flop)构成。它们可以用来实现复杂的逻辑功能。除了CLB和布线(routing interconnect)之外,许多类型的FPGA还包括某些专用的硬件资源,例如BRAM、DSP、外部存储控制器(External Memory Controllers)、PLL、吉比特收发器(Gigabit Transceiver)等。最近的一个趋势是在同一个FPGA中嵌入一个处理器硬核(例如Xilinx Zynq系列中的ARM Cortex A9)。这样处理器可以处理普通的、非关键的任务,而FPGA则可以实现高硬件加速(high-speed acceleration),仅仅用处理器的话,这是无法做到的。这些专用硬核在与ASIC的竞争中至关重要。

什么是ASIC?

ASIC是指应用专用集成电路(Application Specific Integrated Circuit,ASIC)。顾名思义,ASIC是专用的。它们是专为某个(些)目的而设计的,在其整个生命周期内,它们的功能是固定不变的。比如你手机里的CPU也是ASIC,在它的整个生命周期内,它都是作为一个CPU来工作的,它的逻辑功能无法被改变,因为它的数字电路是由恒定连接的门电路和触发器所构成的。ASIC的逻辑功能使用如Viilog或VHDL等硬件描述语言来实现。

与FPGA不同的是,ASIC中所生成的电路被直接固定了,而FPGA中的电路则是通过连接多个CLB来灵活实现的。FPGA类似于用乐高积木来拼一个城堡,而ASIC则像是用钢筋混凝土来浇筑一个城堡。当你需要的时候,你可以把FPGA城堡拆了,再重新用这些乐高积木拼一辆汽车;但你却无法把钢筋混凝土重新浇筑成一辆汽车了。

FPGA与ASIC的比较

| 序号 | FPGA | ASIC |

| 1 | 可重构电路。FPGA可通过不同的设计重新配置。甚至在芯片的某一部分处于工作状态时,也能对另一部分进行重配置(部分重配置)。这一功能在数据中心的加速计算中得到了广泛应用。 | 固定电路。一旦设计被转换成实体电路,就无法改变了。该电路在其生命周期内将一直处于同一功能模式. |

| 2 | 设计通常使用硬件描述语言(hdl)生成,如VHDL或Verilog。 | 与FPGA一致。 |

| 3 | 低门槛。 | 成本、学习曲线、与半导体工厂联系等方面的门槛很高。 |

| 4 | 不适合大规模生产 | 适合大规模生产 |

| 5 | 功耗高 | 功耗低 |

| 6 | 与类似工艺节点的ASIC相比,工作频率有限。布线路由逻辑和可配置逻辑会吞噬时序裕量。 | 利用相同的工艺节点制作的ASIC,其工作频率远高于FPGA。 |

| 7 | 无法进行模拟设计。虽然FPGA可能包含某些模拟电路的硬核,如PLL和ADC等,但它们并不能灵活地来创建如射频收发器等模拟电路。 | 可以有完整的模拟电路,例如Wi-Fi收发器等。这是FPGA所不具备的优势。 |

| 8 | FPGA非常适合雷达、手机基站等应用,目前的设计可能需要升级,以便使用更好的算法或更好的设计。在这些应用中,FPGA高昂的成本并不是决定性因素,它的可编程特性才是决定因素。 | ASIC不适合在可能需要经常更新设计的应用领域。 |

| 9 | 最好用于原型验证和验证设计。很多ASIC都使用FPGA来做原型验证。一些大的处理器厂商也在使用FPGA来验证他们的片上芯片(SOC)。 | 不建议使用ASIC来做原型设计,除非它是绝对有效的。一旦流片后,几乎就没有办法来修复设计错误了(流片失败成本巨大)。 |

| 10 | FPGA设计师通常不需要管后端设计。所有的事情都由综合工具来处理,这些工具会确保设计如RTL代码所描述的那样,并确保其满足时序要求。因此,设计师可以专注于完成RTL的设计。 | 从RTL向下到复位树、时钟树、物理布局和布线、工艺节点、制造约束(DFM)、测试约束(DFT)等,ASIC设计师都需要关注。一般而言,上述每个领域都由不同的工程师负责。 |

FPGA与ASIC的成本分析

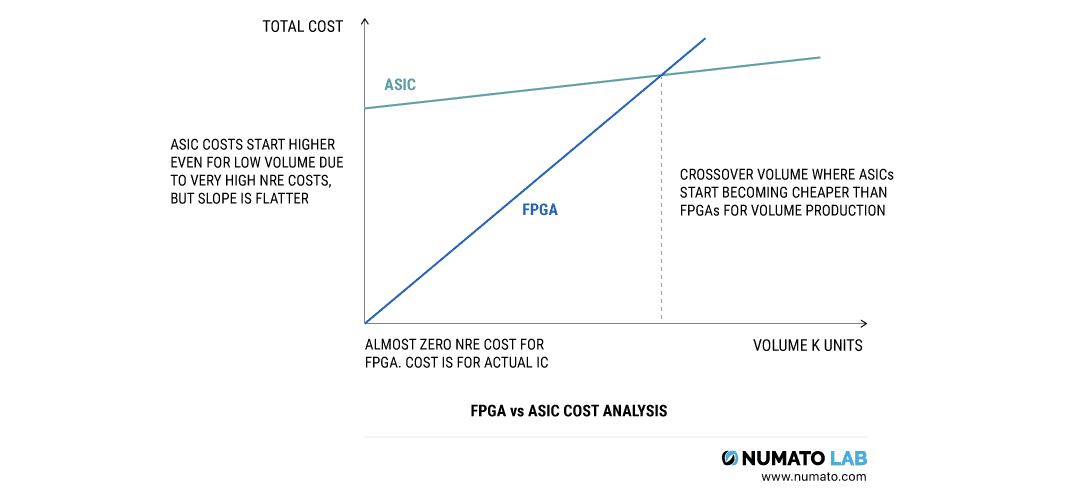

ASIC和FPGA的成本分析图如上。成本和单位值在图表中被省略了,因为它们与所用的工艺技术和时间有所不同。ASIC的NRE成本高达数百万美元,而实际的每一个die成本可能只有几美分。FPGA没有NRE成本,成本的大部分来源于软件(知识产权)。因为NRE成本的存在,ASIC的总成本在一开始就非常高,但其成本斜率较低。也就是说,小规模的ASIC的成本很高,但在大规模的ASIC中,每个批量的成本将变得非常低。

以下是ASIC成本构成主要部分:

- ASIC 的EDA工具和培训

- 设计费用

- DFT费用

- 仿真费用

- 掩膜成本

- 晶圆成本

- 晶圆加工

- Die Utilization

- 生产和制造损失

- 封装

与ASIC相比,FPGA的成本仅限于购买现成的IC。

如何在FPGA或ASIC之间进行选择

你是一个想学习更多关于数字电路和硬件设计内容的新手?那么FPGA和仿真软件最适合您。你在设计自己的产品吗?酷!请问问自己目标市场是什么,预期的价格是多少,功率预算是多少,速度要求等问题。能用FPGA实现吗?如果是的话,那就继续把你的想法实现。如果不能,那你可能只好用ASIC了。在大多数情况下,至少可以使用FPGA制作原型并验证您的想法。当你完成原型的时候,你自己就会知道你是否需要使用ASIC。当然,如果您的设计完全是突破性的,并且非常特殊,有着非常具体的要求(在成本、功率、速度等方面),那么您除了使用ASIC外别无选择。FPGA可以满足大多数的应用情况,特别是当您需要可以重新配置电路时。

参考

《FPGA Vs ASIC: Differences Between Them And Which One To Use?》

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

这篇关于FPGA与ASIC有什么差异?二者该如何选用?的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!