asic专题

数字芯片设计验证经验分享系列文章(第四部分):将ASIC IP核移植到FPGA上——如何测试IP核的功能和考虑纯电路以外的其他因素

作者:Philipp Jacobsohn,SmartDV首席应用工程师 Sunil Kumar,SmartDV FPGA设计总监 本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用IP核来开发ASIC原型项目时,必须认真考虑的一些问题。文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考

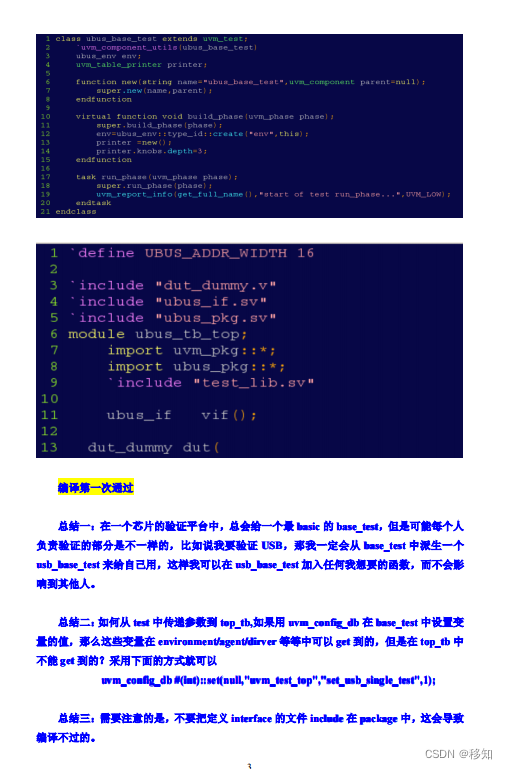

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

在集成电路设计的复杂世界中,验证环节是确保设计满足预期功能和性能要求的关键步骤。随着系统级芯片(SOC)和特定应用集成电路(ASIC)的规模和复杂性不断增加,传统的验证方法已经难以满足高效、准确的验证需求。因此,采用先进的验证方法学和工具变得尤为重要。 SystemVerilog(SV)和通用验证方法学(UVM)作为当前硬件验证领域的两大支柱,提供了一套完整的框架和工具,用于构建可扩展、可重用的

图像处理ASIC设计方法 笔记25 红外成像技术:未来视觉的革命

在当今科技飞速发展的时代,红外成像技术以其独特的优势,在医疗、工业检测等多个领域扮演着越来越重要的角色。本章节(P146 第7章红外焦平面非均匀性校正SoC)将深入探讨红外成像系统中的关键技术——非均匀性校正SoC,以及它如何推动红外成像技术迈向新的高度。 红外成像系统:视觉的延伸 红外成像系统,简而言之,就是利用红外焦平面阵列(IRFPA)捕捉并转换红外辐射,形成图像的技术。这一技术的核心

图像处理ASIC设计方法 笔记21 标记ASIC的顶层状态机

目录 (一)标记ASIC的工作流程1 ASIC首先从控制寄存器内读出待标记图像的基本参数2若写入了有效的启动命令,则进入下面一帧图像的标记过程。3 ASIC通过接口模块从FIFO1中读取待标记的图像4一帧图像初步标记完成后进行等价表的整理压缩5从临时标记存储器中读取临时标记送入标记代换及特征值统计流水线 (二)设计标记ASIC的主要寄存器 学这一章节,为的是学如何设计一个A

图像处理ASIC设计方法 笔记20 标记ASIC系统设计

目录 (一)如何考虑标记ASIC中的图像存储器设计1 片内还是片外存储器2 片内存储器具体怎么实现 (二)特征值存储1 特征值包括2 采用流水线方式统计特征值 本文是阅读6.4节的笔记和感悟,6.4节整体讲的是标记ASIC的系统设计,我理解有两个要点:对于图像存储器的考虑,特征值包括哪些以及如何存储。 (一)如何考虑标记ASIC中的图像存储器设计 1 片内还是片外存储

图像处理ASIC设计方法 笔记19 连通域标记ASIC系统设计

目录 核心的模块有:标记ASIC的工作流程如下:该芯片的系统结构具有如下特点: P131 第6章 连通域标记与轮廓跟踪 本章节讲述了多值分割图像连通域标记芯片的系统设计 多值分割图像连通域标记芯片(以下简称"标记芯片",也称"标记 ASIC"),完成图像连通域标记和图像连通域特征值提取的两大功能。 核心的模块有: 顶层模块、时钟复位模块、存储器模块(控制寄存器、FIFO1、

Verilog基础知识5(ASIC设计中各个阶段的关键问题汇总)

需求说明:Verilog设计 内容 :ASIC设计关键问题 来自 :时间的诗 原文:http://blog.sina.com.cn/s/blog_629d62b60100u42r.html ASIC的复杂性不断提高,同时工艺在不断地改进,如何在较短的时间内开发一个稳定的可重用的ASIC芯片的设计,并且一次性流片成功,这需要一个成熟的ASIC的设计

谈谈IC、ASIC、SoC、MPU、MCU、CPU、GPU、DSP、FPGA、CPLD的简介

谈谈IC、ASIC、SoC、MPU、MCU、CPU、GPU、DSP、FPGA、CPLD的简介 IC (Integrated Circuit) 集成电路 (Integrated Circuit, IC) 是一种把电路中的元器件如电阻、电容、晶体管等集成在一块半导体材料上的微型电子器件。它是现代电子系统的基础组件,按照功能可分为模拟IC、数字IC、混合信号IC等多种类型。 ASIC (App

图像处理ASIC设计方法 笔记10 插值算法的流水线架构

(一) 三次插值算法实现的图像旋转设计的流水线架构 传统上,三次插值算法实现的图像旋转设计需要三块一样的处理资源,为了节约资源,采用流水线设计,简单来讲就是三次插值算法共用一块资源,优化这部分使用的存储器结构,以达成流水线的目标。 插值算法最直接的是需要DFF模块,现在对它进行适应流水线的改造。针对三级插值,有三个不同的设计,第一级用DFF,第二级是DFF加上延迟线,第三次是去掉行缓存、改

CPU、GPU、IPU、NPU、TPU、LPU、MCU、MPU、SOC、DSP、FPGA、ASIC、GPP、ECU、

CPU: 中央处理器(Central Processing Unit)是一块超大规模的集成电路,是一台计算机的运算核心(Core)和控制核心( Control Unit)。 它的功能主要是解释计算机指令以及处理计算机软件中的数据。 中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Data)

图像处理ASIC设计方法 笔记8 卷积计算芯片的结构

(一) P81 卷积芯片内部模板框图 该设计有两个数据通路:图像数据和模板数据。 图像数据是经过帧控制、实时图SPRAM(写控制、 SPRAM读控制、数据读控制)、计算单元; 模板数据是经过模板SPRAM、计算单元。 4.5.4运算单元像素寄存器控制 存储SPRAM写入的64bit数据,输出为8bit。它是属于图像数据的路径。 当处于读操作时,输出的读使能信号fifo_rd_en ,

图像处理ASIC设计方法 笔记7 图像存储SPRAM控制

(一)图像存储SPRAM控制 P83 模块三 图像存储SPRAM控制 输入的图像要存放在这个模块中。这个SPRAM的数据组织和读/写控制是设计的重点之一。 SPRAM是多个块的形式。用的是单端口RAM,采用分时读或者写(读写不同时),起到双端口的效果。应该用的是单端口RAM(Single-port RAM),输入只有一组数据线和一组地址线,读写共用地址线,输出只有一个端口。 可以分时

图像处理ASIC设计方法 笔记6 数据拼接和帧格式校正

第四章大模板卷积ASIC设计方案 P80 实时图SPRM 数据位宽64bit,4个SPRAM,同时得到4行数据 绘制卷积芯片数据路径图,卷积芯片内部模块图 根据这个图,本书后续对各个模块都进行介绍。 P81 第一个模块 图像输入前端FIFO 学习图像处理中好的设计思路:帧格式校验和数据拼接 实现方式见下: (1)帧格式校验 当从前端FIFO中读取数据,检测到帧起始信号有效时,开始计

图像处理ASIC设计方法 笔记5 图像卷积器硬件结构

图像处理ASIC设计方法: 第三章时序问题和解决方法 P71 异步复位信号处理 倘若复位信号撤销时刻发生在时钟上跳沿附近,则触发器输出端进入亚稳态,这成为复位撤销冒险。防止复位撤销冒险,两个措施,一是异步复位同步器,二是使用合理的复位信号驱动网络。 复位信号驱动树的延时控制在物理设计阶段完成,前端设计师可以不考虑。 异步复位在进入同步电路之前,还需要进行毛刺过滤。毛刺过滤是延时电路,一

asic设计中的插件使用。

推荐安装SVE,是一个eclipse的版本,在这个基础上安装veditor和perl 1,verilog和VHDL的编辑器 veditor clipse Verilog editor is a plugin for the Eclipse IDE. It provides Verilog(IEEE-1364) and VHDL language specific code viewer,

ASIC的一些技巧和软件

zz : http://bbs.eetop.cn/thread-138262-1-1.html 安装全套Synopsys软件--关于操作系统的选择 操作系统的选择很重要,我试过了ubuntu7.10,8.04,都或多或少有问题,RedHat9,AS3,SuSe10.2,CentOS4.6,CentOS5.2都有问题,总之不能全部安装,最后我用了RedHat AS 4,成功,所有Sy

图像处理ASIC设计方法 笔记4 异步FIFO

P66 异步FIFO 这段对FIFO的描述很精彩: 理解了水位信号的含义(相当于通常所说的满/空标志,注意读时钟域的空信号,写时钟域的满信号,只能在它各自的时钟域直接使用,如果要在另一时钟域用,需要使用同步器) FIFO可以理解为一个传输数据的管道,写入一方顺序将数据压入管道的一端,读出一方从管道的另一端按照写入的顺序依次取出数据(所以叫先进先出)。 由于进行顺序读写,FIFO不需要地

图像处理ASIC设计方法 笔记3 跨时钟域处理思想

P43第二章 数据路径并行策略 全并行、全串行、半并行 P47 第三章 时序问题和解决方法 锁存器的时序分析,工具做不到,需要设计者手工分析 存储器中SRAM可以直接做到ASIC里面(CMOS工艺)而DRAM不行 P55 作者是不是把sensor翻译成 成像器 成像器向ASIC输入被处理数据 片外异步SRAM写操作波形 图3.14在P54, 解释在P58,双向驱动总线,所以DATAI

图像处理ASIC设计方法 笔记1 硬件加速

这本书是图像处理方面ASIC与DSP比较,讲了为什么要用ASIC做图像处理,它的特点和适用场景。 (一) 适用ASIC的应用场景:体积是第一位考虑的要素 还有功耗。 P25 选择用硬件加速的三个问题 1 算法有高并行性吗? 2 算法实现的硬件开销能承受吗? 3 与软件编程相比,使用硬件能获得多少加速比? 解释1 这个算法每一次搜索都必须依赖前一次搜索的结果,不能并行,就不能用硬件加速 还要

ASIC到底是什么?

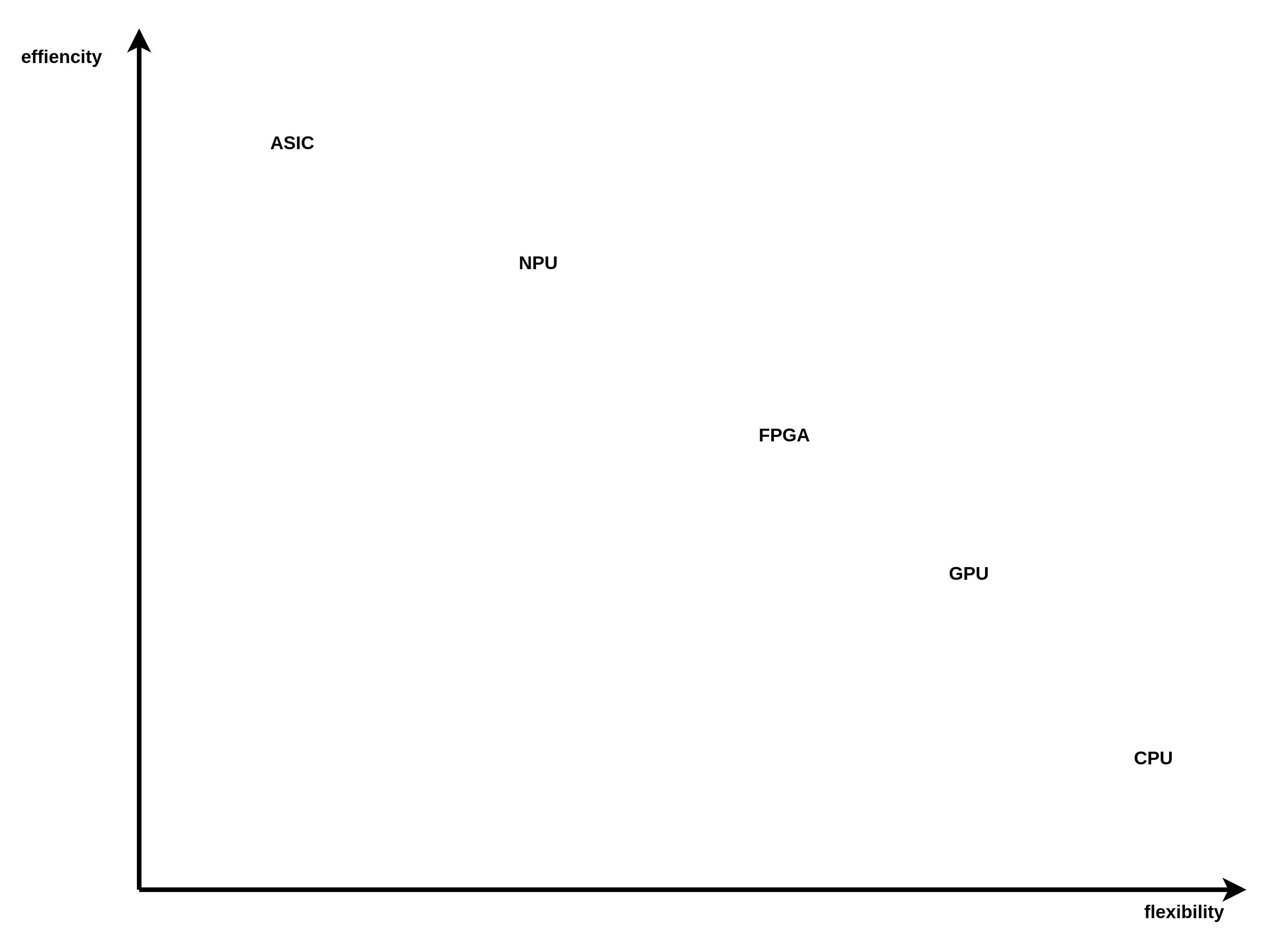

ASIC(Application-Specific Integrated Circuit,特定应用集成电路)是一种定制的、专门为特定应用设计的集成电路。与通用处理器(如CPU和GPU)不同,ASIC 被定制为执行特定任务或应用,通常以高度优化的方式执行特定的计算操作。ASIC 的设计旨在提供最佳性能和效率,因为它专门用于执行一种或几种紧密相关的任务。 在与CPU、GPU和NPU的比较中,ASIC

智原FPGA-to-ASIC方案加速客户人工智能芯片技术革新

台湾新竹 -- (美国商业资讯) -- ASIC设计服务暨IP研发销售厂商智原科技﹝FaradayTechnology Corporation,TWSE:3035﹞今日宣布其FPGA-to-ASIC解决方案已成功完成多项人工智能相关的ASIC项目,如无人机图像识别、医疗图像分析、智能家电与3D感应等应用,提供了更优越的功耗与性能表现,同时降低整体系统成本。 智原的FPGA-to-ASIC方

智原 ASIC 提供工业级后援服务 加速工厂自动化应用

ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)今日宣布已成功交付多项工厂自动化相关的ASIC设计案,这些项目主要应用在工业物联网(IIoT)领域。这些设计包含工业机器人、可编程控制器(PLC processor)、工厂自动化的控制器与网通等应用,采用8吋及12吋工艺技术,并提供客户工业级的功能可靠度与长期供货承诺。

深度学习硬件(GPU、FPGA、ASIC、DSP)

深度学习最近取得的成功势不可挡:从图像分类和语音识别到图片标注、理解视觉场景、视频概述、语言翻译、绘画,甚至是生成图像、语音、声音和音乐! 随着我们的家变得越来越智能,你会发现许多设备都会需要连续地使用深度学习应用、收集和处理数据。 所以我们需要新的硬件,一个比 Intel Xeon 所驱动的服务器更加高效的硬件。一个英特尔服务器 CPU 可能会消耗 100-150 瓦功率并需要一个有着冷却装置

ASIC设计中各个阶段需要注意的问题

ASIC设计中各个阶段需要注意的问题 ASIC的复杂性不断提高,同时工艺在不断地改进,如何在较短的时间内开发一个稳定的可重用的ASIC芯片的设计,并且一次性流片成功,这需要一个成熟的ASIC的设计方法和开发流程。本文结合NCverilog,DesignCompile,Astro等ASIC设计所用到的EDA软件,从工艺独立性、系统的稳定性、复杂性的角度对比各种ASIC的设计方法,介绍了在编码

适用于异构芯片(CPU,ASIC,DSP,FPGA,GPU/GPGPU)的软件并行技术

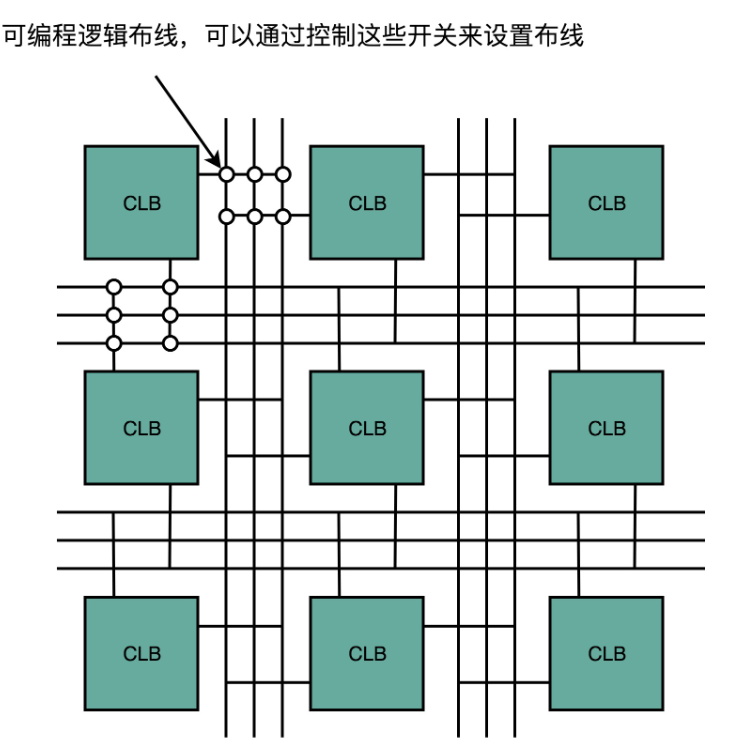

近些年,CPU等通用处理器的性能提升速度放缓,为了继续满足各行各业对高能效计算日益增长的需求,以FPGA,GPU,DSP,NPU等为代表的异构算例,一夜之间在众多的新型热点领域受到广泛关注。 首先结合市面上能够看到的具体的产品来分析这些异构核之间的差异。 多元化算力 除了上述比较通用的命名,还有一些公司为了强调某些方面的差异性,提出了不同的命名,比如VIP的PPU(Parallel