本文主要是介绍FPGA PCIE软核 IP,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

我们日常项目中,使用的PCIE其实大部分是硬核,硬核是有很多电路直接由模拟电路实现了

但是硬核资源有限,有时可能遇到一些本身想用2个PCIE IP 但是可能器件本身只有一个硬核,此时可以考虑PCIE软核实现,我们可以注意到PCIE其实本质还是占用高速串行口,查看器件资源我们可以看到GTX 这类接口是一定会大于PCIE硬核数目的,此外硬核支持的速率受器件限制死了,比如K7系列的器件,最高支持的是PCIE2.0,但是我们可以注意到GTX实际是可以支持10G的线速率,没错,通过PCIE软核是可以再K7器件上实现PCIE3.0的

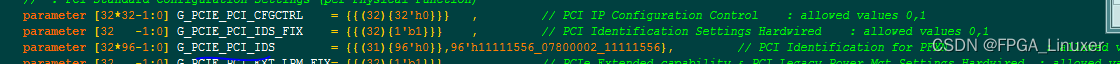

IP只需要搭载器件的transcerver IP即可实现PCIE 软核IP

支持ENDPOINT 及ROOT模式,可用于NVME存储,扩展硬盘数量,从而提高带宽

PS:作为ENDPOINT时,用windriver扫描硬件

这篇关于FPGA PCIE软核 IP的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!