软核专题

Xilinx FPGA软核开发流程

Xilinx FPGA软核开发流程 环境说明 Vivado 2017.4 芯片 XC7K325 以下步骤只列提纲,后面有时间会增加图文具体操作步骤,欢迎大家讨论 具体步骤 创建vivado工程放置模块自动连线生成Block Design综合实现添加引脚分配生成bit流导出硬件Launch SD编写软核程序编译调试通过回到Vivado添加elf重新生成bit流生成mcs固化

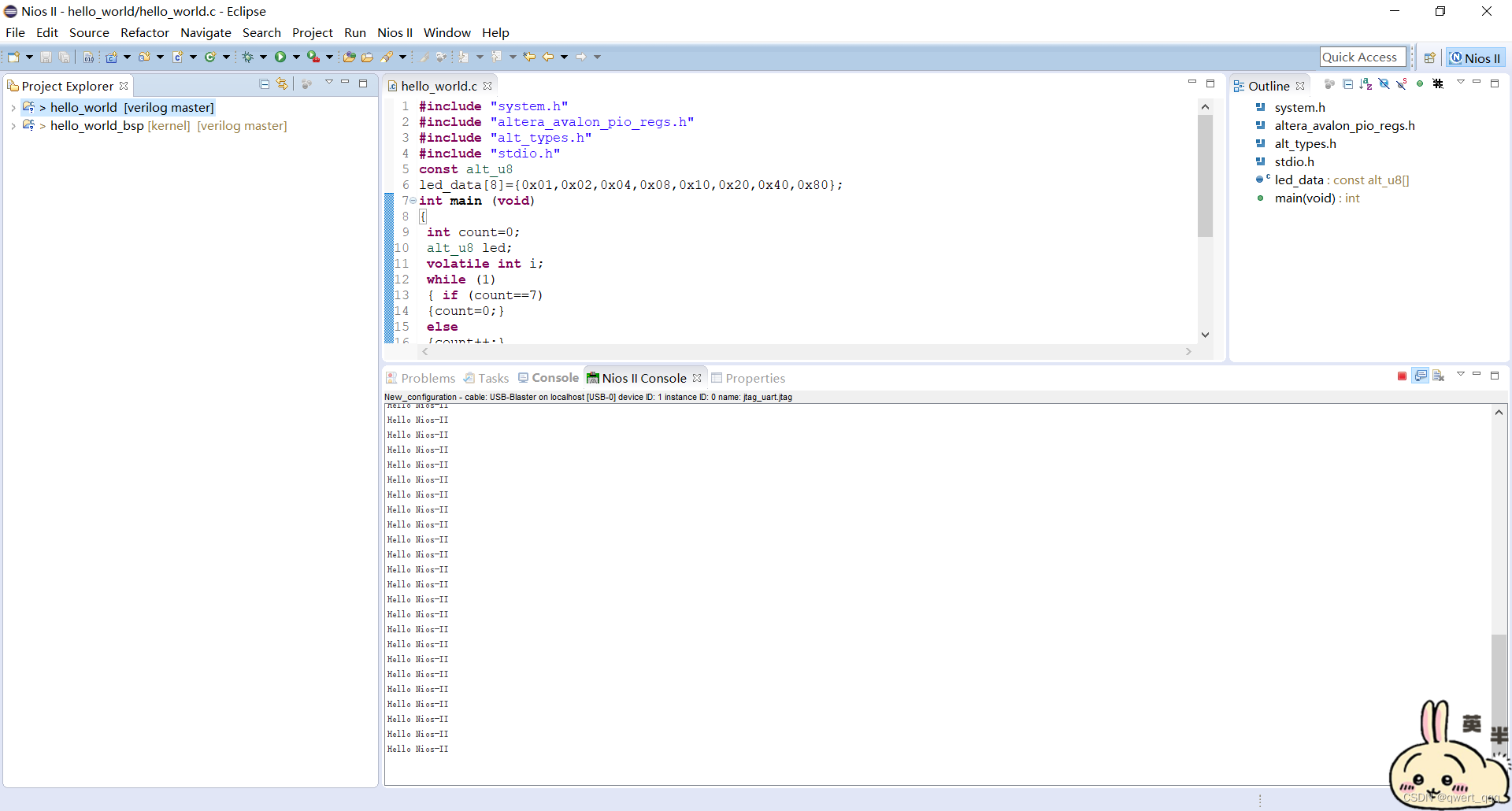

基于NIOS-II软核流水灯和串口通信实现

文章目录 一、创建工程二、系统设计1. 在 “component library” 标签栏中找到 “Nios II Processor” 后点击 Add2. 在 ”Component Library” 标签栏中的查找窗口输入 jtag 找到 ”JTAG UART ”,然后点击 Add3. 添加片上存储器 On-Chip Memory(RAM)核4. 查找窗口输入 pio 找到 ”PIO” 后

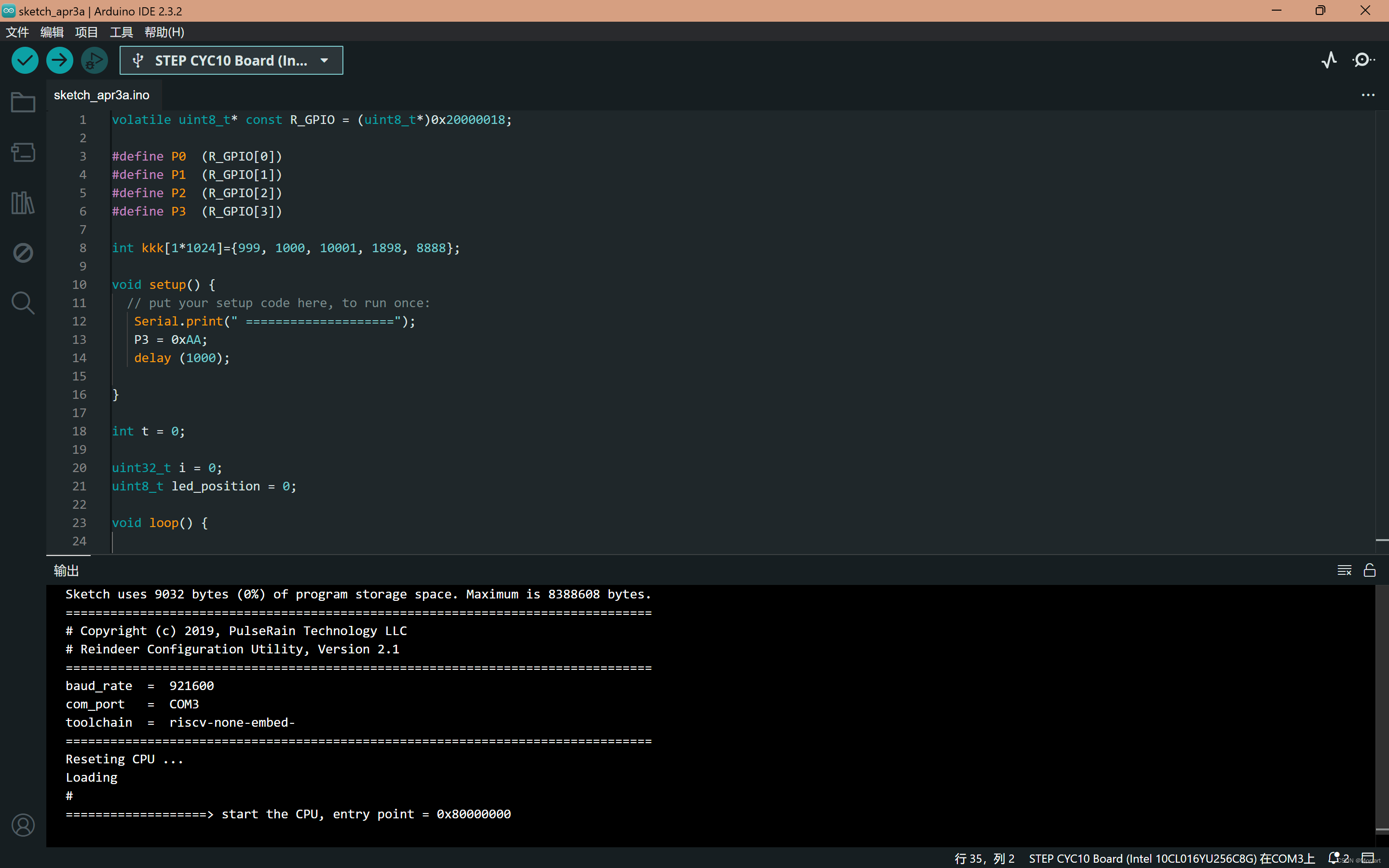

【ArduinoQuartus】在小脚丫STEP CYC10上安装PulseRain Reindeer并在软核上运行基础功能

【Arduino&Quartus】在小脚丫STEP CYC10上安装PulseRain Reindeer并在软核上运行基础功能 一、将Reindeer软核下载到STEP CYC10(一)下载PulseRain Reindeer软核(二)配置Reindeer软核到开发板1.将sof文件转换为jic文件2.将jic文件下载到FPGA中 二、Arduino编写流水灯并下载到开发板中运行(一)Ar

14、zedboard 7020 编译Opencv3.4+Opencv_contrib3.4+DeepSort(软核)

基本问题描述:因为希望使用opencv 附加库的DNN 模块,搞一下深度学习的内容,因为上一篇博客已经自己制作了一个debain系统在zynq7020上,因此在该系统上编译opencv3.4 上,编译过程如下: 1、安装附加库 sudo apt-get install build-essential cmake git pkg-configsudo apt-get install libjp

调试(debug)的底层硬件逻辑——通过FPGA嵌入式软核

以前在vs等上调试代码,查看变量或者内存的值没有去深究调试时底层的硬件的逻辑。看了赛灵思给的microblaze的手册,对于debug的底层硬件逻辑有了了解。 若想在SDK中使用调试模块,在基于FPGA的嵌入式硬件设计(如在赛灵思的vivado中使用block design设计)时,需要添加一个debug的硬件模块——ILA。ILA连接想要在调试时,触发信号到来时,抓取的引脚。 这样当你在CP

PCIe 3.0软核控制器,具备AXI接口和DMA功能

PCIe-AXI-Controller PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,实现PCIe PHY Layer,Data Link Layer以及Transaction Layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方

IP软核、硬核以及固核的概念与比较

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力体现。对于FPGA开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。目前,IP核已经变成系统设计的基本单元

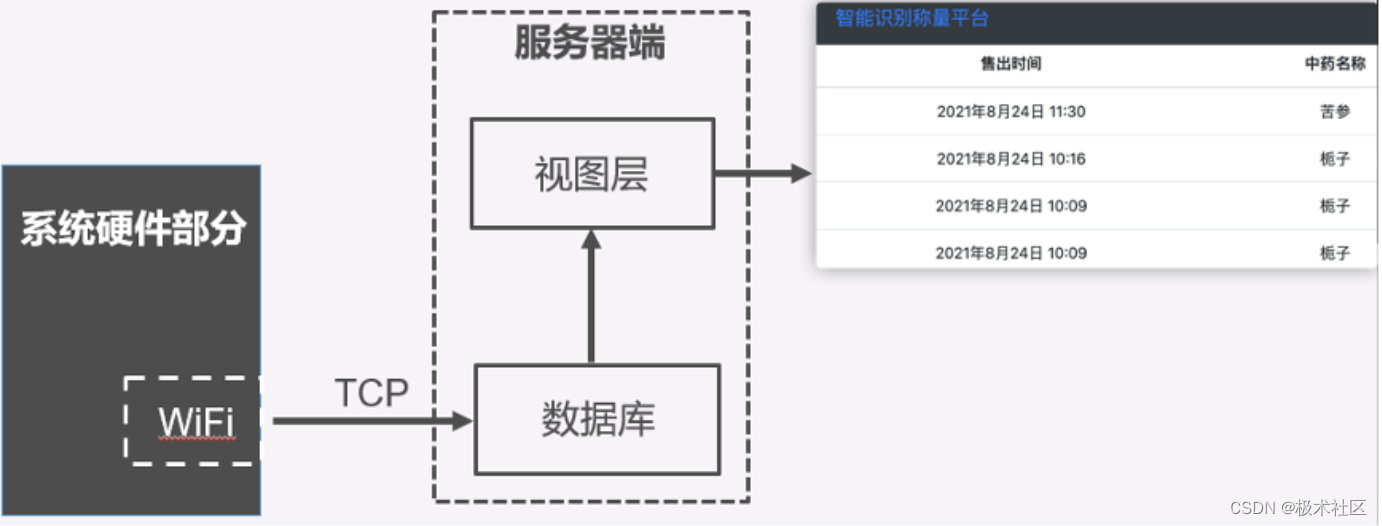

【2021集创赛】Diligent杯一等奖:基于Cortex-M3软核的智能识别称量平台

本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。 杯赛题目:Diligent杯:基于FPGA开源软核的硬件加速智能平台 参赛组别:A组 设计任务: 利用业界主流软核处理器(仅限于Cortex-M系列及 RISC-V系列)在限定的DIGILENT官方FPGA平台上构建SoC片上系统,在 SoC中添加面向智能应用的硬件加速器(如从最简单的矩阵乘加加速到更复

在FPGA上搭建Cortex-m3软核

在FPGA上搭建Cortex-m3软核 前言 说是在fpga上搭建,其实还是比较偷懒了,在Vivado上进行搭建,比较方便。先来讲讲Cortex-m3这个东西,玩过单片机的人应该都用过Stm32f103c8t6这块板子,里面的核心架构就是Cortex-m3,c8t6这个器件是基于m3内核组成一块芯片。由于自己需要做一个加密解密的soc,所以需要先搭建一个m3的软核,后续在软核基础上把做好的

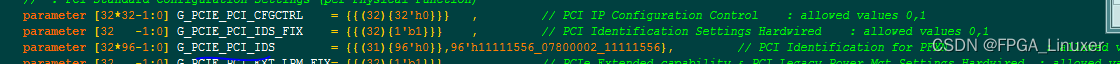

FPGA PCIE软核 IP

我们日常项目中,使用的PCIE其实大部分是硬核,硬核是有很多电路直接由模拟电路实现了 但是硬核资源有限,有时可能遇到一些本身想用2个PCIE IP 但是可能器件本身只有一个硬核,此时可以考虑PCIE软核实现,我们可以注意到PCIE其实本质还是占用高速串行口,查看器件资源我们可以看到GTX 这类接口是一定会大于PCIE硬核数目的,此外硬核支持的速率受器件限制死了,比如K7系列的器件,最高支持的是P

易灵思的Riscv-Sapphire软核搭建及开发流程

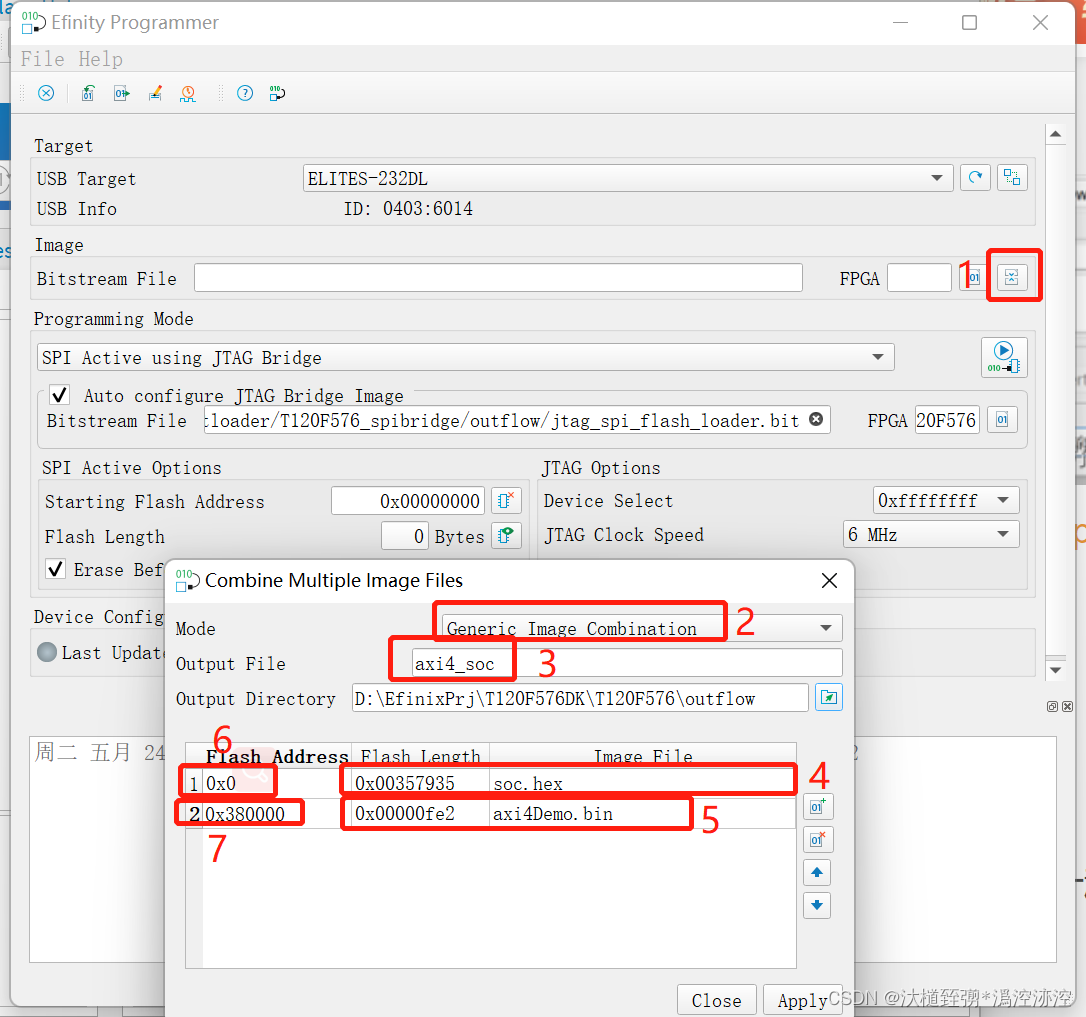

目录 一、首先生成Sapphire软核ip 二、创建Eclipse工程 三、配置Eclipse的编译环境 四、合并逻辑的hex和软核的bin的文件 一、首先生成Sapphire软核ip 通过软件Efinity的IP-Catalog功能生成Sapphire-riscv的IP核,我这里保持默认参数,如下图: 找到相应的目录,目录里的IP文件夹下会有生成的sapphire的目录